Парафазный сдвигающий регистр

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<» 739654

Союз Советскик

Социалистических

Республик (51)М. Кл.

6 11 С 19/00

/

/ г с р (61) Дополнительное к авт. свид-ву (22)Заявлено 09.01.76 (21) 2311472/18 24

Гесударяввввй квинтет

w втк11мтв1 с присоединением заявки № (53) УДК 628.327..6 (088.8) (23) Приоритет

Опубликовано 05.06.80. Бюллетень ¹ 21

Дата опубликования описания 09.06.80

В. И. Редченко и В. В. Малый (72). Авторы изобретения (71) Заявитель (54) ПАРАФАЗНЫЙ СЛВИГАЮЩИЙ РЕГИСТР, 1

Изобретение предназначено дпя исполь-! зования в счетно-решающих устройствах, устройствах автоматики и информационноизмерительной техники, а также в разлапых устройствах приема и передачи дискретных сообщений.

Известны парафазные сдвнгжнцие регистры, содержащие последовательно сое1птненные элементы намяти на триггерах с объединенными счетными входамн, K которым подключена шина сдвига Щ и (2 .

Однако э ви устройства сложны и ненадежны, что вызвано большим количеством элементов и сложной структурой схемы сдвига.

Наиболее близким к предложенному регистру по технической сущности явля. ется парафазнйй сдвигающий регистр, содержащий последовательно соединенные через элементы И-HE элементы памяти, на триггерах с.объединеннымй счетными входами. Выходы элементов И-НЕ в ука;занном устройстве соединены о единичными и нулевыми входами.соответствующих триггеров, а входы — с выходами триггеров, причем вторые входы элементов И -НЕ подключены к шине тактовых импульсов (Э)

Недостатки известного парафазного регистра заключаются в том, что он имеет большее число информационных входов, требует применения тактовых импульсов, а также специального устройства формирования этих импульсов с обязательной временной привязкой к диаграмме поступления входного парафазного кода.

Цепь изобретенйя - повышение надежности устройства и его быстродействия.

Это достигается тем, что в парафазный сдвигающий регистр, содержащий последовательно соединенные элементы памяти на триггерах с объединенными счетными входами и элементы И-НЕ, дополнительно введены элементы памяти на триггере, инверторы и элемент ИЛИ, выход которого соединен со счетными входами триггеров, а вхо1ня - с выходами одних элементов

И-НЕ, первые входы которых соответствен7396 ио соединены с нулевым и единичным выходами триггера дополнительного элемента памяти, вторые входы элементов И-НЕ подключены к выходам инверторов, входы которых подключены к нулевому и единичному входам триггера дополнительного

5 элемента памяти и соответствующим выхо .дам. других элементов И-НЕ, при этом ну- левой выход триггера дополнительного элемента является информационным входом .сдвигающего регистра.

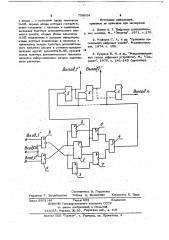

На чертеже представлена функциональ ная схема парафазного сдвигающего ре-. гистра..

Парафазный сдвигающий регистр содер- 15 жит дополнительный элемент 1 памяти на триггере; инверторы 2 и 3, элемент ИЛИ

4, последовательно соединенные, элементы

5 памяти на триггерах с объединенными счетными входами и элементы И-НЕ 6,7, 8,9. Единичный и нулевой входы дополнительного элемента 1 памяти на триггере соответственно через инверторы 2 и 3, одни из элементов И-НЕ 6,7 и элемент

ИЛИ соединены со счетными входами триг-25 геров элементов 5 памяти и с выходами соответствующих других элементов И-HE 8,9. Вторые входы одних элементов И-HE

6.,7 подключены к нулевому и единичному выходам триггера, дополнительного элемента 1 памяти, а нулевой выход этого триггера — к информационнОму входу сдвигающего регистра.

Парафазный сдвигающий регистр работает следующим образом.

При поступлении импульсов парафазного кода йа единичный вход 1" или нулевой вход О и вход сопровождающих импульсов (вход "СИ ) открывается соответствующий элемент И-НЕ 8 или 9 и до- 4 полнительный элемент 1 памяти на триггере установится в соответствукицее положение 0 или "1". Например, при поступлении импульса йа вхдд "1" и сопровождающего импульса на вход СИ триггер 45 дополнительного элемента 1. памяти уст новится в положение 1". В этом случае на информационный вход сдвигающего ре- . гистра будет поступать соответствующий уровень с нулевого плеча названного триггера. После установки триггера дополнительного элемента 1 памяти в сс стояние "1 разрешается прохождение сигнала через элемент И-HE 7, на второй вход которого через инвертор 3 по-. ступает сигнал с единичного входа триггера. В этом случае элемент И-НЕ 7 формирует на своем выходе сигнал, который, поступая на объединенные счет54 а ные входы триггеров последовательно со-, единенных элементов 5 памяти, запишет информацию с информационного входа на первый триггер элемента 5 памяти. Сдвигающий сигнал на выходе элемента ИЛИ

4.возникает только после установки тригgapa дополнительного элемента 1 памяти в состояние "1 и записи этой информации в первый элемент 5 памяти. Это, а также то, что сдвиг информации происходит задним фронтом инпульса, совершенно исключает влияние разбросов временных характеристик элементов схемы на ее нормальную работу.

Аналогично при поступлении нулевого значения парафазного кода на вход "0" и сопровождающего синхроимпульса на вход

СИ" триггер дополнительного элемента 1 памяти через элемент И-НЕ 9 установит ся в состояние "О, и на информационной шине установится соответствующий уровень

Как и в первом случае только после установки триггера дополнительного элемента 1 памяти в состояние "0" при помощи инвертора на выходе элемента И-НЕ 6 будет,формироваться сигнал, который через элемент ИЛИ 4 запишет нулевую информацию в первый элемент 5 памяти, сдвинув прежде записанную в нем информацию во второй разряд (элемент 5 памяти) регистра.

Далее работа устройства происходи г аналогично описанному до полного заполнения всех последовательно соединенных элементов 5 памяти.

Запоминание информации на триггере дополнительного -элемента 1 памяти позволяет при малых длительностях входных сигналов значительно повысить быстродействие и .надежность схемы, а совместное включение этого триггера с инверторами 2,3, элементами И-НЕ 6,7 и ИЛИ

4 позволяет принять парафазный код на обычный однофазный сдвигающий регистр.

Входные элементы И-НЕ 8,9 в совокупности с указанными элементами осуществляют зонту устройства от помех, возникающих во входных линиях связи формула изобретения

Парафазный сдвигающий регистр, содержащий последовательно соединенные эле» . менты памяти на триггерах с объединенными счетными входами и элементы И НЕ,, отличающийся тем, что, с целью йовышения надежности устройства и его быстродействия, он содержит дополнительный элемент памяти на триггере, ин верторы и элемент ИЛИ, выход которого ссединен со счетными входами триггеров, а входы с выходами одних элементов

И-НЕ, первые входы которых соответственно соединены с нулевым и единичным выходами триггера дополнительного we- . мента памяти, вторые вХоды элементов .И-НЕ подключены к выходам инверторов, входы которых подключены к нулевому и единичному входам триггера дополнительного элемента памяти и соответствующим выходам других элементов И-НЕ, нулевой выход триггера дополнительного элемента является информационным входом сдвигающего регистра.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г. Бифровые вычислительные машины, М., Энергии,-1971, с.176.

2. Майоров С. А., и др. Принципы организапии цифровых машин .. Машиностроение, 1974, с. 128, е

3. Букреев И. Н. и др. "Микроэлектронные схемы цифровых устройств . М., Сов. радио, 1975, с. 141-143 (прототип).

Составитель В. Гордонова

Редактор Т. Загребельная Техред A. Кепанская Корректор Е. Папп

Заказ 2951/48 . Тираж 662 Подписное

UHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент, r. Ужгород, ул. Проектная, 4