Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 739658

ИЗОБРЕТЕНИЯ, Сонзэ Советских

Социалистических

Республик катиа вц „, ?., 1 T 6 (51)М. Кл. (я 11 С 29/00

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 01.11.77 (21) 2539868/18-24 с присоединением заявки МйзвудврвтввииыН квинтет

СССР . аю делен изебретеннй и открытий (23)ПриоритетОпубликовано OS,06,80. Бюллетень %21 (5Q) УДК 681.З17 (088.8) Дата опубликования описания 09.06.80 (72) Автор. изобретения

В. С. Шевченко (71) Заявитель (543 УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

3 Изобретение относится к области ЗУ.

Известно устройство для контроля памяти 11) „содержащее для задания nocaegoaamaszocrm выбираемых адресов, видов операций, хранения и обработки результатов БВМ. Оно обладает недостаточо ным быстродействием при контроле оперативных блоков памяти.с малым временем обращения.

Из известных устройств наиболее близ- ким техническим решением к изобретению является устройство для контроля памяти, . содержащее блок формирования тестов, выходы которого подключены к одним входам блока формирования импульсов записи, и чтения, регистра числа и блока сравнения, . другие входы, „которых соединены соответственно с выходом блока местного управления, входом устройства и выходом регистра числа, регистр адреса и блок ynpaanemas .$2)

В этом устройстве можно реализовать лишь тесты для проверки блоков памзтгй, имеющие в алгоритме построения после2

|довательное обращение по адресам проверяемого блока. Реализовать же проверяющие тесты определяющие сохранность информации по данному адресу.при обревцении к другим адресам, . невозможно.

Это существенно сужает область применения устройства, в частности не позволяет эффективно использовать его для к онтроля оперативной: полупроводниковой памяти.

Белью изобретения является расширение области применения устройства за счет обеспечения йвеможности контроля полупроводниковой оперативной памяти.

Поставленная цель достигается тем,,что предложенное устройство содержит дополнительный регистр адреса, триггер и коммутатор, выход которого соединен с выходом устройства, а входы подключены соответственно к выходам триггера и ре е гистров адреса. Входы триггера и дополнительного регистра адреса соединены с выходами блока управления.

3 7396

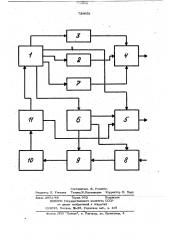

На чертеже изображена структурная схема предложенного устройства.

Устройство содержит блок управления

1, регистр адреса 2, триггер 3, коммутатор 4, блок формирования импульсов

5 записи и чтения 5, блок формирования тестов 6, дополнительный регистр адреса 7, регистр числа 8, блок сравнения 9, блок останова 10 и блок местного управления 11..

Выход коммутатора 4 соединен с выходом устройства, а входы подключены comветственно к выходам триггера 3 и реги- стров 2 и 7. Входы триггера 3 и регистра 7 соединены с выходами блока 1.

Работу устройства рассмотрим на примере контроля полупроводникового блока памяти тестом, типа Галоп". Данный тест предполагает первоначальную запись, по > -му адресу "1" (> =1,2,3 ... N ) и 0" по всем остальным i =1 адресам.

° - 20

@алыче тест предполагает поочередное считывание и контроль записанной информации по j =му адресу (,) =1,2,3 ... И и i4 ) ) и по постоянному ) -му

25 адресу с увеличейием на 1. -ro адреса при переборе всех j -х адресов. Достигается. это следующим образом. По сигналам из блока управления 1 адресный регистр 2 устанавливается в состояние

30 -го адреса, триггер 3 устанавливает коммутатор 4 в такое состояние, по кото - рому сигналы адреса регистра 2 проходят через коммутатор 4 на выход. устройства.

Блок формирования импульсов записи и чтения 5 по сигналам из блока формирования

15 тестов 6 и блока управления 1 выдает на выход устройства сигнал чтения "1». Чте:ние "1", таким образом, производится по

} -му адресу проверяемого;блока- памя40

Регистр 7 устанавливается в состояние 1-го адреса и триггер 3 перебрасывается в другое состояние, подключая вы 45 ходу регистра 7. Блок формирования им пульсов записи и чтения 5 подает по

1 ,) -му адресу на выход устройства сигнал чтения 0".

Сигналом из блока управления 1 триттер.

3 снова перебрасывается, подключая выход устройства через коммутатор 4 к выходу регистра 2, который вновь выбирает

-ый адрес, по. которому производится чтение 1 . Сигналом из блока управле55 ния 1 регистр 7 устанавливается в состояние (j +1) го адреса. Коммутатор 4 ,иод управлением триггера 3 подключает к выходу. устройства выходы регистра 7 и

58 по выбранному (j +1)-му адресу производится чтение "0" .. Дальше роизводятся аналогичные коммутации триггером 3 через коммутaTop 4 выходов регистров 2 и 7 при переборе регистром 7 остальных (N — 3) адресов, причем после перебора всех адресов регистром 7 регистр 2 устанавливается в следующем (+1)-е состояние и производятся аналогичные коммутации. Считанные из проверяемого блока памяти сигналы подаются на регистр 8, а оттуда на блок сравнения 9, который в случае несовпадения считанной и записанной информации выдает на блок останова 10 сигнал, по которому прекращается работа блока 11 и работа все го устройства.

Использование дополнительного адрес. ного регистра, триггера и коммутатора выгодно отличает описанное устройство прототипа. Для расширения области применения прототипа необходимо применение либо специализированной вычислительной машины для задания необходимой последовательности адресов, специального процессора, что менее аффективно, чем применение дополнительного адресного регистра, коммутатора и триггера.

Формул а изобретения

Устройство для контроля памяти, содержащее блок формирования тестов, выходы которого подключены к одним вхо дам блока формирования импульсов записи и чтения, регистра числа и блока сравнения, другие входы которых соединены со"г ответственно с выходом блока местного управления, входом устройства и выходом регистра числа, регистр адреса и блок управления, о т л и ч а.ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности контроля полупроводниковой оперативной памяти, оно содержит дополнительный регистр адреса, триггер и коммутатор, выход которого соединен с выходом устройства, а входы подключены соответственно к выходам триггера и регистров адреса, входы триггера и дополнительного регистра адреса соединены с"выходами блока управления.

Источники информации, принятые во .внимание при. экспертизе

1. Электроника, N. 18, 1969, с. 25 24.

Информ аци онны и лис т ВИ М И, М

1464 (прототип).

7S9658

Составитель .В. Рудаков;

Редактор Л. Утехина Техред Ж. Кастелевич Корректор Е. Папи

Заказ 2951/48 Тираж 662 Подписное

UHHHfIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/6

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4