Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП И

ИЗОБРЕТЕНИЯ

Союз Советскмк

Соцнапксткческнн

Республик

< >739659

К. АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свил-ву— (22) Заявлено 18.01,78 (21) 2571643/18-24 (5 I ) M. Кл, G 11 С 29/00 с прнспелинением заявки Ж

Гасударственный комитет

СССР вв йевам изееретений н открытий (23) П рнорнтет— (53) УДК 628.Э27..6 (088.8) Опублнкованв05.06.80. Бюллетень М 21

Дата опубликования описания 09,06.80 (72) Авторы изобретения

A. В, Тимашев, В, И. Антошкин и A. A. Борттскин

Особое конструкторское бюро вычислитепьной техники

Рязанского радиотехнического института (71) Заявитель (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам и может быть использовано в вычислительной технике.

Известны запоминающие устройства, содержащие регистр адреса, дешифратор адреса, наконитепь, информационные ре% гистры, блок контроля, которые производят контроль записываемой и считываемой информации и выдают сигнал ошибки в слу чае несоответствия информационных и

10 контрольных разрядов 3Q и (2)

Наиболее близким техническим решением к предлагаемому явпяется устройство, содержащее регистр адреса, подключенный к дешифратору адреса, выходы которого соединены с адресными входами блока запоминающих матриц, регистр слова, блок усилителей считывания-записи, бпок контроля и управляющие шины. В нем осуществляется контроль адреса и слова с помощью блока контроля на соответствие информационных и контрольных разрядов и восстановление информации в случае сбоя ! в адресном тракте (3j

Недостатком данного устройства является то, что в нем разрешается зались и .считывание информации нэ любой ячейки.

Однако существуют вычислительные системы„в которых массивы для нескольких процессоров располагаются в одной и той же зоне оперативного запоминающего устройс тва.

В данной зоне расположены массивы, данные из которых могут считываться несколькими процессорами, кроме того существуют такие массивы, данные из которых могут быть считаны только одним иэ процессоров, на котором обычно реализуется операционная система. Поатому дпя нормальной работы вычиспитепьной системы очень важно предотвратить запись данных в массивы, из которых допускается только считывание, а также считывание данных из массивов, к которым доступ данного процессора не разрешен.

Следовательно, функциональные возмож ности известного устройства не позвопяют

3 7396

"испольэовать его при построении вычислительных систем определенного класса.

Белью изобретения является расширение области применения устройства.

Поставленная цель достит ается тем, что, в оперативном запоминающем устройстве, содержащем регистры адреса .и слова, соединенные сосл ветственно через дешифратор и блок усилителей записи-считывании с запоминающим модулем, первые входы 10 регистра слова подключены к соответствующим входным шинам, блок контроля и управляющие шины, введены элементы НЕ, И, ИЛИ и дополнительный регистр слова, первые входы которого соединены с соот- 15 ветствующими выходами блока усилителей записи-считывания, вторые — с одними из выходов регистра слова, другие выходы которого подключены непосредственно и

Через элементы HE к первым входам со- 20 ответствующих элементов И, вторые входы которых подключены к соответствующим управляющим шинам, выходы элементов И через элементы ИЛИ соедийены со вторыми входами дополнительного регистра сло- 25 ва, выходы которого подключены ко вторым входам регистра слова и входам блока контроля.

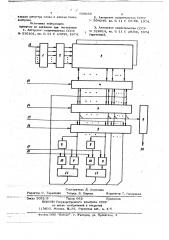

На чертеже представлена функциональ . ная блок-схема оперативного запоминаю- З0 щего устройства.

Устройство содержит регистр 1 адреса, дешифратор 2, запоминающий модуль 3, блок 4 усилителей записи считывания, ðå- 35 гистр 5 слова, блок контроля 6, дополнительный регистр. 7 слова, элементы 8 НЕ, элементы 9 И. (первые), элементы 10 И (вторые), элементы 11 ИЛИ.

Оперативное запоминающее устройство цодключаечся к другим устройствам с по мацью следующих управлякнцих шин: входных шин 12 адреса, шины 13 сигнала, управляющего переключением входов блока

4 усилителей считывания-записи в зависимости от режима работы устройства, шины 14 сигнала, управипощего переключением входов и выходов дополнительного регистра 7 слова в зависимости от режимов работы устройства, входных шин 15

50 слова, шины 16 сигнала, управляющего переключением входов регистра 5 слова и зависимости от режима работы устройства, шины 17 сигнала, подключенную к уп55 равляющим входам первых схем 9 И, шины 18 сигнала, подключенную к управляющим входам вторых схем 10 И, шины

19 сигнала ошибки.

59 4.

Регистр 1 адреса подключен к дешифратору 2 адреса, выходы которого соединены с адресными входами блока 3 эап минающих матриц, блок 4 усилителей считывания-записи подключен к блоку 3 запоминающих матриц. Выход каждого из информационных разрядов (одни из выходов) регистра 5 слова соединен с соответствующим входом блока 4 усилителей считывания-записи и вторым входом соответствующего разряда дополнительного регистра 7 слова, первый вход каждого иэ разрядов которого соединен с соответствующим выходом блока 4 усилителей считывания-записи. Выход каждого иэ разрядов дополнительного регистра 7 слова соединен соответствующим входом блока 6 контроля и вторым входом соответствующего разряда регистра 5 слова, первый вход которого подключен к входной шине

15 слова. Выход каждого из контрольных разрядов,(другие входы) регистра 5 слова соединен с информационным (первым) входом первого элемента 9 И и входом элемента 8 НЕ, выход которого соединен с информационным (первым) входом второго элемента 10 И, выходы элементов 9

И и 10 соединены со входами элементов

11 ИЛИ, выходы которых подключены к соответствующему входу блока 4 усилителей считывания-записи и второму входу соответствующего разряда дополнительного регистра 7 слова. Управляющие входы .всех элементов 9 И объединены между собой и подключены к управляющей шине

17, управляющие входы всех элементов

10 И объединены между собой и подклю- ° чены к управляющей шине 18.—

Устройство работает в следующих режимах: запись, запись с инверсией контрольных разрядов, запись с проверкой, счи1 ывание, считывание с инверсией контрольных разрядов. В режимах запись, запись с инверсией контрольных кодов и. запись с проверкой, адрес ячейки, находящейся на входных шинах адреса 12, и записываемое слово, находящееся на входных шинах 15 слова фиксируются соответственно, на регистре 1 адреса и регистре 5 слева. Затем с помощью сигналов на управляющих шинах 14 и 18 осуществляется перепись слова (контрольные разряды не инвертируются) с регистра 5 слова на дополнительный регистр 7 слова и подключение его выходов к блоку 6 контроля. Появление на шине

19 сигнала свидетельствует об ошибке в принятой информации и запись информации

9 6

6 контроля. Отсутствие сигналов ошибки на шине 19 свядетельствует о нормаиьной работе устройства.

Таким образом устройство выдает car нал ошибки: при сбое входной информации, прн попытке записи данных в режиме запись с проверкой в ячейки, в которые дан ные при начальной загруз се бьщи записаны в режиме запись с инверсией контрольных разрядов; при попытке считывания .данных в режиме считывания иэ ячеек, в которые данные при начальной загрузке быпи записаны в режиме запись,о инверсией контрольных разрядов; при

;сбое информации внутри устройствае

Анализ сигналов ошибки позволяет предотвратить последствия, которые могут возникнуть иэ-за нес анкционярованных обращений к массивам. Следовательно рюширение области применения предлагаемого устройства делает возможным использование оперативного запоминающего устройства при построении высоконадежных мультипроцессорных вычислительных систем, работающих с общим поаем памяти. формула изоápетения

Оперативное запоминающее устройство, содержащее регистры адреса и слова, соединенные соответственно через дешяфратор и блок усилителей записи-считывания с запоминающим модулем, первые входы регистра слова подключены к соответст» вукицим входным шинам, блок контроля и управляющие шины, о т л и ч а ю щ ее с я тем, что, с целью ржшярения области применения устройства эа счет одновременной обработки неоднородного массива данных с инверсией контрольных разрядов, оно содержит элементы НЕ, И, ИЛИ и дополнительный регистр слова, первые входы которого соединены с соответствующ.имя выходами блока усилителей записисчитывания, вторые — с одними из выходов регистра слова, другие выходы которого подключены непосредственно и через элементы НЕ к первым входам соответсъ вующих элементов И, вторые входы которых подключены к соответствующим управляющим шинам, выходы элементов И через элементы ИЛИ соепкнены со вторыми входами дополнятельного регистра слова, выходы которого подключены ко вторым

5 73965

s ячейку не производится. При отсутствии сигнала ошибки и работе устройства в режиме запись с помощью сигналов на шинах 18 (контрольные разряды не инвертируются) 13 и 14 осуществляется подключение слова с регистра 5 слова к блоку 4 усилителей считывания-запись и. запись слова в ячейку памяти в соответ) ствии с адресом, хранимым на регистре

1 адреса. Режим запись с инверсией конт-10 рольных кодов отличается от режима запись тем, что управлякщий сигнал появляется не на шине 18, а на шине 17,, вследствие чего значение контрольного разряда инвертяруется с помощью элементов 8 НЕ. В этом случае в ячейку записывается слово с инвертированными контрольными разрядами.При работе устройства в режиме запись с проверкой после контроля эаписй. ваемого слова в случае отсутствия сигна- 20 па ошибки происходит предварительное считывание слова, хранимого по адресу, зафиксированному на регистре 1 адреса. С помощью сигналов на шянах 13 и.14 производятся запись считанного cross на до олнитецьный регистр 7 слова и подключение его выходов к блоку 6 «онтроля.

Если в этом случае на шине 19 не появляется сигнал ошибки, то с помощью сигналов на шинах 18 (контрольные разряды 3О ие инвертируются) 13 и 14 осуществляет« ся подключение слова с.регистра 5 слова к блоку 4 усилителей записи-считывания и запись слова в ячейку и соответствяи с адресом, хранимым на регистре 1 адре- 55 са. При работе устройства в режиме сч ьтывания с помощью сигналов на шинах 13 и 14 происходят считывание слова иэ, ячейки в соответствии с адресом, хранимым на регистре 1 адреса, запись этого слова 4О на дополнительный регистр 7 слова, подключение выходов дополнительного регист- ра 7 слова к блоку 6 контроля, появление сигнала ошибки на выходе 19 свидетель ствует о несоответствия информационных 45 и контрольных разрядов. При работе устройства в режиме считывания с инверсией контрольных разрядов также происходит считывание слова и запись его на дополнительный регистр 7 слова, но беэ подключения его выходом к блоку 6 контроля. Вместо этого с помощью сигналов на шине 16 происходит перепись слова с дополнительного регистра 7 слова на регистр

5 слова. Затем с помощью сигналов на шинах 17 и 14 происходит инверсяя контрольных разрядов, а запись модифицирован=-ного слова на дополнительный регистр 7 слова и подключение его выходов к блоку

i . г

7 739659 8 а адам регистра слова и входам блока 2. Авторское свидетельство СССР контроля. 504249, кл. (з 11 С 29/00, 1974

Источники информации, лрйиитые во внимание прн экспертизе 3. Авторское свидетельство „C(;p

1. Авторско свидетельство СССР 5 №,528614, -кл. С 11 С 29/00, 1974 № 516101, кл. G 11 С 2Э/00, 1974. {прототип).

Составитель Л. Лмусьева

Редактор С. Тарененко Техред Я. Бирчак Корректор Т. Сквордова

Заказ 3052! 9 Тираж 662 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фллйал ППП "Патент", г. Ужгород, ул. Проектная, 4