Транзисторный инвертор

Иллюстрации

Показать всеРеферат

«ii739699

Союз Советских

Социалистических республик

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. саид-ву— (22) Заявлено 10.10.77(21) 2531026/24-07 с присоединением заявки K

Н 02 М 7/537

Ьаударатааааь 3 каинтат

CCC$ йо делам ааабратаниа и етхрытий (23)Приоритет(53) УДК, 621.314..572(088.8) Опубликовано 05 06.80. Бюллетень ¹ 21

Дата опубликования описания 05.06.80 (72) Автори изобретения

В. С. Моин (7!) Заявитель (54) ТРАНЗИСТОРНЫЙ ИНВЕРТОР

Поставленная цель достигается тем, что в транзисторном инверторе, содержаt5 щем полумосты с 8 последовательно соединенными в каждом плече основными транзисторами и диоды, подключающие точки соединения транзисторов между со20 бой к входным выводам инвертора, предназначенным для подключения секций источника питания, количество указанных выводов принято равным Й + 1, указанные диоды;соединены в Й - 1 цепочек, 1

Изобретение относится к преобразовательной технике и может быть использовано в системах электропитания и электропривода для преобразования постоянного напряжения повышенного уровня в переменное напряжение.

Известны транзисторные инверторы, в которых, с целью повышения допустимой величины входного напряжения в каждом плече, включено несколько соединенных последовательно транзисторов. Для обеспечения равномерного распределения нанряжения межщ транзисторами применяются уравнительные резисторы (1) или уравнительные обмотки трансформатора (а}.

Однако это приводит к усложнению схемы и к снижению ее КПД. и

Известен также транзисторный инвертор, содержащий несколько входных выводов для подключения нескольких секций источника питания н диоды, соединяющие эти выводы с точками соединения транзисторов в каждом плече мостовой схе2 мы инвертора. При этом, помймо обеспечения распределения напряжения между транзисторами плеча, появляется возможность формирования ступенчатого аппроксимирующего синусоиду выходного напряжения инвертора 13).

Недостатком этого инвертора являет, ся большое количество секций источника

° питания и невозможность работы на активно-индуктивную нагрузку. то

Цель изобретения — упрощение устройства.

7396

10 состоящих из двух согласно-последовательно соединенных диодов, крайние выводы цепочек подключены между точками соединения

-го и (n + 1)-ro транзистора смежных плеч полумоста, а средний вывод этой цепочки подключен к входному выводу, предназначенному для соединения и -ой и (n + 1)-ой секции источника питания.

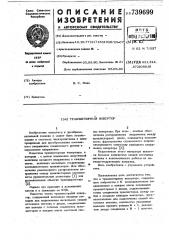

Для улучшения выравнивания напряже ния на транзисторах встречно-параллельно диодам включаются дополнительные транзисторы. . На фиг. 1 показан вариант предлагаемой мостовой схемы при N = 3> на фиг. 2 — вариант полумостовой схемы при

4; на фиг. 3 — диаграммы коммутации транзисторов.

Инвертор (фиг. 1) содержит транзисторы 1-12, включенные по мостовой схеме с тремя последовательно соединенными транзисторами в каждом плече. Вь|ход моста соединен с нагрузкой 13, а вход моста подключен к источнику питания, состоящему из "рех секций с напряжениями О, 0, 0 З . Секции источника 25 питания подключены к входным выводам

14-17 инвертора. Между точкой соединения первого и второго транзистора (1 и 2} верхнего плеча полумоста и точкой соединения первого и второго транзистора (4 и 5) нижнего плеча этого полумоста включена первая цепочка иэ согласно-последовательно соединенных диодов 18 и 19.

Между точкой соединения второго и третьего транзистора (2 и 3) верхнего плеча полумоста и точкой соединения второго и третьего транзистора (5 и 6) нижнего плеча полумоста включена вторая цепочка из согласно-последовательно соединенных диодов 20 и 21. Аналогично включены це-g0 почки диодов 22 и 23, 24 и 25вдругом полумосте инвертора. Средний вывод первой цепочки диодов каждого полумоста подключен к входному выводу 15, предназначенному для соединения первой и вт<И5 рой секции источника питания, а средний вывод второй цепочки диодов каждого полумоста подключен к входному выводу

16, предназначенному для соединения второй и третьей секции источника питания. 50

При увеличении числа транзисторов в плече соответственно увеличивается чйсло цепочек диодов и число секций источника

55 питания, а соединения между ними производятся аналогично описанному.

Устройство работает. следующим об- разом.

"Ъ

99 4В один полупериод, например, открываютются транзисторы 1-3, 10-12, а в

Ф другой 4-9. Напряжения, приложенные к закрытым транзисторам, фиксируются с помощью диодов на уровне напряжений секций источника.

Например, при открытых транзисторах 1-3 напряжение на транзисторе 6 не может быть больше, чем 0, так как открывается диод 21, а напряжение на транзисторах 6 и 5 не может быть больше 0 + Оз, так как. открывается диод 19. Если u„= U - Оз и необходимо выровнять напряжение на всех транзисторах плеча, то для того, чтобы на транзисторе 5 не было перенапряжения . при токе утечки транзистора 6, большем чем транзистора 5 или 4, необходимо включить резистор 26, обеспечивающий прохождение тока несколько большего, чем разность между токами утечки транзисторов 6 и 5 (или 4). Из аналогичных соображений выбирается резистор

27. В отличие от схемы с. обычными выравнивающими резйсторами, через которые необходимо пропустить ток, на порядок превышающий максимальный ток утечкитранзистора, в предлагаемой схеме через транзистор достаточно пропустить ток, равный максимальному току утечки транзистора, т. е. мощность, рассеиваемая в резисторах, уменьшается в 5-10 раз.

Кроме того, резко уменьшается количество резисторов (в инверторе по фиг. 1— втрое).

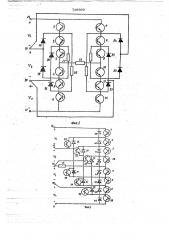

Для обеспечения выравнивания напряжения на транзисторах без использования резисторов предлагается схема инвертора по фиг. 2. Инвертор для примера выполнен по полумостовой схеме с четырь мя последовательно соединенными транзисторами в каждом плече (1-3, 28 и

4-6, 29). Точки соединения транзисторов подключены к входным выходам 15, 16 и 30 инвертора с помощью диодов 18-21, 31 и 32, соединенныхв трицепочки по схеме, описанной в инверторе по фиг. 1.

Встречно-параллельно каждому диоду включены дополнительные транзисторы

33-38. Инвертор (фиг. 2) работает ана логично инвертору по фиг. 1. Однако для лучшего выравнивания напряжения между транзисторами одновременно с основными транзисторами одйого плеча полумоста (например, 1-3 и 28) открываются дополнительные транзисторы, соединенные с основными транзисторами (4-6 и 29) другого плеча полумоста.

5 7396

При этом напряжение, приложенное к транзистору 29, всегда равно 0, к транзистору 6 — U>, транзистору 5 -U>, транзистору 4 — U так как дополнительный транзистор с диодом образует ключ с двусторонней проводимостью, подключающий основной транзистор к секции источника питания.

Если дополнительные транзисторы обеспечивают только функции выравнивания напряжения, они рассчитываются на весьма малый ток. Если же необходимо выполнение инвертора со ступенчатой формой выходного напряжения, работающего на активно-индуктивную нагрузку, то некоторые из дополнительных транзисторов должны быть рассчитаны на тот же ток, что и основные транзисторы. Например, если применить транзисторы 35 и 36, такие же как основные транзисто- zg ры и обеспечить алгоритм коммутации транзисторов, показанный на фиг. 3, то выходное напряжение инвертора имеет двухступенчатую форму аппроксимирующую синусоиду, а напряжение на каждом из транзисторов не превышает напряжения одной .из секций источника питания, т. е. в четыре раза меньше полного напряжения источника питания (между выводами 14 и 17). Если задача выравни- ЗО вания напряжения отсутствует, а необходимо улучшить форму выходного напряжения, то выбирая соотношение между напряжениями U . U .ОЗ:U,как 1:2:4:8, можно получить 16-ти ступенчатую кривую выходного напряжения.

Диоды 39-46 обеспечивают работу инвертора на активно-индуктивную нагрузку.

99 6

Формула изобретения

Транзисторный инвертор, содержащий полумосты с М последовательно соединенными в каждом плече основными транзисторами и диоды, через которые точки соединения основных транзисторов между собой подключены к входным выводам инвертора, предназначенным для подключения секций источника питания, о т л ич а ю шийся тем, что, с целью упрощения, количество указанных выводов равно N + 1, указанные диоды соединены в N — 1 цепочек, в каждой из которых включено согласно-последовательно два диода, крайние выводы каждой цепочки включены между точкой соединения

-го и (n + 1)-го (где n = 1, 2, 3, ...), транзисторов одного плеча и аналогичной точкой соединения транзисторов другого плеча полумоста, причем направление проводимости диодов противоположно направлению проводимости транзисторов, а средний вывод упомянутой цепочки подключен к входному выводу, предназначенному для соединения г1 -ой и (O + 1)-ой секции источника питания.

2. Иивертор по п. l, о т л и ч а к шийся тем, что встречно-параллельно указанным диодам включены дополнительные транзисторы.

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ № 1244941, кл. 21 0 12/03, 1965.

2. Авторское свидетельство СССР

M 311314, кл. Н 02 М 1/18, 1970.

3. Патент США № 3227889, кл. 307-81, 1966.

739699 к

Сос авитель Б, Каржавов редактор С, Терененко Текрен Ж. Кеотеневвч Корректор Т. кворнове

Заказ 3054/S Тираж 783 Подписное

ЫНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., p. 4/5

Филиал ППП Патент", r. Ужгород, ул. ПроеКтная, 4