Приемное устройство для локомотивной сигнализации

Иллюстрации

Показать всеРеферат

. тr бнблнот а sn

Союз Советские

Социалистические

Республик () 740583

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополннтельное к нвт. свнд-ву (22) Заявлено 29.12.77 (2 t ) 2561570/27-11

2 (5! )M. Кл.

В 61 1 25/06 с присоединением заявки ¹

Государственный комитет (23) ПрнорнтетОпубликовано 15.06.80. Бюллетень ¹ 22 (53) УДК621.385. .3 97 (088.8 ) во делам иэооретеннй и открытий

Дата опубликования описания 18.06.80 (72) А вторы изобретения

A. E. Пыров, Б. Д. Никифоров и В. Ф. Амосов

Проектно-конструкторское бюро Главного управления локомотивного хозяйства Министерства путей сообщения

СССР (7!) Заявитель (54) ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ЛОКОМОТИВПОЙ

СИГНАЛИЗАЦИИ

Изобретение относится к железнодорожной автоматике и, в частности, к устройствам локомотивной сигнализации.

Известно приемное устройство для локомотивной сигнализации, содержащее

5 приемный блок, интегратор принимаемого сигнала, генератор, соединенный с блоком отсчета импульсов, а также с интеграторами эталонного сигнала и коррекции, выходы которых подключены к блокам коррекции о длительности интервала, коррекции входного сигнала и сравнивания, выход которого соединен с исполнительным блоком $15

Недостатком известного устройства является недостаточная помехозащищенность от импульсных помех и сигналов с измененными временными параметрами.

Иель изобретения - повышение надежности приема кодовых сигналов и защиты от импульсных помех.

Для этого приемное устройство снабжено управляющим сумматором, один и другой входы которого соединены с приемным блоком, одним блоком ИЛИ, вход которого подсоединен к блоку коррекции входного сигнала, а выход — к блоку отсчета импульсов, и другим блоком ИЛИ, блоком дополнительного сравнения, интет ратором дополнительной коррекции интервала и блоком памяти сигнала, один вход которого соединен с блоком сравнения, другой вход — с блоком коррекции длительности интервала и другим блоком

ИЛИ, а выход подключен к исполнитель ному блоку, выход сумматора соединен с одним блоком ИЛИ, а один из входов подключен к блоку дополнительного сравн ния, выход которого соединен с другим блоком ИЛИ, а к одному из входов подключен интегратор коррекции и интегратор дополнительной коррекции интервала, выход которого соединен с другим блоком

ИЛИ, а один из входов подключен к интегратору коррекции и генератору, причем интегратор принимаемого сигнала соединен с входом приемного блока.

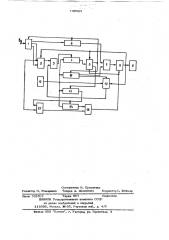

На чертеже представлена структурная схема устройства.

3 74

Приемное устройство для покомотивпой сигнализации содержит приемный блок 1, где выходы подключены к входам сумматора 2, выход которого через один элемент 3 ИЛИ по,гключен к одному из входов блока 4 отсчета импульсов, выход которого подключен к одному из входов блока 5 коррекции длительности интервала, один из выходов которого подсоединен к входу приемного блока 1 и входу интет ратора принимаемого сигнала 6, вход которого подключен к выходу приел4ного блока 1, а один из входов блока 5 коррекции длительности интервала подсоединен к входу сумматора 2, выход интегратора 6 принимаемого сигнала подключен к одному из входов блока 7 сравнения, который в

J) свою очередь, через блок 8 памяти сигнала подключен к исполнительному opr àну 9, при этом генератор 10 подсоединен соответственно ко входам интегратора 11 эталонного сигнала, блока 1 2 коррекции входного сигнала, интегратора 1 3 коррекции и интегратора 14 дополнительной кор- рекции интервала, при этом выход интегратора 13 коррекции соединен со входом интегратора 14 дополнительной коррекции и с одним из входов дополнительного блока 15 сравнения, выход которого через другой элемент 16 ИЛИ подключен ко входам стирания блока 8 памяти сигнала и блока 5 коррекции длительности интерв ала.

Устройство работает следуюгцим оора. зом.

0583 ф

При поступлении сигнала на вход приемного блока 1 сигнал с его выхода поступает на один из входов интегратора 6 принимаемого сигнала, где по досгижении заданного количества импульсов запоминается в блоке памяти. Сигналы с других выходов приемного блока 1 поступают на входы сумматора 2, где сигнал B этот момент отсутствовал и на его выходе формируются сигналы с периодом и скваж" ностью, эквивалентными сигналам выхода приемного блока 1. Эти сигналы посту пают через элемент 3 ИЛИ на вход блока 4 отсчета импульсов.

В момент появления сигнала на другом выходе приемного блока 1 начинает считать импульсы генератора 10 интегратор

11 эталонного сигнала и по достижении заданного количества импульсов, эквива» пентного интервалу времени, на котором оценивается непрерывность входного сит нала, сигнал запоминается в блоке памяти интегратора 1 1 эталонного, сигнала.

5 о а5

ЗО

Сигналы с выходов блоков памяти интеграторов 6 и 11 подаются на входы блока 7 сравнения и при условии, что.на входах блока 7 сравнения имеются одновременно оба сигнала, на его выходе формируется сигнал, который записывает информацию в блок 8 памяти сигнала.

Сигнал с выхода блока 8 памяти сиг» нала производит включение исполнительного органа, а также поступает на один из входов сумматора 2, вследствие чего на выходе последнего будет формироваться сигнал, эквивалентный суммарному сигналу на обоих выходах приемного блока 1, Кроме того, наличие информации запоминается в блоке 12 коррекции входного сигнала, в котором дается разрешение на прием сигнала с генератора 10 элеменга

3 ИЛИ и формирование данным элементом сигнала сброса, поступающего на блок 4 отсчета импульсов, независимо от того, есгь ли на выходе сумматора 2 сигнал или он отсутствует, затем поступает на дополнительный вход блока 5 коррекции длительности интервала.

При образовании интервала на выходах прием ного блока 1, более з ад анного„на выходе блока 4 отсчета импульсов сигнал появляется дважды через время t u t

4 2 при этом t 2 > t 4 . Во время интервала принимаемого кода, прп оценке сигнала на непрерывность сигнал на входе блока 5 отсутствует и последний формирует на своих выходах сигналы через время 4 . После записи информации в блок 8 памяти сигнала и появлении сигнала с его выхода на входе блока 5, последний препятствует прохождению сигнала с выхода блока 4 через время 3 и формирует юг» нап на своих выходах в момент време»г«2

Время коррекции входного сигнала определяется интегратором 1 1 эталонного сигнала, который после отсчета заданного количества импульсов генератора 10, эквивалентного времени коррекции, записывает информацию в свой блок памяти, с выхода которого сигнал поступает на один из входов и блоке 12 коррекции входного сигнала и с выхода последнего прекращается поступление сигналов генератора на вход элемента 3 ИЛИ, где в дальнейшем состояние элементов схемы будет опредепяться наличием сигнала на выходе сумм атора 2.

При образовании интервала на выходах приемного блока 1, более заданного, длительность которого задается блоком от счета импульсов 4. Ha et"o выходе образуется сигнал, он поступает на вход блока

5 коррекции длительности интервала и запоминается в нем, Сигнал с выхода блока 5 обеспечивает стирание информации и интеграторах 6 и 11, а также дальнейший ее прием. Этот же сигггал поступает на управляемый вход приемного блока 1 и восстанавливает чувствительность после него до минимально заданного уровня.

Одновременно сигнал с одного пз выходов блока 5 снимает запрет с интегратора 13 коррекции. Последний начинает считать импульсы генератора 10, и по достижении заданного количества импульсов на выходе интегратора 13 коррекции образуется сигнал, который снимает запрет с интегратора 14 дополнительной коррекции интервала и последний начинает счет импульсов генератора 1 О, а также сигнал с вькода интегратора 13 поступает на вход дополнительного блока 15 срам ения.

С этого ломента выклю- ение блока 8 памяти сигнала может быть осуществлено двумя способами.

Допустим, что через определеггное вре25 мя после образования сигнала на выходе интегратора 13 коррекции на другой вход дополнительного блока 1 5 сравнения поступил сигнал с выхода приемного блока 1, тогда на входах блока 15 одновременно появятся сигналы, в результате чего, на

ЗО его выходе формируется сигнал, который поступает на вход элемента 16 ИЛИ, Сиг нап с выхода элемента 16 ИЛИ стирает информацию в блоке 8 памяти сигнала, что приводит, в свою очередь, к выключе- З нию исполнительного блока 9 и к снятию сигнала с входов блоков 2 и 5, а также стирает информацию в блоке коррекции длительности интервала 5, что, в свою очередь, приводит к снятию запрета с ин- » теграторов 6 и 11 и к прекращению подачи сигнала с другого входа приемного блока 1, кроме того, происходит поступление сигнала на один из входов интегратора 13 коррекции. 4S

Исчезновение сигнала на выходе блока

13 приводит к разбору схемы совпадения дополнительного блока 15 сравнения и к стиранию информации в интеграторе

14 дополнительной коррекции 14, а так- so же к снятию запрета с блока 8 памяти сигнала. С этого момента устройство принимает свое первоначальное положение и готовится для приема новой информации, Осуществление дополнительной коррекции длительности интервала происходит следующим образом. Допустим, что после образования сигнала на выходе интегратора 13 коррекции на другой вход до8,З 6 полнительного блока 15 сравнения сигнал с выхода приел.ного блока 1 не поступает.

Б этом случае интегратор 14 дополнительной коррекции интервала считает импульсы генератора 10, по достижению заданного количества импульсов, эквивалентного интервалу времени дополнительной коррекции, сигнал запоминается в блоке памяти и на выходе интегратора

14 форлсируется сигнал, который поступает на вход элемента 16 ИЛИ, сигнал с выхода последнего произведет переключения в схеме, описанные выше.

Формула изобретения

Приемное устройство для локомотивной сигнализации, содержащее приемный

Fлок, иегтегр атор прин11маелюго сигнала, генератор, соединенный с блоком отсчета импульсов, а также с интеграторал и эт ало пгого си гн ал а и к оррекции, в ыходы которых подключены к блокам коррекции длительности интервала, коррекции входного сигнала и сравнения, выход которого соединен с испол>и тельным блоком, о т— ли чающее сятем, что, сцелью повышения надежности приема кодовых сигналов и защиты от HMIg льсных помех, оно снабжено сумматором, один и другой . входы которого соединены с приел ньгм блоком, одним блоком ИЛИ, вход которого подсоединен с блоку коррекции входного сигнала, а выход — к блоку отсчета импульсов, и другим блоком ИЛИ, блоком дополнительного сравнения, интегратором дополнительной коррекции 1пгтервалQ и блоком памяти сигнала, один вход которого соединен с блоком сравнения, другой вход — с блоком коррекции длительности интервала и другим блоком ИЛИ, а выход подкгпочен к исполнительному блоку, выход сумматора соединен с одним блоком

ИЛИ, а один из входов подключен к блоку дополнительного сравнения, выход которого соединен с другим блоком ИЛИ, а к одному из входов подключены интегратор коррекции и интегратор дополнительной коррекции интервала, выход которого соединен с другим блоком ИЛИ, а один из входов подключен к интегратору коррекции 1 генератору, причем интегратор принимаемого сигнала соединен со входом приемного блока.

И сто чники информ ации, принятые Во внимание прп экспертизе

1. Авторское свидетельство СССР

iлй 56 7222, кл. В 61 L 25i06, 197 6.

740583

Составитель И. Ермоленко

Редактор П, Макаревич Техред А. Шепанская Корректор С. Шекмар

Заказ 3285/2 Тираж 567 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий.

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4