Устройство для сопряжения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<11741259 (61) ???????????????????????????? ?? ??????. ????????-???? (22) ???????????????? 040178 (21) 2589511>

{51)м. к.2 с присоединением заявки №

G Об F 3/04

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 150680. Бюллетень ¹22

Дата опубликования описания 150680

{53) УДК684. 327. 21 (088. 8) (72) Авторы изобретения диденко, A.Ñ. Кандауров, К.Г. Карнаух, Ю.П. Кочур, Й.И. Кучерявый, В.Ф. Луценко и И.С. Шандрин (71) Заявитель

Специальное .конструкторское бюро систем автоматического управления (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано, например, для сопряжения ЦВМ .со стохастическими интеграторами при построении гибридных вычислительных систем.

Известны устройства для сопряжения, содержащие блок буферных регистров, соединенный входами с соответствующими входами устройства, распределитель опроса, блок управления, блок синхронизации и блок формирования адреса, и выполняющие функции управления организацией обмена между объектами и ЦВМ (1). 35

Недостаток этйх устройств состоит в ограниченных функциональных возможностях и низком быстродействии, поскольку выбор объекта производится последовательно вне зависимости от 20 его состояния.

Наиболее близким к технической сущности к изобретению является устройство сопряжения; содержащее буферный регистр, счетчик адреса, дешифратор адреса, регистр кода операции, регистр признака, дешифратор признака, счетчик данных, реверсивный преобразователь и блок управления, и выполняющее Функции сопряже- 30 ния ЦВМ с цифровым интегратором.

В устройстве вводу исходных данных в каждом функциональном направлении предшествует передача управляющего слова, по которому выполняется команда Управление, а затем передается информация (выполнение команды Записать ). Управляющее слово содержит код признака передаваемой информации, код признака адресной команды для ввода числа, код признака команды настройки запоминающего устройства, а также команды пуска или сброса. При выполнении команды Записать осуществляется передача на интегратор одного информационного слова или группы слов в функциональном направлении, заданном при выполнении команды Управление .

Вывод результатов решения задачи также осуществляется путем передачи от

ЦВМ управляющего слона, указывающего на Функциональный ацрес считываемой информации и непосредственной передачи результатов решения с интегратора на ЦВМ при выполнении команды Читать (2).

Недостатки этого устройстна заключаются в ограниченных функциональных воэможностях и низком быстродействии, 741259 обусловлен ых тег!, .т c, n.-."о:.! å по з воopT а ни з Q =iт ь ции от ЦВМ без и .. ;;:.,,." зияющего слона для каждого:,ун . ;ионального направления, не может -,ыдать информацию в ЦВМ беэ получения от нее команды выдачи, не позволяет сформировать KGJJ, состояния интеграторов, отражающий громежуточн-.." или конечный этап решения эь-,.-.,а и, а также не обеспе чив ает корми =о.-";.i-:è.—. с ",îáùåния минимально о Ожъем . Годео> ;- 1 его 0 промежуточные или кон -fHIJQ реэуJ,„òàrL.. решения задачи для выдачи в ЦВМ.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается

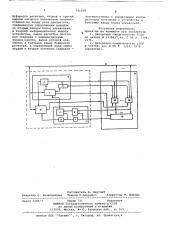

1 тем, что н устройство для сопряжения, содержащее буферный регистр и бгок управления, соединенные первыми входами и выходами соответственно с информационном в ходами и выходами «() устройства, регистр состояния, подключенный входами к соответствующим входам из группы входов состояния объектов устройстна, второй выход блока управления соединен с 25 выходом запуска устройства, введены память, два элемента задержки, узел приоритета и группа элементов И гашения, первые входы =-.ëcментов И гашения группы соединены с соответствующими индик ат срнн-;и 3 ходами ус тройстна, вторые входы — c соотв ет с.т вующи;;:и выходами узла приори тета и выходами иэ группы адресных выходов ус сройстна, управляющий вход — с --ретьим выходом блока управЯ ления и управляющим входом буферного регистр выход группы эле .сентов И гашения соединен со вторы входом ,буфеpnoro регистра, второй и третий выходы котor! o."o подключены 40 соответственно io в:.о,:., У=ла приоритета, соедк -1е,-:-.ому управляющим Bbl-. ходом с,з ., орым входом блока управления, и второму информационному выходу устройства, выход регистра состояния соединен с информационным в ходом памяти выход которой подключен к третьему входу буферного регистра, а угранляющий вход через первый и второй элементы задержки— соответственно к управляющим входам регистра состояния и устройства и третьему входу блока управления, На чертеже представлена блок-":."ема устройств а.

Схема устройства сoäåpæèò буферный регистр 1,. узел 2 приоритета, группу 3 элементов И гашения, составляющие блок 4 организации циклического обмена, память 5,, регистр

6 состояния, первый 7 и второй 8 6О элементы задержки, составляющие блок 9 формирования инструкций, и блок 10 управления, специализированное вы:ислительное устройство 11, включающее стохасти веские интеграторы 12 и блок 1 3 управлени я, и информационную магистраль 14 связи с

ЦВМ.

Блоком 4 организации циклического обмена при приеме информации от

ЦВМ осуществляется прием адресного слона,. Указывающего функциональное награвлениe и порядок следования исходной информации в информационном пакете, передаваемом в сопрягаемое устройство, распределение ин;ор;:лации в ссотве .rcr ÿêè с адресными си г."- ала,"нл, содержащиьплс я в адресном слове, а также прием и хранение кодон режимов работы сопрягаемого устройства .

При выдаче на ЦВМ промежуточных или конечных результатов решаемой задачи блок 4 осуществляет прием от блока 9 кодов состояния интеграторон и адресных сигналов, которые определяют функциональный признак и порядок следования информации н информационном пакете,а также н соответствии с адресным словом производит подключение интеграторов к информационной магистрали для выдачи результатов решения задачи на ЦВМ. Блок 10 управления предназначен для упранления обменом информацией между ЦВМ, блоком 4 и сопрягаемы« устройством при вводе и выводе информации.

Блок 9 формлрования инструкцией по позиционным сигналам состояния, поступающим от согрягаемогс устрой::гва, формирует код состояния и адресное слово, которое указывает, н: каком эт=;.пе реше:. ия задачи на ЦВМ будет выдана промежуточная или конечная информация, какой функциональный смысл в ней заключен и в ка-. ком порядке ее необходимо выдавать.

B регистр 1 riðè приеме информации

or ЦВМ заносится адресное слово и код режима работы сопрягаемого устройства. В адресном слоне каждому интегратору 12 выделен адресный разряд, наличие единицы в котором указывает на то, что при данном обмене в соответствующий интегратор будет заноситься информация ° Порядковый номер адресного разряда регистра 1 определяет очередность занесения информации н выбранный интегратор 12.

Узе -. 2 приоритета выбирает адресную ш, и,, того интегратора- 12, единч;- в адресном разряде регистра которого имеет высший приорит=-,. Оцнонременно адресные сигналы поступают на элементы 3 И группы чер =- которые после занесения информации н =-ыбранный интегратор производится гашение (сброс) того адресного разряда регистра 1, который был выбран узлом

2. При этом на ныходе узла 2 выбирается адрес следующего функционального направления.

При выдаче результата решения на

ЦВМ в ре ги стр 1 заносится адресное

741259 слово и код состояния интеграторов

12. В этом случае адресное слово указывает, из каких интеграторов и в какой последовательности на

ЦВМ будет выдаваться информация, Устройство работает следующим образом.

При приеме информации от ЦВМ первая информационная посылка, содержащая адресное слово и код режима, заносится в регистр 1 и подается на узел 2 для выбора адреса того интегратора 12, адресная единица которогб в адресном слове имеет высший приоритет, а на информационной магистрали 14 от ЦВМ выставляется информация, которую необходимо занести в выбранный интегратор. После занесения информации данный интегратор 12 формирует известительный сигнал, кото ый поступает на элементы 3

И группы. По сигналу от блока 10 производится гашение (сброс) адресного разряда, соответствующего данному интегратору. Узел 2 выбирает следующий разряд адресного слова, хранимого в регистре 1, в котором записана единица.и подключает адресный сигнал к следующему интегратору.

Аналогичным образом производится занесение информации в другие интеграторы, единицы в адресных разрядах которых были занесены в регистр 1 при обмене на данном цикле.

После занесения информации во все интеграторы, помеченные единицами в адресном слове, принятом от ЦВМ, узел 2 формирует управляющий сигнал, который поступает в блок 10 и извещает об окончании занесения информации. Блок 10 в свою очередь производит запуск интеграторов на выполнение основной операции. Код режима иэ регистра 1 поступает в блок. 13 для указания типа задачи и режима ее решения. (Выдача на ЦВМ промежуточных или конечных результатов решения задачи осуществляется по инициативе устройства 11. При этом интеграторы формируют позиционные сигналы состояния, которые заносятся в регистр б. Содержимое регистра 6 является адресом ячейки 5 памяти, где хранится инструкция. С задержкой на время занесения сигналов состояния в регистр б с выхода первого элемента 7 формируется сигнал запуска памяти . Чере з время, н еобходимое для считывания ин формации и з памяти, второй элемент 8 задержки вырабатывает сигнал, поступающий в блок 10 и извещающий его об окончании формирования инструкции. Эта инструкция содержит код устройства 11, а также адресное слово, ук а эыв ающе е из каких интеграторов 12 и в какой последовательности будет производиться выдача

34

46

6О

65 накопленной информации при данном обмен е с ЦВМ, При этом первым словом на ЦВМ передается содержимое регистра 1, а затем в соответствии с состоянием разрядов в адресном слове организуется поочередная выдача информации иэ интеграторов 12. Причем очередНость выдачи информации из интеграгоров определяется расположением их адресных разрядов в адресном слове регистра 1.

После выдачи информации с очередного интегратора производится гашение его адресного разряда в адресном слове регистра 1 узел 2 выбирает следующий интегратор и блоком 10 разрешается выдача информации на

UBM от вновь выбранного интегр тора.

Таким образом, устройство позволяет обеспечить подключение группы интеграторов, решающих одну общую задачу, и организовать обмен информацией таким образом, что вся информация, вводимая из ЦВМ или выводимая на ЦВМ, сопровождается только одним служебным словом, а это сокращает время обмена информацией между ЦВМ с сопря гаемыми устройствами.

Устройство позволяет также организовать циклический обмен информацией в процессе решени я задачи с выдачей на ЦВМ не только промежуточных или конечных результатов решений, но и кодов состояни я, указывающих, каким образом это решение проходило, что в свою очередь расширяет функциональные возможности устройства.

Формула изобретения

Устройство для сопряжения, содержащее буферный регистр и блок управ-. ления, соединенные первым входами и выходами соответственно с информационными входами и выходами устройства, регистр состояния, подключенный входами к соответствующим входам из группы входов состояния объектов устройства, второй выход блока управления соединен с выходом запуска устройства, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, в устройство введены память, два элемента задержки, узел приоритета и группа элементов И гашения, первые входы элементов И гашения группы соединены с соответствующими индикаторными входами устройства, вторые входы — с соответствующими выходами узла приоритета и выходами из группы адресных выходов устройства„ управляющий вход — c третьим выходом блока управления и управляющим входом буферного регистра, выход группы элементов И гашения соединен со вторым входом

741259

Составитель B. Вертлиб

Редактор О. Колесникова Техред О.Андрейко Корректор М. Шароши

Заказ 3326/7

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП - Патент, r. Ужгород, ул. Проектная,4 буферного регистра, второй и третий выходы которого подключены соответственно ко вхоцу узла приоритета, соединенному управляющим выходом со вторым входом блока управления, и второму информационному выходу устройства, выход регистра состояния соединен с информационным входом памяти, выход которой подключен к третьему входу буферного регистра, а управляющий вход через первый и второй элементы задержки— соответственно к управляющим входа регистра состояния и устройства и третьему входу блока управления.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке 9 2339617,кл. G 06 F 3/04, 1976.

2. Авторское свидетельство СССР

9 519704, кл, G 06 F 3/04, 1974 (прототип).