Устройство для вычисления синуснокосинусных произведений

Иллюстрации

Показать всеРеферат

Союз Соеетскнх

Соцналнстнческнх

Реслублнк

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ Сви ЕТЕЛЬСТВУ

< >741274 (6! ) Дополнительное к авт. свид-ву (22) Заявлено, 230178 (21) 2571967/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 1 0680, Бюллетень Ио 22 (51)М, Кл.2

G 06 F 15/34

Государственный комитет

СССР по делам изобретений н открытии (53) УДК 681. 3 (088.8>

Дата опубликования описания 1В0680 (72) Авторы изобретения

Е.И. Духнич и В.А. Митраков

Новороссийское высшее инженерное морское училище (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИНУСНО-КОСИНУСНЫХ

ПРОИЗВЕДЕНИЙ

Изобретение относится к области вычислительной техники и предназначено для построения на его основе специализированных ЦВМ.

Известно арифметическое устройство (1), содержащее сдвигающие регистры, коммутирующие блоки, сумматорывычитатели. Это устройство выполняет преобразование координат вектора при повороте осей прямоугольных координат (х,у) на угол d.и, в частности, позволяет одновременно вычислять функции х = sino( у = cos с(. (1> . 15

На практике часто требуется вычислять одновременно синусно-косинусные произведения вида

А = sin d. sing В = созд.- в1п(1 !

С = sin ф„- соя(, D = созс(.. сов ) 20

Синусно-косннусные произведения могут быть вычислены с помощью такого устройства за время выполнения трех преобразований. При выполнении первой операции получаются функции . 25 х,у, при второй — значения A и С и при третьей — В и D. Такое время реализации на практике не всегда допустимо, что является недостатком этого. устройства. 30

Наиболее близким по технической сущности к данному изобретению является устройство (2), содержащее три сумматора, три регистра, два коммутатора, блок управления, при этом выходы разрядов первого и второго регистров соединены с соответствующими входами первого и второго коммутаторов, управляющие входы которых соецинены с первым входом устройства, входы первого и второго регистров соединены с первым и вторым выходами устройства, а третьего регистра — с первым входом блока управления и выхо-. дом первого сумматора, первый вход которого соединен с выходом третьего регистра, а второй — со вторым вхо-. дом устройства, первые входы второго и третьего сумматоров соединены соответственно с выходами первого и второго регистров, а их управляющие входы — с первым выходом блока управления.

Недостатком такого устройства является большое время реализации преобразований.

Целью изобретения является повышение быстродействия устройства при вычислении синусно-косинусных произведений.

741274

11ель достигается тем, что предлагаемое устройство дополнительно содержит три регистра, два коммутатора и одинадцать сумматоров, причем выходы разрядов четвертого и пятого регистров соединены с соответствующими входами третьего и четвертого коммутаторов, первые входы четвертого, пятого и шестого сумматоров соединены с выходами соответственно четвертого, пятого и шестого регистров, первые выходы первого, второго, третьего и четвертого коммутаторов соединены соответственно с первыми входами седьмого, восьмого, девятого и десятого сумматоров и со вторыми входами третьего, второго, пятого и четвертого сумматоров, а их вторые выходы — соответственно с первыми входами одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров, выходы второго, третьего, четвертого и пятого сумматоров соединены соответственно со вторыми входами девятого, десятого, седьмого и восьмого сумматоров, а выходы седьмого, восьмого, девятого и десятого сумматоров соединены соответственно со вторыми входами двенадцатого, один- ..надцатого, четырнадцатого и тринадцатого сумматоров, выходы которых являются выходами устройства, причем выходы одиннадцатого и двенадцатого сумматоров соединены соответственно со входами пятого и четвертого регистров, второй вход шестого сумма" тора соединен со вторым входом устройства, а его выход — co вторым вхо". дом блока управления и входом Шестого регистра, управляющие входы четвертого, пятого и шестого сумматоров соединены с первым выходом блока управления, соединенного вторым выходом с управляющими..входами первого, седьмого, восьмого, девято|о и десятого сумматоров, а третьим — с уп-. равляющими входами одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров.

Вычисление синусно-косинусных произведений выполняется по алгорит1 - -24

А Ë;+ „; В,. 2.-+,„С„.-2 «P„@Dq 2

Р 1=Р1-g„Cq q2 "-(;2 В„" Ц„. ..А, 2, 8;+„=6„. — „„ р;, ЖМ 12Л где sign 6 $21=sign ((1 r o=oL, Яо=Pi D =1 A = В = С =О, i — номер итерации, % — угловая постоянная, равная

are tg 2

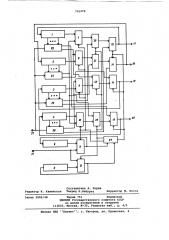

На чертеже представлена блок-схема предлагаемого устройства..

Она включает регистры 1-6, сумматоры 7-16, выход 17 (первый выход), выход 18 (второй выход), выход 19 (третий выход), выход 20 (четвертый выход), вход 21 угловой постоянной (второй вход), блок 22 управления, коммутаторы 23-26, вход 27 управляющего сигнала (первый вход), сумматоры 28-31.

Устройство работает следующим об5 разом.

Операнды я к Bj ю Cjp Р1 г В1 г Я1 хранятся в регистрах 1-6; по команде

1-й итерации из блока управления по входу 27 все коммутаторы соединяют, 10 свои первые выходы с выходами соответствующих разрядов регистров таким образом, что на входы блоков 7-10, 2831 поступают операнды, умноженные на величину 2 ", а свои вторые выходы— таким образом, чтобы на входы блоков

l3-16 поступили, операнды, умноженные на величину 2 ", С выходов младших разрядов регистров 1-6 ойеранды поступают на входы сумматоров 7-12, где в соответствии со значениями и 1, суммируются (вычитаются) с вели.

21 чинами, которые поступают с выходов блоков 23-26 и иэ запоминающего устройства по входу 21 соответственно.

25 С выходов сумматоров 7-10 результаты поступают на входы блоков 28-31, где суммируются (вычитаются) в соответствии с Ц2„ с операндами, умноженными на величину 2 ". С выходов блоков 283() 31 результаты пбступают на входы блоков 13-16, где в соответствии с сигналом („1 1,"21) суммируются (вычитаются) с операндами, умноженными на величину 2 ". Результаты операций Aq+<, З5 . В., с1+(, Р„-+„, 81«Я1.„..(записываются в регистры 1-6 соответственно.

Константы Ч„поступают иэ запоминающего устройства по входу 21, значения 6)1«q и Я„+(подаются на входы бло.ка управления 22, где используются

4О для определения значений k1(1+Ä) 2(„ 0 произведения <., ((„+11. g2(q.1 которые будут выдаваться на соответствующие выходы блока íà (i+1) -й итерации. Процесс повторяется до вы45 полнения заданного количества итераций. В конце операции результаты образуются на выходах 17-20.

ЭфФективность предлагаемого изо-бретения заключается в сокращении времени вычислений в три раза при увеличении объема оборудования примерно в два раза.

Формула изобретения

Устройство для вычисления синуснокосинусных произведений, содержащее три сумматора, три регистра, два коммутатора, блок управления, при этом

60 выходы разрядов первого и второго регистров соединены с соответствующими входами первого и второго коммутаторов, управляющие входы которых соединены с первым входом устройства, Я входы .первого и второго регистров

741274

30 соединены с первым и вторым выходами устройства, а третьего регистра — с первым входом блока управления и выходом первого сумматора, первый вход которого соединен с выходом третьего регистра, а второй — со вторым вхо-: дом устройства, первые входы второго и третьего сумматоров соединены соответственно с выходами первого и второго регистров, а их управляющие входы — с первым выходом блока управ- о ления, о т л и ч а ю щ е е с. я тем, что, с целью повышения быстродействия, устройство дополнительно содержит три регистра, два коммутатора и одиннадцать сумматоров, причем выходы разрядов четвертого и пятого регистров соединены с соответствующими входами третьего и четвертого коммутаторов, первые входы четвертого, пятого и шестого сумматоров соединены с выходами соответственно четвертого, пятого и шестого регистров, первые выходы первого, второго, третьего и четвертого коммутаторов соединены соответственно с первыми входами седьмого, восьмого, девятого, деся- 25 того сумматоров, и со вторыми входами третьего, второго, пятого и четвертого сумматоров, а их вторые выходы с первыми входами соответственно одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров, выходы второго, третьего, четвертого и пятого сумматоров соединены соответственно со вторыми входами девятого, десятого, седьмого и восьмого сумматоров, а выходы седьмого, восьмого, девятого и десятого сумматоров соединены соответственно со вторыми входами двенадцатого, одиннадцатого, четырнадцатого и тринадцатого сумматоров, выходы которых являются соответственно .первым, вторым, третьим и четвертым выходами устройства, причем выходы одиннадцатого и двенадцатого сумматоров соединены со входами соответственно пятого и четвертого регистров, второй вход шестого сумматора соединен со вторым входом. устройства, а его выход — co вторым входом блока управления и входом шестого регистра, управляющие .входы четвертого, пятого и шестого сумматоров соединены с первым выходом блока управления, соединенного вторым выходом с управляющими входами первого, седьмого, восьмого, девятого и десятого сумматоров, а третьим — c управляющими входами одиннадцатого, двенадцатого, тринадцатого и четырнадцатого сумматоров.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 445042, кл. G 06 F 7/38., 2. Система ДИВИК для решения сложных навигационных задач Электроника, Р 18, 1966, с. 3038 (прототип).

741274

Тираж 751 Подпи сн ое

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Эакаэ 3305/48

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Составитель А. Зорин

Редактор H. Каменская Техред H.Бабурка Корректор М. Коста