Устройство для кусочно-линейной аппроксимации функций времени

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистическими

Республик

<1>741285 (61) Дополнительное к авт. саид-ву (22) Заявлено 0901.78 (21) 2567895/18-24 (51)М. Кл.2 с присоединенйем заявки ¹

G 06 G 7/28

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 1506.80. Бюллетень № 22

Дата опубликования описания 180680 (53) УДК 681.335.

° 8 (088. 8) (72) Авторы изобретения

В.Е. Ямный, Э.И. Подольный, Ю.И. Белоносов и В.N. Чумак (71) Заявитель

Белорусский ордена Трудового Красного Знамени государственный университет им. В.И. Ленина (54) УСТРОЙСТВО ДЛЯ КУСОЧНО- ЛИНЕЙНОЙ АППРОКСИМАЦИИ

ФУНКЦИЙ ВРЕМЕНИ

Изобретение относится к аналоговой и аналого-цифровой вычислительной технике.

Известно устройство для.кусочнолинейной аппроксимации функций (1), 5 содержащее буферные регистры, цифроаналоговые преобразователи, операционные усилители, блок памяти, блок управления выборкой из памяти. Его недостатком являются значительные 1О аппаратурные затраты при аппроксимации функций времени.

Наиболее близким техническим решением к данному изобретению является устройство для кусочно-линейной аппроксимации функций времени (2), содержащее первый регистр, принимающий входной код, и второй регистр, принимающий от первого регистра код, запаздывающий на один интервал времени по отношению к коду, поступающему в первый регистр, два цифроаналоговых преобразователя, подключенных к выходам йервого и второго регистров, аналоговый интегратор с ключом 25 для разряда конденсатора интегратора, первый и второй входы интегратора подключены к выходам цифроаналоговых преобразователей, управляющий вход ключа соединен со входом смены Зр кодов второго регистра, и сумматор, .входы которого подсоединены соответственно к выходу интегратора и выходу второго цифроаналогового преобразователя, а выход является выходом устройства.

Это устройство позволяет преобразовывать цифровой код равноотстоящих ординат в кусочно-линейную Функцию времени. Однако этому устройству присущ существенный недостаток. При работе устройства разряд конденсатора интегратора происходит за конечное время и тем больше, чем больше время интегрирования. Во время разряда кон- денсатора интегратор нормально не функционирует, поэтому существенно возрастает погрешность аппроксимации в моменты смены кода в регистрах.

На выходе устройства эти погрешности проявляются в виде импульсных помех. ,Пля больших времен интегрирования емкость интегратора составляет единицы микрофарад, поэтому во избежание больших токов через ключ включают ограничительный резистор, что еще больше увеличивает рассмотренную погрешность

Целью изобретения является повышение точности устройства за счет уменьшения. импульсных помех.

741285

d0

65. то достигается тем, что устройство для кусочно.-линейной аппроксимации функций времени, содержащее первый и второй буферные регистры, первый и второй цифроаналоговые преобразователи, цифровые входы которых соединены с выходами соответствующих буферных регистров, входы первого бу- ° ферного регистра являются цифровыми входами устройства, а его выходы сое динены со входами второго буферного регистра, управляющие. входы буферных регистров объединены и являются управляющим входом устройства, аналоговый сумматор, выход которого является выходом устройства, а первый вход соединен с выходом второго цифроаналогового преобразователя, операционный усилитель, вход которого через первый и второй входные резисторы соединен с выходами первого и второго цифроаналоговых преобразователей, а выход соединен со вторым входом аналогового сумматора, первый интегрирующий конденсатор, соединенный одним выводом со входом операционного усилителя, первый разрядный ключ, подсоединенный параллельно к первому интегрирующему конденсатору, дополнительно содержит второй интегрирующий конденсатор, второй разрядный ключ, первый и второй коммутирующие ключи и триггер управления ключами, счетный вход которого подключен к управляющему входу устройства, прямой выход — к управляющим входам второго разрядного и первого коммутирующего ключей, инверсный выход — к управляющим входам первого разрядного и второго коммутирующего ключей, второй интегрирующий .конденсатор соединен одним выводом со входом операционного усилителя, а другим выводом через второй коммутирующий ключ с выходом операционного усилителя, второй разрядный ключ подсоединен параллельно второму интегрирующему конденсатору, первый коммутирующий ключ включен между другим выводом первого интегрирующего конденсатора и выходом операционного усилителя.

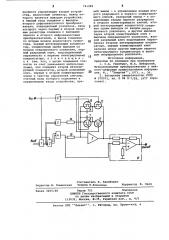

Схема устройства для кусочно-линейной аппроксимации функций временч приведена на чертеже.

Устройство содержит первый и второй буферные регистры 1, 2, первый и второй цифроаналоговые преобразователи 3, 4, операционный усилитель 5, триггер б управления ключами, первые интегрирующий конденсатор 7 и разрядный ключ 8, вторые интегрирующий конденсатор 9 и разрядный ключ 10, первый и второй коммутирующие ключи 11, 12, аналоговый сумматор 13, первый и второй входные резисторы 14, 15.

Устройство для кусочно-линейной аппроксимации функций времени работает следующим образом.

В исходном состоянии регистры 1 и

2 установлены в нулевое состояние..На выходах цифроаналоговых преобразователей 3 и 4 и на выходе операционного усилителя 5 напряжение равно нулю. Два ключа 8 и 12 или 10 и ll замкнуты. Примем, что в исходном состоянии были замкнуты ключи 8 и 12.

При поступлении на выход регистра 1 кода первой ординаты и подачи управляющего импульса в регистр 2 перепишется состояние регистра 1 (т.е. нуль), а в .регистр 1 запишется код первой ординаты. Это приведет к появлению напряжения, пропорционального коду первой ординаты на выходе цифроаналогового преобразователя 3, На выходе цифроаналогового преобра15 зователя 4 напряжение в этот момент равно нулю. К операционному усилителю 5 подключится ранее разряженный конденсатор 9.

Напряжение с выходов цифроаналоговых преобразователей 3 и 4 поступают на входные резисторы 14, 15 и их сумма интегрируется конденсатором 9.

Следующим управляющим импульсом опрокидывается триггер б управления ключами, содержимое буферного регистра

1 переписывается в буферный регистр

2, а .в буферный регистр 1 заносится код второй ординаты. После опрокидывания триггера 6 интегрирующий конденсатор 9, который зарядился к конЗ0 цу интервала аппроксимации до напряжения, равного первой ординате, отключается с помощью ключа 12 от усилителя 5 и разряжается ключом 10, а к усилителю 5 подключается с помощью

35 ключа ll ранее разряженный с помощью ключа 8 конденсатор 7.

На выходах цифроаналоговых преобразователей 3 и 4 появятся напряжения, а напряжение на выходе операционного усилителя 5 начинает изменяться по линейному закону практически сразу со сменой кода ординаты.

Таким образом включение дополнительного конденсатора, трех ключей и триггера управления ключами позволяет устранить влияние конечного времени разряда интегрирующего конденсатора на работу ус-.ройства и повысить точность аппроксимации функций времени по сравнению с прототипом.

Формула изобретения устройство для кусочно-линейной аппроксимации функций времени, содержащее первый и второй буферные регистры, первый и второй цифроаналоговые преобразователи, цифровые входы которых соединены с выходами соответствующих буферных регистров, входы первого буферного регистра являются цифровыми входами устройства, а его выходы соединены со входами второго буферного регистра, управляющие входы буферных регистров объединены и

741285

Составитель Н. Балабошко

Редактор Н. Каменская Техред Н.Ковалева Корректор Е. Папп

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-.35, Раушская наб., д. 4/5

Заказ 3205/48 филиал ППП Патент, г. Ужгород, ул. Проек гкал, 4 являются управляющим входом устройства, аналоговый сумматор, выход которого является выходом устройства, а первый вход соединен с выходом второго цифроаналогового преобразователя, операционный усилитель, вход которого через первый и второй входные резисторы соединен с выходами первого и второго цифроаналоговых преобразователей, а выход соединен со вторым входом аналогового сумматора, первый интегрирующий конденсатор, соединенный одним выводом со входом операционного усилителя, первый разрядный ключ, подсоединенный параллельно к первому интегрирующему конденсатору, о т л и ч а ю щ е е— с я тем, что, с целью повышения точности эа счет уменьшения импульсных помех, оно содержит второй интегрирующий конденсатор, второй разрядный ключ, первый и второй коммутирующие ключи и триггер управления, ключами, счетный вход которого подключен к управляющему входу устройства, прямой выход — к управляющим входам второго разрядного и первого коммутирующего ключей, инверсный выход — к управляющим входам первого разрядного и второго коммутирующего ключей, второй интегрирующий конденсатор,;соединен одним, выводом со входом операционного усилителя, а другим выводом через второй коммутирующий ключ с выходом операционного усилителя, второй разрядный ключ подсоединен параллельно второму интегрирующему конденсатору, первый коммутирующий ключ включен между другим выводом первого интегрирующего конденсатора и выходом операционного усилителя.

l, Источники информации, принятые во внимание при экспертизе

1. С.A. Гинзбург, Ю.А. Любарский.

Функциональные преобразователи с аналого-цифровым представлением информации. И., Энергия, 1973, с. 36.

2. Авторское свидетельство СССР

Р 570071, кл. G 06 GI7/28, 1977 (прототип).