Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

G 11 С 13/00

Гасударственный комитет

Опубликовано 15.06.80. Бюллетень №22

Дата опубликования описания 21.06.80 (53) УДК 681.327 (088.8) А0 делам нэобретений н открытий (72) Автор изобретения

В. И. Шилинговский (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах ЦВМ с параллельной обработкой информации.

Известно постоянное запоминающее устройство с выдачей информации в параллельном коде, содержащее регистр адреса с многовходовыми элементами ИЛИ на его выходах, счетчик с элементами И на его выходах, кольцевые пересчетные схемы, общий элемент ИЛИ, схему пуска и останова (1(.

Недостатком такого устройства является низкое быстродействие, которое определяется временем заполнения кодового счетчика.

Наиболее близким техническим решением к данному изобретению является постоянное запоминающее устройство, содержащее регистр адреса, соединенный через дешифратор с адресными шинами, кольцевые пересчетные блоки, кодовый счетчик, разрядные выходы которого подсоединены к первым входам выходных элементов И, многовходовые элементы ИЛИ, соединенные по входам с адресными шинами и по выходам с соответствующими элементами кольцевых пересчетных блоков, выходы которых подключены ко входам элемента И, выход которого подключен через линию задержки к шине установки в исходное состояние и ко вторым входам выходных элементов И (21.

Однако это устройство характеризуется невысоким быстродействием, определяемым временем заполнения кодового счетчика, в котором формируется считываемое слово.

Целью изобретения является повышение быстродействия устройства.

Цель достигается тем, что в предлагаемое о устройство введены дополнительно две группы элементов ИЛИ, m элементов И,(где

tll — количество групп считываемых слов), кольцевой регистр сдвига на и Хт разрядов, (где rl — разрядность считываемых слов), инвертор, вход которого соединен с выходом пересчетного блока и первыми входами элементов И, а выход — с дополнительным входом второго элемента И, выход которого соединен со входом регистра сдвига, установочный вход которого соединен с выходом линии задержки, шины опроса разрядных слов — с выходами элементов И, вторые входы которых соединены с соответствующими выходами элементов ИЛИ первой дополнительной группы, входы которых со741321

1Î

Формула изобретения

55 единены с выходами дешифратора адреса, выходы элементов ИЛИ второй дополнительной группы соединены с информационными выходами устройства, а их входы — соответственно с одноименными разрядными выходами регистра сдвига.

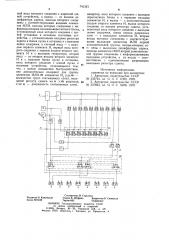

На чертеже представлена блок-схема описываемого устройства.

Оно содержит регистр 1 адреса, адресную шину 2, дешифратор 3 адреса, элементы

4 = 1 — 4-8 ИЛИ, пересчетный блок 5, состоящий из ячеек 6-1 — 6-8 памяти, шину 7 установки устройства в исходное состояние, блок 8 пуска и останова, линию 9 задержки, элементы 10 и 11 И, генератор 12, шину 13 пуска и останова, инвертор 14, элементы15-1, 15-2 И, кольцевой регистр 16 сдвига, шины 17 опроса разрядных слов, элементы 18-1, 18-2, 19-1 — 19-8 ИЛИ, ячейки 20-1 20-16 памяти кольцевого регистра сдвига.

Кольцевой регистр 16 сдвига предназначен для записи начального кода числа, определяемого подсоединением информационных входов кольцевого регистра 16 сдвига с установочным входом. Элементы 4-1 — 4-8, 18-1, 18-2 ИЛИ предназначены для организации произвольной выборки слов по данному адресу путем подсоединения входов этих элементов к выходам дешифратора 3 адреса.

Информационный вход регистра 1 адреса соединен с адресной шиной 2 устройства, а выход — со входом дешифратора 3 адреса, выходы которого соединены с соответствующими входами элементов 4-1 — 4-8 ИЛИ, выходы которых соединены соответственно с информационными входами пересчетного блока 5, которыми являются входы ячеек

6-1 — 6-8 памяти. Установочный вход пересчетного блока 5 соединен с шиной 7 установки в исходное состояние устройства, с установочными входами регистра 1 адреса и блока 8 пуска и останова и с выходом линии 9 задержки, а счетный вход — с выходом первого элемента 10 И, первый вход которого соединен с первым входом второго элемента 11 И и с выходом генератора 12, второй вход — со вторым входом второго элемента 11 И и с выходом блока 8 пуска и останова, вход которого соединен с шиной 13 пуска и останова устройства.

Вход инвертора 14 соединен с выходом пересчетного блока 5 и первыми входами элементов 15-1, 15-2 И, а выход — с дополнительным входом второго элемента 11 И, выход которого соединен со входом кольцевого регистра 16 сдвига, установочный вход которого соединен с выходом линии 9 задержки. Шины 17 опроса разрядных слов соединены с соответствующими выходамй элементов 15-1, 15-2 И, вторые входы которых соединены с соответствующими выходами элементов 18-1, 18-2 ИЛИ, входы которых соединены соответственно с выходами дешифратора 3 адреса. Выходы элементов

19-1 — 19-8 ИЛИ соединены с информационными выходами устройства, а их входы—

2О

25 зо

З5

4О

4S

5О соответственно с одноименными разрядными выходами регистра 16 сдвига, которыми являются выходы его ячеек 20-1 — 20-.16 памяти.

Устройство работает следующим образом.

В исходном состоянии в регистре 1 адреса и пересчетном блоке 5 записан нулевой код числа, а в кольцевом регистре 16 сдвига начальный код числа. При подаче кода адреса на адресную шину 2 устройства возбуждается один выход дешифратора 3 адреса, с которого разрешающий сигнал через элементы 4-1 4-8 ИЛИ и 18-1, 18-2 ИЛИ поступает соответственно на информационный вход одной ячейки 6 памяти пересчетного блока 5 и второй вход одного из элементов 15 И. С приходом импульса с генератора 12 на вторые входы элементов 10 и 11 И и сигнала с шины 13 пуска и останова через блок 8 пуска и останова на первые входы элементов 10 и 11 И, на выходе этих элементов формируются сигналы, по которым в подготовленную ячейку 6 памяти записывается «1», а в кольцевом регистре 16 сдвига информация сдвигается на один разряд. С приходом каждого следующего импульса с генератора 12 в пересчетном блоке 5 «1» переносится в последующую ячейку 6 памяти, а в кольцевом регистре 16 сдвига информация сдвигается на один разряд. Сигнал, сформировавшийся на выходе пересчетного блока 5, поступает через инвертор 14 на дополнительный вход элемента 11 И, закрывая его, и на первые входы элементов 15-,1, 15-2 И, формируя на соответствующей шине 17 опроса разрядных слов импульс считывания из ячеек 20-1—

20-16 памяти информации, записанной в них к этому моменту времени, которая через элементы 19-1 — 19-8 ИЛИ поступает на информационные выходы устройства. Сигнал с выхода пересчетного блока 5 через линию 9 задержки производит установку элементов устройства в исходное состояние, и устройство готово к следующему обращению.

Количество разрядов кольцевого регистра сдвига п Xm равно количеству записанных в устройство различных слов, а общее количество записанных слов равно количеству выходов дешифратора адреса. При этом в качестве начального кода может быть использован, например, код ориентированного цикла, образующий ориентированный эйлеров граф.

В описываемом устройстве наибольшее время выборки равно и тактам, а в устройстве-прототипе это время равняется 2» тактам, следовательно, предлагаемое устройство имеет большее быстродействие, чем и определяется его достоинство.

Постоянное запоминающее устройство, содержащее регистр адреса, информацион741321

Составитель И. Горелова

Техред К.Шуфрич Корректор В. Синицкая

Тираж 662 Подписное

LlHHHllH Государственного комитета СССР по делам изобретений и открытий

I 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП сПатент>, г. Ужгород, ул. Проектная, 4

Редактор Н. Каменская

Заказ 3210/49 ный вход которого соединен с адресной шиной устройства, а выход — со входом дешифратора адреса, выходы которого соединены с соответствующими входами элементов ИЛИ, выходы которых соединены с информационными входами иересчетного блока, установочный вход которого соединен с шиной установки в исходное состояние устройства, с установочными входами регистра адреса и блока пуска и останова и с выходом линии задержки, а счетный вход — с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И и с выходом генератора, второй вход — со вторым входом второго элемента

И и с выходом блока пуска и останова, вход которого соединен с шиной пуска и оста нова устройства, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит две группы элементов ИЛИ, N элементов И, (где 1т1в количество групп считываемых слов), кольцевой регистр сдвига на и Х 1т1 разрядов, (где Il — разрядность считываемых слов), инвертор, вход которого соединен с выходом пересчетного блока и с первыми входами элементов И, а выход — с дополнительным входом второго элемента И, выход которого соединен со входом регистра сдвига, установочный вход которого соединен с выходом линии задержки, шины опроса разрядных слов — с выходами элементов И, вторые входы которых соединены с соответствующими выходами элементов ИЛИ первой дополнительной группы, входы которых со1о е; нены с выходами дешифратора адреса, выходы элементов ИЛИ второй дополнительной группы соединены с информационными выходами устройства, а их входы — соответственно с одноименными разрядными выходами регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 335724, кл. G 11 С 17/00, 1970.

ze 2. Авторское свидетельство СССР № 337823, кл. G 11 С 13/00, 1970.