Импульсный умножитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ „,741442

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социапистическмк

Республик (61) Дополнительное к авт. саид-ву— (22)Заявлено 09.11,7 (2I) 2540897/18-21 (5т )Щ. (л.

Н 03 К 5/156 с присоединением заявки РЙ—

Веудэрстееииый комитет (23) Приоритет— до делам изобретений и открытиИ

Опубликовано 15.06.80. Бюллетень ¹ 22

Дата опубликования описания 16.06.80 (53) УДК 621. .374.44 (088. 8) В. И. Галкин, Д. С. Дубинин, Г. А. Комоцкий, A. Ж. Курмаев, Р. С. Романов, К. К. Чемарда, В. H. Барьков, В. В, цыганков, и Г. ф. Шамин (72) Авторы изобретения (7!) Заявитель (54) ИМПУЛЬСНЫЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к импульсной технике и может быть использовано для умножения частоты следования импульсов в измерительных устройствах.

Известны импульсные умножители частоты, позволяющие производить умноже5 ние частоты следования импульсов в широком диапазоне изменения исходной частоты в целое число раз (1) .

Наиболее близким по технической сущ10 ности является дискретный умножитель частоты, содержащий элемент задержки, вход которого соединен с входом устройства и с одним из входов элемента ИЛИ, триггерный делитель частоты, вход которого соединен с выходом элемента задержки, а выходы через последовательно соединенные формирователи и элементы совпадений — с остальными входами элемента ИЛИ, при этом вторые входы элементов совпадений соединены с выходом программного устройства (2) .

Это устройство, позволяя умножать исходную частоту слепования импульсов

2 в дробное число раз, не обеспечивает равномерность выходной последовательности импульсов, а это сужает область его применения, не позволяя использовать известный умножитель в измерительных и других устройствах.

Йель изобретения — обеспечение формирования равномерной импульсной последовательности на выходе устройства при умножении исходной частоты в— и+л тъ раз и широких пределах ее изменения, Это достигается тем, что в импульсный умножиталь частоты, содержащий триггерный делитель частоты, элемент

ИЛИ, и формирователей и элементов совпадений, введены управляемый генератор, включенный между входом устройства и входом триггерного делителя частоты, П триггеров, выходы которых соединены с BxoA&MH соответствующих им элементов совпадений и вторыми входами последую цих триггеров, а первые входы— с выходами элементов совпадений, триггер с раздельным запуском, включенный между входом устройства и формирователем, делитель частоты в и рез и элемент ИЛИ, входы которого соецннены с вхоцами первого элемента ИЛИ и выходами формирователя и пелителя частоты в и раз, а выхоц — со вторыч вхоцоч первого из и триггеров, при этом, вход целителя частоты в Yl раз соединен с вхопом устройства и обнуляющим вхопом целителя частоты, а обнуляюн ий вход триггера с раздельным запуском соединен с обнуляющим входом делителя частоты в раз и обнуляющич входом устройства.

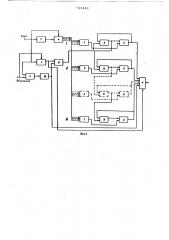

На фиг. 1 показана функциональная схема описываемого умножителя частоты; на фиг. 2 — временные пиаграмчы поясняющие его работу, Импульсный умножитель частоты сопержит делитель 1 частоты в и раз, управляемый генератор 2, триггер 3 с раз2О дельным запуском, целитель 4 частоты, Р формирователей 5, ri элементов 6 совпадений, первый элемент 7 ИЛИ, и триггеров 8, второй элемент 9 ИЛИ и формирователь 10. Выход первого элемента

ИЛИ является выходом устройства.

Для упрощения рассмотрим работу устройства пля и =3. Входная импульсная последовательность (фиг, 2a) поступает на вход управляемого генератора 2, час30 тота следования импульсов не выходе которого равнаг (фиг. 2б), гпе1 „-частота следования импульсов на входе управляемого генератора, а также на вход делителя 1 частоты в 3 раза. Коэффи35 циент тт выбирается равны M оп=к(п+1 ), гae — целое положительное число, Для рассматриваемого примере примем

К =2, т.е.п =8, причем вместо управляемого генератора 2 может быть исполь- 4о зован умножитель частоты в целое число раз, С выхоца управляемого генератора

2 импульсная последовательность (фиг. 2б) поступает на триггерный делитель 4 частоты. На формирователи 5 импульсы пос- 45 тупают с соответствую ших плеч триггеров триггерного делителя 4 таким образом, что на выходах формирователей 5 формируются импульсные последовательности (фиг. 26,2, ) импульсы которых отстоят соответственно на} „, К (п-1), (n-2) от импульсе управляемого генератора 2 (отсчет производится после обнуления триггерного делителя 4 вхопной импульсной последовательности

55 (фиг. 2а) .

Далее эти и иул сы (фиг. 2,г,g) поступают на свои пвухвхоцовые элементы 6

741442

4 совпадений, не вторые входы которых поступают импульсы (фиг. 2е,ж, z) с триггеров 8, которые разрешают прохождение через элементы 6 совнапений импульсных последовательностей (фиг. 2и,к,т ), Для подготовки схемы к работе на обнуляющий вход триггера 3 с разпельныч запуском поступает внешний обнуляющий импульс (фиг. 2ч), который переводит триггер 3 с раздельным запуском (фиг. 2н ) в исходное положение и обнуляет целитель 1 частоты в и раз, Внешний обнуляюший импульс (фиг. 2ч) поступает перец первым импульсом вхоцной импульсной последовательности. В этот момент, когда первый импульс входной импульсной последовательности (фиг. 2о) произвепет переключение триггера 3 с разпельным запуском, на выхопе формирователя

10 образуется импульс (фиг. 2p), который поступает на один из входов первого элемента 7 ИЛИ пля получения на его выходе импульсе, соответствующего первому импульсу вхопной последовательности (фиг. 2a), который будет также первым импульсом умноженной импульсной послеповательности (фиг. 2n ), а также поступает через второй элемент 9 ИЛИ на опии из входов триггера 8, обеспечивая подготовку его к работе (фиг. 2e).

Триггер 8 разрешает прохождение шес— того импульса (фиг, 2и) через элемент

6 совпадений на вход первого элемента

7 ИЛИ. Ыестой импульс с выхода элемента 6 совпадений возврашает триггер

8 в исходное состояние (фиг. 2e), опновременно переключая (фиг. 2Ж), следующий триггер Р и разрешал прохождение четвертого импульса (фиг. 2 ) через элемент 6 совпадений. С выхода элемента

6 совпадений четвертый импульс (фиг. 2 поступает на один из входов первого элемента 7 ИЛИ и устанавливает триггер 8 в исходное состояние (фиг. 2ж), переключая (фиг. 25) следующий триггер

8 и обеспечивая прохожцение второго импульса (фиг. 2 p) через элемент 6 совпадений на оцин из входов первого элемента 7 ИЛИ. Второй импульс в свою очередь устанавливает триггер 8 в исходное состояние (фиг. 2 ч), Далее процесс повторяется с той лишь разницей, что не вход триггера 8 начинают поступать импульсы (фиг. 2р) с пелителя 1 частоты в р раз. На выходы первого элемента

7 ИЛИ формируется умноженная в —гМ

= 4 раз импульсная послс цоветельность з (фиг. 2 p ).

5 7414

Описанный импульсный умножитель частоты обеспечивает получение на выходе импульсной последовательности, умноженной в раз, с неравномерностью, не превышающей 1 4 от периода сле- дования импульсов, устойчивую работу устройства при изменении исходной частоты в широких пределах до > 40%, возможность реализации устройства на современной элементной базе, что позволяет 10 .использовать его в цифровых измерительных устройствах и в устройствах магнитной записи цифровой информации с самосинхронизацие й, tS формула изобретения

1. Импульсный умножитель частоты, содержащий триггерный делитель частоты, элемент ИЛИ, rl формирователей и элемен-20 тов совпадений, отличающийся тем, что, с целью обеспечения равномерной импульсной последовательности на выходе при умножении в раз в него г 1

A введены делитель частоты в г1 раз, П триггеров, триггер с раздельным запуском, формирователь, второй элемент ИЛИ и управляемый генератор, выход которого соединен с входом триггерного делителя частоты, а вход с входом устройства, с 30

42 6 входом делителя частоты в t1 раз, с единичным входом триггера с раздельным запуском и обнуляющим входом триггерного делителя частоты, при этом его выходы через формирователи и двухвходовые элементы совпадений соединены- с входами первого элемента ИЛИ, и первыми входами триггеров, выходы которых соэ; динены со вторыми входами соответствующих им элементов совпадений и вторыми входами последующих триггеров, при этом второй вход первого триггера соединен с выходом второго элемента

ИЛИ, первый вход которого соединен со входом первого элемента ИЛИ, входом делителя частоты в и раз, а второй— со входом первого элемента ИЛИ и через формирователь с выходом триггера с раздельным запуском, обнуляющий вход которого соединен с обнуляющим входом делителя частоты в и раз и обнуляющим входом устройства.

Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

М 306543, кл. Н 03 В 19/00, 15.04. 69.

2. Авторское свидетельство СССР

И 365823, кл. H 03 К 5/156, 25.05.71 (прототип).

741442

Составитель E. Борзов

Редактор П. Макаревич Техред Ж.Кастелевич Корректор Г.Назарова

Заказ 3334/10 Тираж 995 Подписное

LB)HHHH Государственного комитета ССС Р по делам изобретений и открытий

113035, Москва, Ж-35, Раушскяи ням., д. 4/5

Филиал ППП "Патент, г. Ужгород, ул. Пр ктп s t, 4