Селектор импульсов заданной длительности

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1 ц741444 (61) Дополнительное к авт. свнд-ву ¹ 6156pp (22) Заявлено 23,12.77 (2l) 2557687/18-21 с присоединением заявки № (5! )М. Кл.

Н 03 К 5/18

Гоаударстеениый комитет

СССР (23) Приоритет— ао делам изобретений и открытий

Опубликовано 15.06.80. Бюллетень ¹ p2

Дата опубликования описания 16.06.80 (53) УДК 621. .374.3 (088. 8) (72) Авторы изобретения

P. Г. Джагупов, Г. С. Вайсман и Р. К. Мамедов

Азербайджанский институт нефги и химии им. М. Азизбекова (71) Заявитель (54) СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ

ДЛИТ ЕЛЬНОСТИ, l 2

Изобретение относится к импульсной технике и может найти применение в автоматических устройствах для поиска и селекции пар импульсов заданной длительности следуюших друг за другом в носле5 довательности импульсов со случайной фазой фронта.

По основному авт. свид. ¹ 615600 известен селектор импульсов заданной длительности, содержаший ждуший мультивиб-„ ратор, выполненный на логических элементах И и НЕ, вход которого соединен со входной шиной, а выход соединен с фор. мирователем сигнала заднего фронта эталоннот о импульса> выход которого подклютg чен к первому входу выходного aors кого элемента И, второй axon которого соединен с выходом формирователя сигнала заднего фронта входного импульса, вход которого подключен к входной шине, 2о формирователь стробируюшего импульса, состояший из последовательно включенных логических элементов НЕ, выходы которых соединены со входами логического элемента И и фазосдвигаюшего конденсатора, причем вход формирователя стробируюшего импульса соединен с там межуточным выходом формирователя сигнала заднего фронта и входного импульса, а выход формирователя стробируюшего сигнала, соединен со входом сброса ждушего мультивибратора 1) Данное устройство может быть применено в случае, когда фиксация момента прихода им пульса заданной длительности происходит в обрабатываемой последовательности импульсов.

Однако известный селектор лишен во:.ьможиости фиксировать момент появления какой-либо комбинации импульсов заданных длительностей в последовательности, например появления двух смежтых импульсов заданных длительностей в последовательности. Это ограничивает функциональные возможности известных селекторов, поскольку в такой комбинации может быть передана дополнительная информация.

3 7414

Цепью изобретения является обеспечение селекции двух смежных импульсов заданной дпитепьности.

Поставленная цепь достигается тем, что в селектор импульсов заданной дпитепьности, содержащий ждущий мультивибратор, выполненный на логических апементах И и НЕ, вход которого соединен со входной шиной, а выход соединен с формироватепем сигнала заднего фронта эта- 10 лонного импульса, выход которого подключен к первому входу выходного логического элемента И, второй вход которого соединен с выходом формирователя сигнала заднего фронта входного импульса, 1s вход которого подключен к входной шине, формирователь стробирующего импульса, состоящий из последовательно включенных логических элементов НЕ, выходы которых соединены со входами погичес- 20 кого элемента И и фазосдвигающего конденсатора, причем вход формнроватепя стробирующего импульса соединен с промежуточным выходом формирователя сигнала заднего фронта и .входного импульса, а выход формирователя стробирующего сигнала соединен со входом сброса ждущего мупьтивибратора, введен выходной коммутирующий блок, один вход которого соединен с выходом логического эле- 30 мента И, второй вход подключен к выходу логического элемента И формирователя заднего фронта импульса, а третий вход подключен к шине запуска, а выходной коммутирующий блок, состоит из триггера, один вход которого через логический элемент НЕ соединен с выходом погического элемента ИЛИ, два входа которого подключены ко входам выходного коммутирующего блока, а третий соединен с первым выходом триггера и первым входом логического элемента И и через второй логический элемент НЕ с третьим входом выходного коммутирующего блока, причем второй вход второго логического апемента И соединен со вторым выходом триггера, второй вход которого подключен к выходу второго логического эпемента И установки "О триггера.

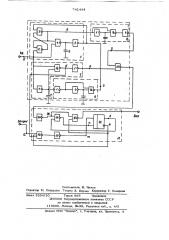

На чертеже приведена структурная электрическая схема селектора импульсов заданной длительности.

Селектор состоит из формирователя 1 импульса эталонной длительности, представпяющего собой ждущий мупьтивибратор, 5 собранный на логических элементах 2-5И и конденсаторе 6, формирователя 7 сигнапов, соответствующих заднему фронту

44 ф входного импульса, формирователя 8 сигналов, соответствующих заднему фронту импульса атапонной длительности, формирователя 9 стробирующего импульса, погического элемента 10 И,. выходного коммутирующего блока 11, вкпючающего триггер 12, логические элементы 13, 14 НЕ, 15, 16 И, 17 ИЛИ. Элементы

1 и 7-10 образуют селектор импульсов.

Работа устройства осуществляется следующим образом.

Предварительно на вход сброса логического элемента 17 ИЛИ подается импульс, приводящий устройство в исходное состояние, на другом входе этого эле-мента существует положитепьный потенциап, открывающий его. Выходной импульс этого элемента после инвертирования сбрасывает триггер 12. При этом после дни и пр ям ым выходом открывает элемент 15 И и инверсным выходом закрывает другой элемент 16 И. Каждый из импульсов входной последовательности передним фронтом запускает формирователь 1 импульса эталонной дпитепьности, который вырабатывает импульс эталонной длительности, Этот импульс подается на формирователь 8; который формирует сигнап, соответствующий заднему фронту импульса эталонной длительности. Этот сигнал подается на один из входов логического апемента И 10.

В параллельном канапе формирователем 7 формируется сигнал, соответствующий заднему фронту входного импульса, который подается на второй вход элемента .10 И. При одновременном воздействии этих сигнапов последний выдает импульс селекции, который свидетельствует о приходе импульса заданной длительности. Импульс селекции после инвертирования на эпементе 13 НЕ подается на информационные входы элементов 15 и 16 И.

Через открытый в данный момент элемент

15 И импульс селекции поступает на триггер 12 и сбрасывает его. На селектор поступает второй входной импульс. Возможны два случая, когда дпитепьность второго импульса совпадает с эталонной длительностью и когда дпитепьность второго импульса не совпадает с эталонной дпитепьностыо.

В случае, когда длительность второго импупьса совпадает с эталонной длительностью, на элемент 10 И одновременно поступают сигналы, соответствуюшие задним фронтам указанных импульсов, и апемент 10 И выдает импульс селекции этот

741444 импульс после инвертирования на элементе 13 НЕ поступает на информационные входы элементов 15 и 16 и через открытый в данный момент элемент 16 И подается. на выходную шину селектора двух смежных импульсов.

В случае, когда длительность второго входного импульса не равна эталонной длительности, сигнал селекции не формируется, а коротким импульсом с формирователя 7 сигнала, соответствующего заднему фронту входного импульса через элемент 17 ИЛИ и элемент 14 НЕ осуществляется перекидывание триггера 12. При этом вновь открывается элемент 15 Й и закрывается элемент 16 И, Селектор возвращается в исходное положение и оказывается готовым к опросу следующей пары смежных импульсов из входной последовательности.

Формула изобретения

1. Селектор импульсов заданной длительности по авт. М 615600, о т л ич а ю шийся тем, что, с целью селекции двух смежных импульсов заданной длительности, в него введен выход,ой коммутирующий блок, один вход которого соединен с выходом логического элемента И, второй вход подключен к выходу логического элемента И формирователя заднего фронта импульса, а третий вход подключен к шине запуска.

2. Селектор по п. 1, о т л и ч аю шийся тем, что выходной коммутирующий блок состоит из триггера, один вход которого через логический элемент. !

О не соединен с выходом логического элемента ИЛИ, два выхода которого подключены ко входам выходного коммутирующего блока, а третий вход соединен с первым выходом триггера и первым

15 входом логического элемента И, второй вход которого соединен с одним входом второго логического элемента И и через второй логический элемент НЕ с третьим входом выходного коммутирующего бло20 ка, причем второй вход логи-еского элемента И соединен со вторым выходом триггера, второй вход которого подключен к выходу второго логического элемента И.

Источники информации, Ф принятые во внимание при экспертизе

1, Авторское свидетельство СССР

N 615600, кл. Н 03 К 5/18, 25.10.76.

741444

Составитель В. Чижов

Редактор Ю. Петрушко Техред Я. Яир.щк Корректор Г, Назарова

Заказ 3334/10 Тираж 995 Подписное

Ш1ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж 35, Раушская наб„д. 4/5 филиал ППП "Патент, г, Ужгород, ул. Проектная, 4