Преобразователь напряжения-код одиночных импульсов

Иллюстрации

Показать всеРеферат

Ссноз Советских

Социалистических

Республик (61) Дополнительное.к авт. свид-ву— (22) Заявлено 24.1078 (21) 2677181/18-21 с присоединением заявки N9 (23) Приоритет—

Опубликовано 150680 Бюллетень Ио 22

Дата опубликования списания 150680

Н 03 К 13/ 6

Государственный коннтет

СССР по делам нзобретеннй н открытий (53) УДК 681. 325 (088. 8) (72) Авторы изобретения

A.A. Осьминин и Г.Н. Абрамов (71) Заявитель

Ульяновский политехнический институт (54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ-КОД

ОДИНОЧНЫХ ИМПУЛЬСОВ

Изобретение относится к импульсной технике и может быть использовано в измерительных радиотехнических устройствах преобразования амплитуды коротких одиночных импульсов.

Известен преобразователь, содержащий М (число уровней квантования) пороговых устройств, выходы которых подключены к входам шифратора (1) .

Недостатком данного преобразователя является низкая надежность особенно при большом числе разрядов в выходном коде

-Целью изобретения является повы. шение надежности преобразователя.

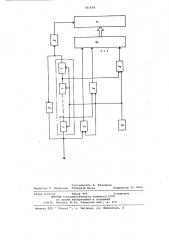

Это достигается тем, что в преобразователь напряжение - код одиночных импульсов, содержащий пороговые блоки и шифратор, введены линия задержки, блок управления, ре.гистр памяти, источник эталонного напряжения, последовательная цепь вычитающих блоков, управляющие входы которых подключены к выходу источника эталонного напряжения, Причем выход последнего вычитающего блока в последовательной цепи вычитающих блоков подключен к входам линии задержки и блока управления, к сигнальному входу каждого вычитающего блока подключен сигнальный вход соответствующего порогового блока, управляющие входы которых соединены с выходом источника эталонного напряжения, а к сигнальному входу первого вычитающего блока, кроме того, подключен выход линии задержки, при этом выход блока управления подключен к управляющему входу регистра памяти, сигнальйый вход которого через шифратор подключен к выходам пороговых бло15 ков.

На чертеже приведена функциональная схема преобразователя напряжение — код одиночных импульсов, Сигнальный вход первого вычитающего блока 1, являющийся входом преобразователя, соединен с выходом линии задержки 2 и с сигнальным входом первого порогового .блока 3, а выход — с сигнальным входом второго порогового блока и с сигнальным входом второго вычитающего блока и т, д. последовательной цепи 4 вычитающих блоков, выход которой соединен с входами линии задержки и

741458, блока управления 5. Причем выходы пороговых блоков через шифратор б соединены с сигнальным входом регистра памяти 7, управляющий вход которого соединен с выходом блока управления, а управляющие входы вычитающих блоков соединены с выходом источника 8 эталонного напряжения.

Преобразователь работает следующим образом.

В первом подцикле преобразования импульс подают на сигнальный вход первого вычитающего блока 1. и одновременно на сигнальный вход первого порогового блока 3, на управляющие входы которых поступает неизмейное эталонное напряжение с выхода источника 8 эталонного напряжения, На выходе вычитающего блока вырабатывается разность между входным импульсом и эталонным напряжением.Эта разность поступает на последующий вычитающий блок и на сигнальный вход следующего порогового блока, где н случае ее превыаения величины неизменного эталонного напряжения вырабатывается импульс стандартной амплитуды и длительности, Шифратор б преобразует параллельный единичный код на выходе пороговых блоков в позиционный двоичный код, Разность с последнего вычитающего блока поступает через линию задержки 2 на вход первого вычитающего блока и выполняется следующий подцикл. Время задержки линии задержки должно превышать максимальную длительность преобразуемых импульсов.

Устройство управления 5 осуществляет с помощью стандартных импулЬсов управления работой регистра памяти: кратковременное хранение и выполнение по разрядной логической операции сложения хранимого результата преобразования предыдущего подцикла преобразования с вводившим результатом преобразования последующего подцикла.

Количество вычитающих блоков последовательной цепи вычитающих блоков определяется, исходя из требуемого времени преобразования

Т а зиА где а — количество подциклов преобразования; время задержки линии задержки.

Тогда общее количество пороговых блоков Й = Ь = ф где N- число уровней квантования, и основной объем аппаратурных затрат т. е. основной объем аппаратурных затрат по сравнению с прототипом уменьшается в 2/а раз, вследствие чего повышается надежность преобраз ов ател я.

Формула из обретения

Преобразователь напряжение — код одиночных импульсов, содержащий пороговые блоки и шифратор, о т л ич ающи и с я тем, что, с целью повышения надежности, в него введены линия задержки, блок управления, регистр памяти, источник эталонного напряжения, последовательная цепь вычитающих блоков, управляющие входы которых подключены к выходу -источника эталонного напря30 жения, причем выход последнего вычитающего блока подключен к входам линии задержки и блока управления к сигнальному входу каждого вычитающего блока последовательной цепи вы35 читающих блоков подключен сигнальный вход соответствующего порогового блока, управляющие входы которых соединены с выходом источника эталонного напряжения,а к сигнальному входу первого вычитающего блока, кроме того, подключен выход линии .задержки, при этом выход блока управления подключен к управляющему входу регистра памяти, сигнальный вход которого через шифратор подключен к выходам пороговых блоков, Источники информации, принятые во внимание при экспертизе

1. Гитис. Преобразователи информации для электронных цифровых вы® числительных устройств., М., Энергия, 1975, с. 314 (прототип).

741458

Составитель A. Кузнецов

Редактор Т. Юрчикова Техред М.Петко

Корректор E. Папп

Заказ 3218/54 Тираж 995 Подписное

gHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4