Коммутирующее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ТЮЛЬСТВУ

Союз Советских

Соцналнстнчесннх

Респубпнк (б!) Дополнительное.к авт, сеид-ву (22) Заявлеио031)578 (21) 2611174/18-21 (51)м. Кл. с присоединением заявки Ио—

Н 03 К 17/02

Государственный комитет

СССР по делам изобретений н открытий (231 Приоритет

Опубликовано 1506.80. Бюллетень Ио 22

Дата опубликования описания 1506.80 (53) УДК 621. 316.

56 (088. 8) (72} Авторы изобретения

A.Е. Пыров и Б.Д. Никифоров

Проектно-конструкторское бюро Главного управлени я локомотивного хоз яйств а Министерств а путей сообщени я (71) Заявитель (54) КОММУТИРУ)0ЩЕЕ УСТРОЙСТВО

Изобретение относится к области автоматики.

Известны коммутирующие устройства, содержащие генератор импульсов, кодОвые преобразователи и ключ (1).Недостаткам известного устройства относится малая информационная. емкость.

Наиболее близким техническим решением к данному является коммутирующее1О устройство, содержащее генератор импульсов, выход которого соединен с информационным входом первого кодового преобразователя и одним из входов ключа, второй вход которого подключен к выходу второго. кодового преобразо- вателя,а выход ключа соединен с выходной шиной (2).К недостаткам известного устройства относится малая информационная емкость.

Целью изобретения является увеличение информационной емкости коммутирующего устройства, Указанная цель достигается за счет того, что в известное коммутирующее устройство дополнительно введены дифференцирующий элемент, блок памяти тактовых импульсов и блок памяти окончания цикла, а также в каждом канале блок памяти интервалов, многостабильный триггер и шифратор, выход второго кодового преобразователя через дифференцирую= щий элемент соединен со входом установки первого кодового преобразова.теля, первый и второй выходы которого подключены соответственно к информационным входам блока памяти тактовых импульсов и блока памяти окончания цикла, один иэ выходов которого соединен с первым входом второго кодового преобразователя, а другой выход подключен ко входу установки блока памяти тактовых импульсов, выход которого соединен со вторым входом второго кодового преобразователя, в каждом кан але выход блока памяти интервалов подключен ко входу у1тановки многостабильного триггера, выход которого соединен со входом шифратора, один иэ выходов которого подключен ко входу блокировки многостабильного триггера, при этом соотствующая группа выходов. первого кодового преобразователя соединена с информационными входами блока памяти интервалов и многостабильного триггера, а выходы блока памяти интервалов н шифрато741463 ра подключены к соответствующей группе входов второго кодового преобразователя,,при этом выход блока памяти тактовых импульсов соединен со входом установки блока памяти интервалов первого канала, другой выход шифратора предыдущего канала соединен со входом установки блока памяти интервалов последующего канала, а другой выход шифратора последнего канала подключен ко входу установки блока памяти окончания

10 цикла.

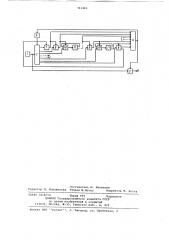

На чертеже представлена функциональная схема коммутирующего устройства.

Она содержит генератор импуль- 15 сов 1, выход которого соединен с информационным входом первого кодового преобразователя 2 и одним из входов ключа 3, второй вход которого подключен к выходу второго кодово- Щ го преобразователя 4, а выход ключа 3 соединен с выходной шиной 5; дифференцирующий элемент б, вход которого соединен с выходом второго кодового преобразователя 4, а выход д подключен ко входу установки первого кодового преобразователя 2, первый и второй выходы которого подключены соответственно к информационным входам блока 7 памяти тактовых импульсов и блока 8 памяти .окончания цикла, один из выходов которого соединен с первым входом второго кодового преобразователя 4, а другой выход подключен ко входу установки блока 7 памяти тактовых импульсов, выход кото. рого соединен со вторым входом второго кодового преобразователя 4; 9блок памяти интервалов, выход которого подключен ко входу установки многостабильного триггера 10, выход 40 которого соединен со входом шифратора .11, один из выходов которого подключен ко входу блокировки многостабильного триггера 10; соответствующая группа выходов первого кодового преобразователя 2 соединена с информационными входами блока 9 памяти интервалов и многостабильного триггера 10, а выходы блока 9 памяти интервалов и шифратора ll под- 5О ключены к соответствукщей группе входов второго кодового реобразователя 4. Выход блока 7 памяти тактовых импульсов соединен со входом установки блока 9 памяти интервалов .

nepSoro канала, другой выход шифратора ll предыдущего канала соединен со входом установки блока 9 памяти интервалов последующего . канала, а другой выход шифратора 11 последнего канала подключен ко входу 66 установки блока 8 памяти окончания цикла.

Коммутирующее устройство работает следующим образом. Сигнал от генератора импульсов l поступает на Я вход кодового преобразователя 2, который формирует сигналы через заданное количества импульсов генератора 1; Первый сигнал, сформированный кодовым преобразователем 2, является сигналом окончания тактового импульса и он поступает на основной вход и запоминается в блоке 7 памяти тактовых импульсов. Включейие блока 7 памяти тактовых импульсов приводит к появлению сигнала на выходе кодового преобразователя 4, сигнал которого поступает на ключ 3 и запирает его, тем самым организуя на выходе ключа 3 интервал, Кроме того, сигнал с выхода кодового преобразователя 4 поступает на дифференцирующий элемент 6, который преобразует сигнал в дельта им пульс. Дельта импульс стирает первичную информацию в кодовом преобразователе 2., который после этого начинает формировать сигнал первого интервала. При наличии информации в блоке 7 памяти тактовых импульсов снимается запрет с блока 9 памяти интервалов. После этого, как на выходе кодового преобразователя 2 сформируется интервал между тактовым импульсом и первым информационным импульсом, включится блок 9 памяти интервалов, который в свою очерець снимет запрет с многостабильного триггера 10,а.также даст сигнал на вход кодового преобразователя 4, что в свою очередь вызовет снятие сигнала с выхода кодового преобразователя

4. Это вызовет включение ключа 3, на выходе которого появится сигнал от генератора импульсов 1; кроме того, снятие сигнала с выхода кодового преобразователя 4 также воспринимается дифференцирующим элементом 6 и дельта импульс с его выхода вновь приве— дет кодовый преобразователь 2 в исходное состояние, который после окончания действия дельта импульса начнет формировать первый информационный импульс, Первый информационный импульс может- содержать в себе rn„ èíформаций в зависимости от количества каскадов многостабильного тригге. ра 10,. Если первый информационный им-пульс несет в себе одну информацию, то после первого импульса на выходе кодового. преобфйзователя 2 включится первый каскад многостабильного триггера 10 и через шифратор 11 многостабильного триггера 10,блокируется и снимет запрет с блока 9 памяти интервалов. Если первый информационный импульс несет в себе }и информаций, . то на выходе кодового преобразователя 2 будет Ич импульсов, следующих один за другим через заданный интервал времени, которые включают поочередно каждый каскад многостабильного триггера 10 и при включении ъ каскада многостабильного триггера 10 он

741463 себя остановит через шифратор 11.

Наличие сигнала на выходе шифратора 11 вызовет появление сигнала на выходе кодового преобразователя 4, который, в свою очередь, выключит ключ 3; тем самым-начнется на выходе ключа 3 формирование второго интервала и вызовет появление дельта импульса на выходе дифференцирующего элемента б. Дельта импульс приводит кодовый преобразователь 2 в исходное состояние, который начинает формировать второй интервал между первым и вторым информационными импуль- сами. После окончания формирования и-го информационного импульса сигнал с выхода шифратора 11 оста15 навливает многостабильный триггер 10, снимает запрет с блока 8 памяти окончания цикла и воздействует на коцовый преобразователь 4, который рабо-. тает так же, как и при воздействии на него сигнала от шифратора 11. Следовательно, кодовый преобразователь

2 начнет формировать последний интервал, извещающий об окончании кодового цикла. Как только данный сигнал 25 появится на выходе кодового преобразователя 2, он включит блок 8 памяти окончания цикла, который в свою очередь воздействует на кодовый преобразователь 4 и сигнал с его вы- ЗО хода от крыв ает ключ 3, н а выходе которого начнет формироваться тактовый импульс, и воздействует через дифференцирующий элемент б на кодовый преобразователь 2, приводит его в исходное состояние и он начнет формировать тактовый импульс. Кроме того, сигнал с выхода блока 8 памяти окончания цикла стирает информацию в блоке 7 памяти тактовых импульсов, отсутствие информации в котором приводит к стиранию информации в блоке 9 памяти интервалов, а отсутствие информации в блоке 9 памяти интервалов приводит к сбросу в исходное состояние многостабильного триггера 10. Отсутствие сигнала на выходе шифратора 11 приводит к стиранию информации в следующем блоке 9 памяти интервалов. Отсутствие сигнала на выхода шифратора 11 приводит к стиранию информации в блоке .8 памяти окончайия.цикла и коммутирующее устройство приходит в исходное состояние.

Формула изобретения

Коммутирующее устройство, содержащее генератор импульсов, выход () которого соединен с информационным входом первого кодового преобразователя и одним нз входов ключа, второй вход которого подключен к выходу второго кодового преобразователя, а выход ключа соединен с выхоцной шиной, о т л и ч а ю щ е е с я тем, что с целью увеличения информационной емкости, в него. введены дифференцирующий элемент, блок памяти тактовых импульсов и блок памяти окончания цикла, а также в каждом канале блок памяти интервалов, многостабильный триггер и шифратор, выход второго кодового преобразователя через дифференцирующий элемент соединен со входом установки первого кодового преобразователя, пер" вый и второй выходы которого подключены соответственно к информационным входам блока памяти тактовых импульсов и блока памяти окончания цикла, один из выходов которого соединен с йервь|м входом второго кодового преобразователя, а другой выход подключен ко входу установки блока памяти тактовых импульсов, выход которого соединен со вторым входом второго кодового преобразователя, в каждом канале выход блока памяти интервалов подключен ко входу установки многостабильного триггера, выход которого соединен со входом шифратора, один из выходов которого подключен ко входу блокировки многостабильного триггера, при этом соответствующая группа выходов первого кодового преобразователя соединена с информационными входами блока памяти интервалов и многостабильного триггера, а выходы блока памяти интервалов и шифратора под= ключены к соответствующей группе входов второго кодового преобразователя, при этом выход блока памяти тактовых импульсов соединен со вхоцом установки блока памяти интервалов первого канала, другой выход шифратора. предыдущего канала соецинен со входом установки блОка памяти интервалов последующего канала, а другой выход шифратора последнего канала подключен ко входу установки блока памяти окончания цикла.

Источники информации, принятые во внимание при экспертизе

1. Леонов A.À. Техническое содержание автоматической локомотивной сигнализации и автостопов,М., Транспорт, 1974, с. 41, фиг. 2.

2, Авторское свидетельство СССР по заявке 9 2434953/18-21, кл, Н 03 К 17/02, 15.06.77(прототип).

741463

Составитель IO Васильев

Редактор Л, Новожилова Техред М.Петко Корректор М, Коста

Заказ 3218/54 Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП Патент, г. Ужгород, ул, Проектная, 4