Дешифратор адреса

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ . К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«i>741470 (61) Дополнительное к авт. свид-ву (22) Заявлено 021078 (21) 2669099/18-21 с присоединением заявки ¹ (23) Приоритет

Опубликовано 1506.80. Бюллетень № 22

Дата опубликования описания150680 (51}М. Кл.

Н 03 К 17/60

Государственный комитет

СССР по делам изобретений и открытий (53} УДК 621. З82 (088.8) С.A. Еремин, A.È ° Стоянов, В.A. Сухоруков и В.C. Хорошунов (72) Авторы изобретения (71) Заявитель (54) ДЕШИФРАТОР АДРЕСА

Устройство относится к импульсной и вычислительной технике и может быть использовано при построении запоминающих устройств на МДП-транзис- 5 торах.

Известен дешифратор адреса, каждый каскад которого содержит входные

МДП-транзисторы с индуцированным каналом и нагруэочный МДП-транзистор со встроенным каналом, причем затворы входных транзисторов и их истоки подключены к входным шинам и общей шине соответственно, стоки входных транзисторов объединены и

15 соединены с истоком нагруэочного транзистора и входной шиной устройства, сток нагрузочного транзистора подключен к шине. источника питания (1) .

К недостаткам известного устройства следует отнести значительную потребляемую мощность и низкую технологичность, обусловленную Наличием транзисторов как с индуцированным, так и со встроенным каналами °

По технической сущности и схемной реализации наиболее близким к описываемому является дешифратор адреса, содержащий в каждом каскаде входные МДП-транзисторы, нагрузочный МДП-транзистор и МДП-транзистор связи, причем затворы и истоки входных транзисторов подключены к входным шинам дешифратора и общей шине соответственно, стоки входных тран— зисторов объединены и подключены к истоку нагрузочного транзистора и стоку транзистора связи, сток нагрузочного транзистора соединен с ии— ной источника питания (2) .

К недостатку такого устройства следует отнести малую надежность функционирования, что обусловлено высокой сложностью управления его работой.

В целях повышения надежности функционирования в дешифратор адреса, содержащий в каждом каскаде входные МДП-транзисторы, нагрузочный

МДП-транзистор и МДП-транзистор связи, причем затворы и истоки входных транзисторов подключены к входным шинам дешифратора и общей шине соответственно, стоки входных транзисторов объединены и подключены к истоку нагрузочного транзистора и стоку транзистора связи, сток на741470 грузочного транзистора соединен с шиной источника питания, введены конденсатор, дополнительные первый и второй МДП-транзисторы и в каждый каскад третий дополнительный

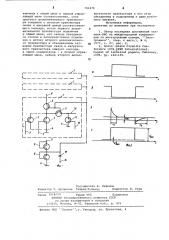

МДП-транзистор, Причем исток и затвор третьего дополнительного транзистора подключены к.общей шине и первой управляющей шине соответственно, сток третьего дополнительного тран, зистора соединен с истоком транзистора связи и выходной шиной соответствующего каскада,. исток первого дополнительного транзистора подклю.чен к общей шине, его затвор объединен со стоком и непосредственно подключен к истоку второго допол- 15 нительного транзистора и объединенным затворам транзистора связи и нагруэочного транзистора каждого каскада, а через конденсатор — к второй управляющей щине, затвор второго до- 2Q полнительного транзистора и его сток объединены и подключены к шине источника питания, На фиг. 1 изображена принципиальная схема описываемого дешифратора ад- g5 реса; на фиг. 2 приведены временные диаграммы его работы, Дешифратор адреса .содержит в каждом из N каскадов 1 N 2 входных транзисторов 2, стоки которых объединены с истоком нагрузочных транзисторов 3, Истоки транзисторов 2 подключены к общей шине 4, а затворы — к входным шинам 8. Сток нагрузочного транзистора подсоединен к шине источника питания б, его затвор объединен с затвором транзистора 7 связи, с затвором и стоком первого дополнительного транзистора 8 и с истоком второго дополнительного транзистора 9, образующих делитель напряжения, а также с первым 40 выводом конденсатора 10. Затвор и сток транзистора 9 присоединены к шине источника питания 6. Исток транзистора связи объединен со стоком третьего дополнительного транзистора 11 и присоединен к выходной шине

12. Затвор транзистора 11 подключен к первой управляющей шине 13,- а исток — к общей шине 4, к которой подключен также исток транзистора 8, Второй вывод конденсатора 10 подключен к второй управляющей шине

14. При и=пользовании описываемого дешифратора для построения запоминающих устройств в качестве первой и втофой управляющих шин,.используются шинй выбора кристалла и инверсная шина выбора кристалла соответственно, Дешифратор адреса работает сле,цующим образом. Транзисторы 8 и 9 образуют делитель напряжения пита- 69 ния, формирующий в средней точке напряжение 0О„=0„„р,где U„ - пороговое напряжейие транзисторов. Если на управляющих шинах 14 и 13 присутствуют cHríçëû ниэкОГО и ВысОкО- $5 го уровней соответственно (фиг. 2а и б), то транзисторы 3 и 7 заперты, транзистор 11 открыт и на выходной шине 12 каскада — низкий уровень напряжения.- Потребление каскадом мощности от источника питания б отсутствует.

При поступлении на шины 14 и 13 высокого и низкого уровней напряжения соответственно транзистор 11 закрывается. Напряжение на затворах транзисторов 3 и 7 скачкообразно возрастает на величину амплитуды сигнала на шине 14 (фиг. 2в), и открываются транзисторы 3 и 7.

Когда все транзисторы 2 заперты на выходной шине 12 каскада формируется высокий уровень напряжения (фиг, 2 r — сплошная линия). Через промежуток времени (длительность которого определяется;значением емкости конденсатора 10 и значением крутизны транзистора 8, напряжение на затворах транзисторов

3 и 7 уменьшается до величины 0„ „„ транзисторы запираются, что обеспечивает сохранение на выходной шине высокого уровня напряжения.

Когда хотя бы один иэ входных транзисторов открыт, на выходной шине 12 формируется и сохраняется низкий уровень напряжения (фиг. 2гпунктирная линия), Так же как и в первом случае через промежуток времени 1 входную адресную информацию можно менять — напряжение на выходной шине сохраняется.

Через время т, после снятия сигнала высокого уровня с шины 14 дешифратор адреса готов к повторному циклу работы., Простота управления и незначительная мощность, потребляемая в статическом состоянии, обусловливают высокую надежность функционирования дешифратора.

Формула изобретения дешифратор адреса, содержащий в каждом каскаде .входные МДП-транзисторы, нагрузочный МДП-транзистор и

МДП-транзистор связи, причем затворы и истоки входных транзисторов подо ключены к входным шинам дешифратора и общей шине соответственно, стоки входных транзисторов объединены и подключены к истоку нагруз очного транзистора и стоку транзистора связи, сток нагруэочного транзистора соединен с шиной источника питания, отличающийся тем, что, с целью повышения надежности функционирования, в него Введены конденсатор, дополнительные первый и второй МДП-транзисторы и в каждый каскад третий дополнительный МДП-транзистор, причем исток и затвор третьего дополнительного транзистора под741470

15

Составитель В, Нефедов

Редактор Т. Юрчикова Техред М.Петко Корректор Н. Стец г

Заказ Тираж 995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/Б

Филиал ППП Патент,г. Ужгород, ул. Проектная, 4 ключены к общей шине и первой управляющей шине соответственно, сток третьего дополнительного транзистора соединен с истоком транзистора связи и выходной шиной соответствующего каскада, исток первого дополнительного транзистора подключен к общей шине, его затвор объединен со стоком и непосредственно подключен к истоку второго дополнительного транзистора и объединенным затвором транзистора связи и нагрузочного транзистора каждого каскада, а через конденсатор — к второй управляющей шине, затвор второго дополнительного транзистора и его сток объединены и подключены к шине источника питания.

Источники информации, принятые во внимание при экспертизе

1 . Обзор последних достижений техники БИС на международной конференции по интегралЬным схемам. Электроника, (пер. с англ.), 9 4, 1977, с. 27, рис. 2.

2. SoIid -State Ciranits Conference 1978, XEEE InternationaI, Dagest of technicaI papers, February, 1978, рр. 104-105.