Устройство поэлементной синхронизации и регенерации

Иллюстрации

Показать всеРеферат

< >741479

Союз Советскнх

Соцнапнстнческнх

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к акт. свнл-ву (22) Заявлено 07.04.78 (21) 2601826/18-09 с присоединением заявки ¹ (23) П рипритет (51)M. Кл.

Н 04 L 7/08

Гооударстввнный комитет но делам нэобретений н открытий

Опубликовано 15.06.80. Бюллетень ¹ 22

Дата опубликования описания 15.06.80 (53) УДК621З94, .662 (088.8) (72) Авторы изобретения

Н. Н. Дунева,.М. С. Подлубный и В. Л. Хаэан (71) Заявитель (54) УСТРОЙСТВО ПОЭЛЕМЕНТНОЙ СИНХРОНИЗАЦИИ

И РЕГЕНЕРАЦИИ

Изобретение относится к радиосвязи и может использоваться в приемной аппаратуре на узлах ретрансляции радиосигналов и приемных центрах, где ведется одновременная работа с большим числом корреспондентов.

Известно устройство поэлементной синхрониза-5 ции и регенерации, содержащее последовательно соединенные определитель нулевых переходов сигнала, анализатор, а также формирователь стробирующих импульсов, формирователь выход. ных сигналов и выходной решающий блок (1). то

Однако известное устройство имеет недостаточную помехозащищенность.

Цель изобретения — повышение помехозашищенн ости.

Для этого в устройтство лоэлементной синхронизации и регенерации, содержащее последовательно соединенные определитель нулевых переходов сигнала, анализатор, а также формирователь стробируюших импульсов, формирователь го выходных сигналов и выходной решающий блок, введены последовательно соединеннь е блок временного уплотнения, коммутатор и блок памяти, последовательно соединенные блок

2 управления, распределитель импульсов сброса:. и блок запоминания фазы, а также распредели .тель сигналов, при этом первый и второй выходы блока памяти подключены к соответствующим входам определителя нулевых переходов. сигнала, а третий выход — к входам формирователя выходных сигналов через последовательно соединенные выходной решающий блок н распределитель сигналов, выходы анализатора подключены к соответствующим входам распределителя импульсов сброса, выходы блока запоминания фазы подключены к входам формирователя стробирующих импульсов, выход которого подключен к другому входу выходного решающего блока, а выходы блока управления подключены к соответствующим входам блока временного уплотнения, блока памяти и распределителя сигнапов, причем на управляющие входы блока управления и блока запоминания фазы подан опорный сигнал, а на управляющий вход распределителя импульсов сброса подан сигнал "сброс памяти".

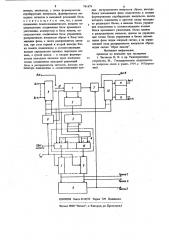

На чертеже приведена структурная электрическая схема предложенного устройства.

741479

3

Устройство поэлементной синхронизации и регенерации содержит блок 1 памяти, определитель 2 нулевых переходов сигнала, анализатор 3, распределитель 4 импульсов сброса, блок,5 запоминания фазы, формирователь б, стробирующих импульсов, выходной решающий блок 7, блок 8 управления, блок 9 временного уплотнения, распределитель 10 сигналов, формирователь 11 выходных сигналов, коммутатор 12. so

Устройство работает следующим образом, При поступлении на вход сигнала, несущего информацию, в соответствии с видом комбинавии, между парными отводами блока 1 памяти оказываютСя переходы поступивших посылок, ts при этом на выходе определителя 2 нулевых переходов в соответствующие моменты времени появляются сигналы, которые поступают на вход анализатора 3 с оценкой условий связи, осуществляющего подсчет количества переходов 20 входного сигнала, расположенных в местах, кратных ,длительности элементарной посылки, на отрезке времени, достаточном для надежного вхождения в синхрониэм, и, кроме того, сравнение подсчитанного количества нулевых переходов соответствующих границам элементарных посылок с некоторым пороговым значением, а также анализ наличия неискаженной просечками зоны в середине кахсдой элементарной посылки. В результате анализатор 3 формирует сигнал оценки на 3Q одной из К-шин, которые соединены со входами распределителя 4 импульсов сброса. Распределитель 4 импульсов сброса представляет собой совокупность элементов памяти 13 оценок качества, одни входы которых объеди- З5 иены и подключены к выходным шинам анализатора 3, а другие также объединены и соединены с выходами блока 8 управления. Указанный блок 8 управляет очередностью подключения: корреспондентов на вход блока 1 па- 4о мяти; сигналов полученных оценок качества условий связи к соответствующим входам элементов памяти 13 оценок качества; сигнала выходного решающего блока 7 ко входам формирователей 11 выходных сигналов. 45

Кроме того, предусматривается внешний сброс памяти распределителя 4 импульсов через промежутки времени, не превышающие

I время нахождения стробирующего импульса в допустимой зоне посылки без подстройки.

Формирование сигналов сброса в элементах памяти 13 оценок качества производится по приоритету лучшей оценки с запретом прохожде ния на выход сигналов с худшей оценкой. Это позволяет существенно снизить вероятность потери синхронизации при ухудшении условий связи. Элементы памяти 13 оценок качества формируют сигналы, которые осуществляют

4 установку начальной фазы блока 5 запоминания фазы, на сигнальные входы которых подается сигнал опорной частоты fpn. В результате преобразования частоты акоп на выходе блока 5 формируются сигналы, соответствующие моментам тактовой синхронизации, по времени при. ходящиеся в центр элементарной посылки, и повторяющихся с периодом, равным номинальной длительности посылки. Формирователь 6 стробирующих импульсов собирает сигналы с выхода блока 5. Собирательный сигнал тактовой синхронизации подается на вход выходного решающего блока 7, куда одновременно поступает сигнал с выхода блока 1 памяти и где осуществляется принятие решения о переданной посылке методом стробирования посылки в центре. Сигнал с выходного решающего блока 7 поступает на вход распределителя 10 сигналов, где происходит преобразование уплотненного во времени сигнала от и-корреспондентов в совокупность выходных сигналов для каждого из и-корреспондентов отдельно. Далее, сигналы поступают на входы формирователя 11 выходных сигналов, где осуществляется регенерация элементарной посылки до ее стандартной длительности. Введение в предложенное устройство совокупности указанных технических средств выгодно отличает его от прототипа и аналогов, так как позволяет существенно снизить схемные затраты, обеспечивая значительный выигрыш в габаритах устройства и экономию материальных средств при его производстве, повышает пропускную способность канала связи эа счет устранения потерь информации в процессе вхождения в синхронизм в начале сеанса и после длительных перерывов в связи, а также при приеме коротких сообщений повышает помехоустойчивость схемы при передаче длительных сигналов одной полярности, устраняет влияние помех на точность синхронизации при ухудшении условий связи.

Макет, включающий в себя все основные узлы описанного устройства поэлементной синхронизации и регенерации, был разработан и испытан в лабораторных условиях и на реальной трассе.

На реальной коротковолновой трассе в режиме приема коротких телеграмм объемом в 20 бит были получены хорошие результаты, принци недостижимые прототипом.

Формула изобретения

Устройство позлементной синхронизации и регенерации, содержащее последовательно соединенные определитель нулевых переходов

5 74 сигнала, анализатор, а также формирователь стробирующих импульсов, формирователь выходных сигналов и выходной решающий блок, о т л и ч а и ш е е с я тем, что, с целью повышения помехозащищенности, введены последовательно соединенные блок временного уплотнения, коммутатор и блок памяти, последовательно соединенные блок управления, распределитель импульсов сброса и блок запоминания фазы, а также распределитель сигналов, при этом первый и второй выходы блока памяти подключены к соответствующим входам определителя нулевых переходов сигнала, а третий выход — к входам формирователя выходных сигналов через последовательно соединенные выходной решающий блок и распределитель сигналов, выходы. анализатора подключены к соответствующим вхо1479 6 дам распределителя импульсов сброса, выходы блока запоминания фазы подключены к входам формирователя стробнрующнх импульсов, выход которого подключен к другому входу выходного решающего блока, а выходы блока управления подключены к соответствующим входам блока временного уплотнения, блока памяти и распределителя сигналов, причем на управляющие входы блока управления и блока запоминания фазы подан опорный сигнал, а на управляющий вход распределителя импульсов сброса подан сигнал "сброс памяти".

Источники информации, принятые во внимание при экспертизе

1. Чистяков Н. И. и др. Радиопрнемные устройства. М., Государственное издательство по вопросам связи и радио, 1959,с. 147(прототип) .

ЦНИИПИ, Заказ 3219/55 Тираж 729 Подписное

Филиал ППП Патент", г. Ужгород, ул. Проектная,4