Вычислительное устройство

Иллюстрации

Показать всеРеферат

Союз Советскмх

Соцмалмстмческмх

Республмк

ОП ИКАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

?42930

Ф

/ (61) Дополнительное к авт. свмд-ву— (22) Заявлено 09.01,78 (2() 256 7896/18-24 с присоединением заявки,%— (23) Приормтет—

Олубликовано25.06.80. Бюллетень,% 23 йата опубликования описания30.06.80 (5! )М. Кл.

G 06 F 7/38

Гееудерстееииый комитет

СССР ив лелем иэооретеиий и открытий (5З) уды 681.325 (088.8) (j2) Авторы изобретения

В. Б. Дудыкевич и В. H. Максимович (7I) Заявитель (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО

УстрОйство ОтнОситсЯ к вычислительной технике и может бьаь использовано в уст ройствах обработки информации.

И зве стны вычислительные устройств а, предназначенные аля вычисления функции вида

У-К„Х"+ -+ К Х+КО Г11 и $23

Однако они являются довольно сложными по своему выполнению.

Наиболее близким к предлагаемому по технической сущности является вычислительное устройство, содержащее четыре счетчика, регистр, ase группы элементов

И, блок памяти, два дешифратора, nsa элемента задержки, три элемента И, элемент

ИЛИ и генератор тактовых импульсов (3)

Недостатками этого устройства являются большое количесгво оборудования и низкое быстроцействие, обусловленное наличием делителя частоты, генератора так20 товых импульсов в цели умножения устройства

Бель изобретения - упрощение устрой ства и повышение его быстродействия.

Поставленная цель достигается тем, что вычислительное устройство, содержащее счетчики, блок памяти, генератор тактовых импульсов, дешифратор, элементы

И, ИЛИ и задержки, причем выход блока памяти подключен ко входам первого счетчика, выходы которого подключены ко входам дешифратора, выход которого соединен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выходы разрядов второго счетчика подключены к первым вхоаам соответствующих элементов И первой группы, содержит триггер и два блока вычитания, причем выход генератора тактовой частоты подключен ко второму входу первого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выходы первого и второго элеменгов ИЛИ поттключены ко входам первого и второго счетчиков соответственно, выхоаы разрядов первого счетчика соединены с первыми входами соответствующих элементов

7 293О

ЭО

И второй группы, выходы которых подклкчены ко входам третьего ИЛИ, выходы эпементов И первой группы подкпк»чоны ко входам четвертого эпемента ИЛИ, первый и второй входы первого блока вь читания соединены с выходами первого и третьего элемента ИЛИ соответственно, а первый и второй входы второго блока вычитанил — с выходаМИ второго и ЧЕтвертого элементов ИЛИ соответственно, выход цешифратора подключен к счетному входу триггера и, через элемент задержки - ко ,входу блока памяти, нулевой выход триг гера подключен к первым входам второго и третьего элементов И и первому управляющему входу второго счетчика, второй управляющий вход которого соединен с единичным выходом триггера, вторые входы второго и третьего элементов И подкпючены к выходам первого и второго блоков вычитания соответственно, а выходыко вторым входам соответственно первого и второго эпементов ИЛИ, второй вход каха ого элемента И первой группы (ь=1,..., tl, где ((.-разрядность счетчиков) подключена

1 к вы соду (t1 — (.+1)-ro разряда первого счетчика, а второй вход каждого (. -ro элемента И второй группы подключен к

\ выходу (П. — (-+1)-го разряда второго счетчика.

Потенциапьные входы каждого из элементов 4 И группы подкпюче п.t к епинич ным выходам одного из триггеров реверсивного счетчика 2, а импульсные входы соединены С единичными выходами одного из триггеров счетчика 1, причем ео- ° пи один из его входов подкпючен к триг геру младшего ркзряда счетчика 2, то второй вход подключен к триггеру старше10 го разряда счетчика 1 и наоборот. Имцупьсы появляются на выходе того элемента 4

И группы, который подключен к находяще— муся в единичном состоянии триггеру счетчика 2 и переходящему из нулевого в еди- . ничное состояние триггеру счетчика 1.

Средняя частота f6спедования импульсов на выходе элемента 6 ИЛИ определяется чаототой f иHмMп у л0ьbсoоoв, поступающих на вход счетчика 1,. и числОм Й (Е) 1 находящимся в реверсивном счетчике 2 и равнк где Ч вЂ” коэффициент пересчета счетчи25 ков1 и2.

На выходе схемы 10 вычитания частота импульсов равна разности частот, поотупающих на ее входы: (о — В- 4 (4

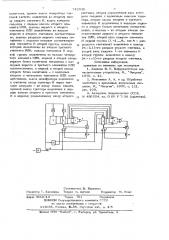

На чертеже представпена функционапьная схема устройства.

Оно содержит счетчик 1, реверсивный счетчик 2, блок 3 памяти, группы элементов 4 и 5 И, эпементы 6-9 ИЛИ, блоки 10 и 11 вычитания, эпементы 12-14

И, дешифратор 15, элемент 16 задержки, триггер 17, генератор 18 тактовых импульсов.

Работа устройства на примере вычиопения многочпена дпя случая й. 4.

Предварительно в счетчик 1 заносится значение О.ц, в реверспвный счетчик 2 .значение Х, а в ячейки блока 3 памяти— значения коэффициентов 0- - О.< в дополнительном коде и значение Х. Триггер

17 устанавпивается и "О", при этом элементы 12 и 13 И подготавпиваются к открытию по первым входам, а реверсивный счетчик 2 устанавливается в режим вычитания.

Импульсы с генератора 18, частота спедования которых fT, поступают на входы элементов 8 и 9 ИЛИ. На второй вход элемента 8 ИЛИ поступают импульсы с выхода блока 10 вычитания, проходящие через элемент 12 И, частота спедования к торых f ip .

Частота импульсов на выходе элемента

8 ИЛИ равна: (3)

Tчитывая эти выражения, получим т N

N (t) Аналогично, учитывая вырахиния

Я Ng(t) и (5) 3 fg Ф (6) 40

fò + (4, (7) 45 где И((Ц число, содержащееся в счетчи1 ке 1, получим

50 1т N ((, ()

Частота 1 g u f g связана с чиспами, содержащимися в счетчиках 1 и 2, соотношениями:

У= }(+." х rA (18)

Nr„„é„, д йх dNr.(t)

N (Ц й,(t) 5 7 (2930 6

Подставляя выражения (9} и (1О) со- В общем случае в счетчик 1 предваответственно в (4) и (8) получим рительно заносится,значе((ие A rr, rr

4,N (t) f. Nm (1Ц реверсивный счетчик 2 — значение Х, а и (c)

1 в ячейке блока 3 памяти — значения коz. эффипиентов Й -r- Q.(r в дополнительном.

z, 12) ккоде и значение Х .

dt Ni(t результирующее выражение в общем разделив уравнение (11) на уравнение случае примет вид . (12) и произведя разделение переменны, получим у й;((.," d Ni((.) к N (t) a„N g(t) (14} ипи 25 у Х O.(r

N1 (15)

После этого, через промежуток времени 1- который определяется элементом 16 задержки, число и в дополнительном коде переписывается с блока 3 памяти в счетчик 1, Дешифратор 15 перебрасывает трщ гер 17 в единичное положение, при этом элементы 12 и 13 И закрываются. а реверсивный счетчик 2 устанавливается в режим суммирования. Импульсы с генератора 18 через открытый элемент 14 И поступают на счетчики 1 и 2.

За время прошедшее с момента поступления первого импульса на счетчик 1, до момента переполнения счетчика 1, при котором дешифратор 15 закрывает элемент

14 И, в реверсивный счетчик 2 поступает а, импул

После этого число, записанное в ревер- 45 сивном счетчике 2, равно

У = м + а. (16) х И-ч

Дальше процесс вычисления повторяется в аналогичном порядке, причем значения чисел переписываются с блока 3 памяти s счетчик 1 в следующем порядке

Х Q, Х Cl<, Х, Юз . В результате в реверсивном счетчике 2 содержится число у= н-х" + х + х — х+а . — цч + з з. + о (17) 50

В момент переполнения счетчика 1 дешифратор 15 закроет элемент 14 И. При 15 этом в реверсивном счетчике 2 записывается число У, Проинтегрировав выражение (13), подставив пределы изменения переменных, получим 20

Таким образом, при включении в состав устройства реверсивного счетчика, трех элементов ИЛИ, двух блоков вычитания и триггера и введении новых связей между элементами из состава вычислительного устройства исключается три счетчика, регист р, дешифратор и элемент задержки, чем достигается упрощение устройства по сравнению с известным.

В известном устройстве- счетчик 4 устанавливается в О через промежуток времени Г(= Т„, 0.„Х, где т — период импульсов тактового генератора, а

0-r. — число, содержащееся в этом счеп чике. В предлагаемом устройстве в режиме суммирования счетчик 1 устанавливается в "О" через промежуток времени P =7 ° д,;„, . где Qr. — число, содержащееся в этом счетчике. В режиме умножения промежуток времени, необходимый для установления счетчика 1 в О, меньше Т, так как частота импульсов, поступающих на счетчик 1 больше К

С учетом вышесказанного, быстродействие предлагаемого устройства выше быстродействия известного. фо рмул а из об ретения

Вычислительное устройство, содержащее счетчик, блок памяти, генератор тактовых импульсов, дещифратор, элементы

И, ИЛИ и задерыси, причем выход блока памяти подключен ко входам первого счетчика, . выходы которого подключены ко входам дешифратора, выход которого сое динен с первым входом первого элемента

И, выход которого подключен к первому входу первого элемента ИЛИ, выходы разрядов второго счетчика подключены к ггервым входам соответствующих элементов

И первой группы, о т л и ч а ю щ е е— сятем,,что,,с целью упрощения устройства и повышения его быстродейстаия, усч ройство содержит триггер и два блока

7429 вычитания, причем выход генератора тактовой часготь| подключен ко второму входу первого элемента И, выхоп которого соединен с первым входом второго але» меита HfIH, выходы первого и второго алемептов ИЛИ подключены ко входам первого и второго счетчиков соответсгвенно, выхопы разрядов первого счетчика соединены с первыми входами сооIветствующих элементов И второй группы, выходы которых подключены ко вхопам третьего элемента ИЛИ, выходы алементов И перво группы подключены ко входам четверто1"о элемента ИЛИ, первый и второй вхопы первого блока вычитания соединены с выходами первого и третьего алементов ИЛИ соответственно, а первый и второй входы второго блока вычитания - с выходами второго и четвертого алементов ИЛИ соот ветственно, выход дешифратора подключен к счетному входу триггера И через алемент задержки — ко входу блока памяти, нулевой выход триггера подключен к первЫм входам второго и третьего алементов

И и первому управляющему входу второго

30 H счетчика, второй управляющий вход которого соединен с епиничным выходом триг гера, вторые входы второго и третьего элементов И подключены к выходам первого и второго блоков вычитания соответс венно, а выходы — ко. вторым вхопам соответственно первого и второго алементов ИЛИ, второй вход каждого алемента

И первой группы (4 =1....t1, me и. - разрядносгь счетчиков) подключен к выходу (h.- +1)-го разряда первого счетчика, а второй вход каждого ь-го алемента И второй группы подключен к выходу (и. — к+1)-го разряпа второго счетчика.

Исючники информации, принятые во внимание при экспертизе

1. Данчеев В. П. 11ифрочастотные вычислительные устройства. М., "Энергия", 1976, с. 42.

2, Мельников A. А. и др. Обработка частотных и временных импульсных сигналов. М., Энергия", 1976, с. 121, рис. 109.

3. Авторское свидетельство СССР, М 496554, кл. G 06 Р 7/38 (прототип).

Составитель В, Березкин

Редактор Т. Киселева Техреп О. Легеэа Корректор М. Пожо

Заказ 3618/14 Тираж 751 Подписное

H%HHH Государственного комитета СССР по целом изобретений и сткрьг«яй

113035, Москва, Ж-35, Раущская наэ„, д. 4/5 филиал ППП Патент", г. Ужгород, ул. Проектная, 4