Устройство для решения дифференциальных уравнений в частных производных

Иллюстрации

Показать всеРеферат

Союз Советски

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ р>742946 (6! ) Дополнительное к авт. свид-ву (22) Заявлено 090178 (21) 2568681/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 250680. Бюллетень № 23

Дата опубликования описания 250680 (51)M. Кл.

G 06 F 15/32

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.14 (088.8) (72) Авторы изобретения

А.Г. Тищенко и Н.Ф. Купчинов (71) Заявитель

Таганрогский радиотехнический институт им. В.Д. Калмыкова (54 ) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИИ1ЬНЫХ

УРАВНЕНИИ В ЧАСТНЫХ ПРОИЗВОДНЫХ

Изобретение относится к вычислительной технике и может быть использовано при конструировании и разработке специалиэирова»ных устройств, предназначенных для решения дифференциальных уравнений в частных производных.

Известно устройство, основанное на принципе разрядно-аналоговой обра- 0 ботки информации, состоящее иэ разрядно-логической матрицы, построенной на вентильных схемах, на выходных шинах которой выдаются последовательности импульсов, соответствующие парным произведениям разрядов чисел, поступающих на входы реверсивного сумматора, на выходе которого вырабатывается решение конечно-разностного уравнения (11 .

Недостатками известного устройства являются большой объем оборудования, связанный, например, с необходимостью использования 2„-входных сумматоров для »-разрядных чисел трудности автоматизации процесса решения, связанные с выработкой напряжений, управляющих разрядно-логической матрицей; трудности в разработке математического обеспечения, связанные с проблемамн получения разрядных уравнений, отличающийся от исходных уравнений конечно-разностных.

Наиболее близким к .изобретению по технической сущности является устройство, содержащее блок ввода, соединенный с сумматором, блок умножения, два последовательно-паралдельных регистра, соединенных выходами с блоком умножения и блоки шаговой коммутации, входы которых подключены к блоку умножения, соединенному с сумматором, выход которого соединен со входом одного из регистров. Ука.занное устройство содержит блоки, которые позволяют хранить два значения сеточной функции на предыдущем временном слое и на данном вы исляеемом, а также умножить эти значения на необходимые коэффициенты в блоках умножения, что дает возможность решать уравнение теплопроводности (2) .

Недостатком устройства является то, что точность решения, реализуемая устройством, не превышает второго порядка точности при равномерной сетке и первого порядка при неравномерной сетке.

42946

Цель изобретения — повышение точ ности работы устройста.

Поставленная цель достигается тем, что в устройство для решения дифференциальных уравнений в частных производных, содержащее регистры, блок умножения, сумматор, коммутатор, прИчем выход первого регистра соединен с первым входом блока умножения, выХод которого соединен со входом сумматора, выход сумматора подключен к одному из входов второго регистра, выход которого соединен с первыми входами коммутатора и третьего реги@тра, выход которого соединен са вторым входом блока умножения, вход первого регистра и вторые входы 15 второго и третьего регистров соединены с информационным входом устройства,третьи входы второго и третьег регистров и второй вход коммутатора подключены к управляю- 20 щему входу устройстна, выход коммутатора является информационным выходом устройства, нведен блок вычисления моментон функции, вход которого соединен с выходом д5 второго регистра, а выход блока нычиоления моментов Функции подключен к третьему входу блока умножения, а также тем, что блок вычисления моментов функции содержит два узла 3О умцожения,дна сумматора, узел ввода, узЕл деления и регистры, причем,выход первого регистра соединен с первым входом первого узла умножения, выход которого подключен к первому входу первого сумматора, выход которого соединен с Первым входом узла деления, первый и второй выходы узла ввода соединены соответственно с перным и вторым входами второго узла умножения,второй 4О и третий входы которого соединены с первым и вторым выходами узла деления, первый и второй выходы второго узла умножения соединены с перным и вторым входами второго сумматора, 45 третий вход которого соединен с третьим выходом узла деления, третий выход узла ввода подключен к вторым входам первого узла умножения и узла деления, третий вход которого соеди- 50 нен с четвертым выходом узла ввода, пятЫй выход узла нвода подключен к второму входу первого сумматора, третий, четвертый и пятый входы которого Соединены соответственно через второй, третий и четвертый регистры с одними информационными входами блока вычисления моментов фунКции, другие информационные входы которого подключены, соответственно, к входу первого регистра и к второму ЬО входу узла ввода, выход второго сумматбра является информационным выходом блока вычисления моментов функции.

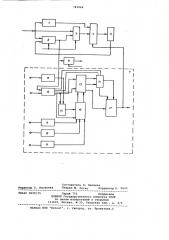

Иа чертеже йредставлена блок-схема устройства. 65

Устройство для решения дифференциальных уравнений в частных производных содержит регистры 1-3, блок 4 умножения, сумматор 5, коммутатор б, блок 7 вычисления моментов функции.

В состав блока 7 входят регистры

8-11, узел 12 ввода, узлы 13 и 14 умножения, узел 15 деления, сумматоры

16 и 17.

Алгоритм, реализуемый устройством, получается н результате замены вторых производных уравнений v а и а и

7 = Зт а моментами функции О, а первой производной по конечно-разностным отношениям, что приводит к уравнению

«««, . «»» «,« с кЛ кл которое вычисляется по явной итера ционной формуле вида

П+«,5 И,5 + @tl,5 QYl,s к1 кj кл где вычисление моментов функций и происходит при решении следующих систем алгебраических уравнений:

4, . +4.4 .+A, =Ь к3 -I КЛ кЛ-«

U 20 +О

КД-«x,j к,«+« ч . ч +« -2

М .ФМ . М =6 &к+««к к « к-«„j к,«к+«j

При этом решается уравнение

hA«.« =d hh,„ Р.

Bi

Д»

"+«С ° -d- А

1 «1 а, 1«- -г=к — т

«« где А ., С .,  — значение разностных

1 1 1 коэффициентов вида

А1И „+C .È„+Â .

=д

d, — матрица правой части.

Работа устройства происходит следующим образом.

В регистры 1-3 заносятся начальные услония U и U Эти зна1

1«} ) -1,1. чения умножаются н блоке 4 на моменты функций 4„> и &к1, поступающие на вход блока 4 с выхода блока 7. Полученные произведения складываются на сумматоре 5 и поступают н регистр

2 н качестве 1-ой итерации решения на 1-ом временном слое. Аналогично получается 2-ая и т.д. итерации искомого решения.При этом блок 7 вычисляет моменты функции М « " ..М"

<«,5-и к) ..- кj

® к,« а коммутатор б по управляющему сигналу соединяет выход устройства со входами соседних устройств, на которые поступает текущее значение решения, получаемых в данном устройстве. По окончании итерационI ного процесса по управляющему сигналу з регистра 2 в регистр 3 осуществля742946 ется запись полученного на первом временном слое решения 0 „,а в регистр 2 заносится начальйое условие

z.o

0„ -. Аналогично происходит работа устройства на 2-ом и т.д. на и -ом временном слое.

Работа блока 7 на 5-той итерации и временного слоя происходит следующим образом.

В регистры 6-11 записаны начальные условия а(.„, U;+<, U;, U;+< соответственно. На узел 12 с выхода регистра 2 поступает текущее значение реив шения U,а íà его другой вход поступают в узел 12 подготовленные начальные значения М;, А;, С,, В,,(Ъ;.

На узел 15 с выхода узла 12 йоступают значения А . и В; соответственно, а с выхода сумматора 16 — разность С . — <„ A „.,ãäe сС„ A „- сформиро1 вано узлом 13. Значения, поступающие на вход узла 15, получены в результате суммирования на сумматоре 16 значений U„ <,U„, U,. 1, хранящихся в регистрах 9-11. Полученные значения прогоночного коэффициента с(1,,(А1 и значение О = поступают с;-а,л; на узел 14, на который одновременно из узла 12 подаются значения Мqн (1

Полученные произведения с(.д,.„>hh,fb„. суммируются на сумматоре 17 со зиад; чением В = „ .1 поступающим с

1- 1 1 выхода узла 15. Полученная сумма является текущим значением момента функции М„ + =<, +q (где

p„,=а(„+B), непрерывно отражающим поведение функции И в области решения.

Реализацию предлагаемого устройства можно осуществлять на основе микросхем серий К 178, К 186,К 502.

Введение дополнительного блока вычисления моментов функции выгодно отличает предлагаемое устройство от известного, так как позволяет решать важный класс задач, описываемых параболическими и эллиптическими уравнениями с большей точночтью и быстродействием, увеличен- ными на три порядка в случае неравномерной сетки и на два порядка в случае равномерной сетки, по сравнению с известным.

Формула изобретения

1. Устройство для решения дифференциальных уравнений в частных производных, содержащее регистры, блок умножения, сумматор, коммутатор, причем выход первого регистра соединен с первым входом блока умножения, выход которого соединен со входом сумматора, выход сумматора подключен к одному из входов вто5

65 рого регистра, выход которого соединен с первыми входами коммутатора и третьего регистра, выход которого .соединен со вторым входом блока умножения, вход первого регистра и вторые входы второго и третьего регистров соединены с информационным входом устройства, третьи входы второго и третьего регистров и второй вход коммутатора подключены к управляющему входу устройства, выход коммутатора является информационным выходом устройства, о т л и ч а ющ -е е с я тем, что, с целью повышения точности, в него введен блок вычисления моментов функции, вход которого соединен с выходом второго регистра, а выход блока вычисления моментов функции подключен к третьему входу блока умножения.

2. Устройство по п.1, о т л ич а ю щ е е с я тем, что блок вычисления моментов функции содержит два узла умножения, два сумматора, узел ввода, узел деления и регистры, причем выход первого регистра соединен с первым входом первого узла умножения, выход которого подключен к первому входу первого сумматора, выход которого соединен с первым входом узла деления, первый и второй выходы узла ввода соединены соответственно с первым и вторым входами второго узла умножения, второй и третий входы которого соединены с первым и вторым выходами узла деления, первый и второй выходы второго узла умножения соединены с первым и вторым входами второго сумматора, третий вход которого соединен с третьим выходом узла деления, третий выход узла ввода подключен к второму входу первого узла умножения и узла деления, третий вход которого соединен с четвертым выходом узла ввода, пятый выход узла ввода подключен к второму входу первого сумматора, третий, четвертый и пятый входы которого соединены соответственно с одними информационными входами блока вычисления моментов функции, другие информационные входы которого подключены соответственно к входу первого регистра и к второму входу узла ввода, выход второго сумматора является информационным выходом блока вычисления моментов функции.

Источники информации, принятые во внимание при экспертизе

1. Пухов Г.Е. Цифровые сетки параллельно-последовательного действия для интегрирования дифференциальных уравнений. "Электроника и моделирование", вып. 3, Киев, 1974.

2. Авторское свидетельство СССР

9 373735, кл. G 06 G 7/56, 1971 (прототип), 742946

Составитель Н. Палеева

Техред М. Петко Корректор Е. Папп

Редактор Т. Киселева

Закаэ 3619/15

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. ужгород, ул. Проектная,4