Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«»742951 (61) Дополнительное к авт. свид-ву (22) Заявлено 01.0378 (21) 2604954/18-24 (5 f 3 М. (л.2 с присоединением заявки N2

G 06 F 15/34

Государственный комитет

СССР по делам изобретений. и открытий (23) Приоритет

Онубликовано250680. Бюллетень М 23

Дата опубликования описания 250630 (533 УДК 681. 3 (088. 8) (72) Авторы изобретен и я

Е.Ф. Киселев и Е.О. Березовский (71) Заявитель (54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной технике и предназначено для воспроизведения функции одного аргумента, представленного или числоимпульсным (унитарным), или параллельным кодом.

Известно устройство, содержащее дешифратор, сумматор, блок памяти (БН), умножитель (1) .

Однако при увеличении точности воспроизведения функций увеличивается емкость БП, что вызывает определенные трудности при построении на основе этого преобразователя устройства для воспроизведения многоразрядной функ- 15 ции.-Наиболее близким по технической сущности к изобретению является устройство, содержащее генератор 20 импульсов, двоичный умножитель, первые входы которого соединены с выходами блока задания коэффициентов и счетчик функции (2) .

Однако устройство имеет низкие функциональные возможности из-за того, что переключение участков аппроксимации организовано по числоимпульсному коду модуля функции

/у(х) / и параллельный код аргумента хЗО в преобразователе не вырабатывается, что создает определенные трудности при его настройке и контроле или требует усложнения его схемЫ.

Цель изобретения — расширение . функциональных воэможностей, для обеспечения работы как с числоимпульсным, так и параллельным кодами аргумента без увеличения объема оборудования.

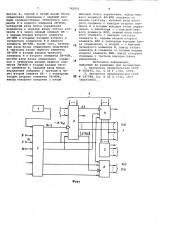

Поставленная цель достигается тем, что в устройство, содержащее генератор импульсов, блок задания коэффициентов,счетчик функции и двоичный умножитель, первая группа входов которого соединена с выходами блока задания коэффициентов, дополйительно введены счетчик участков аппроксимации и блок управления, первый вход которого соединен с выходом генератора импульсов, второй — является входом запуска преобразователя, третий — входом числоимпульсного кода аргумента преобразователя, четвертый — входом признака режима работы преобразователя, пятый вход соединен с первыми выходом двоичного умножителя, шестой — с выходом счетчика участков аппроксимации, седьмой— с выходом блока задания коэффициен742951 тов, а первый выход блока упра вления — с тактовым входом двоичного умножителя, второй — с первыми управляющими входом двоичного умножителя, счетчика участков аппроксимации и счетчика функции, третий — с вторыми управляющими входами соответственно двоичного умножителя и счетчика участков аппроксимации, четвертый и пятый — соответственно со вторым и третьим входами счетчика функции, четвертый вход которого соединен со вторым выходом двоичного умножит@ля, а выходы счетчика функции являютая выходами кода функции преобразователя, вторая группа входов дйоичного умножителя является входами кода младших разрядов аргументй,выходами старших разрядов которого являются входы счетчика участков аппроксимации, входы блока задания коэффициентов соединены с выходами счетчика участкон аппроксимации и являются выходами старших разрядов аргумента, выходами младших разрядов которого являются выходы двоичного умножителя, третий ныхОд которого соединен с третьим входом счетчика участков аппроксимации.Кроме того, блок управления содержит элементы И, ИЛИ, НЕ, 2И-ИЛИ и триггер, причем первый вход блока управления соединен G первым входом пЕрвого элемента И, второй вход кОторого соединен с выходом триггера, а выход — с первым выходом блока управления, второй вход блока управлЕния соединен с первыми входами второго и третьего элементов И,третий и пятый входы блока управления соединены с первыми входами соответственно четвертого элемента И и первого элемента 2И-ИЛИ, четвертый нХод блока ут равления подключен к первому входу пятого элемента И и через первый элемент НŠ— с первым входом второго элемента 2И-ИЛИ и вток рыми входами второго и четвертого элементов И и первого элемента

2И-ИЛИ, кроме того, четвертый вход блока управления подключен к третьему входу первого элемента 2И-ИЛИ и вторым входам третьего элемента И и второго элемента 2И-ИЛИ, шестой вход блока управления соединен с четвертым входом первого элемента

2И- (ЛИ и вторым нходом пятого элемента И, седьмой вход блока управления соединен с третьим и через вторОЭ элемент НŠ— с четвертым входом второго элемента 2И-ИЛИ, выход которого соединен с пятым выходом блока управления, выход первого элемента 2И-ИЛИ соединен со входом триггЕра, нулевой вход которого соединен с выходом второго элемента И и вторым ныходом блока управления, а еДИничный †с выходом первого эле,мента ИЛИ, первый вход которого сое динен с выходом третьего элемента И, первым входом второго элемента ИЛИ и четвертым выходом блока управления, а второй — с выходом четвертого элемента И, выход пятого элемента И соединен со вторым входом второго элемента ИЛИ, выход которого соединен с третьим выходом блока управления.

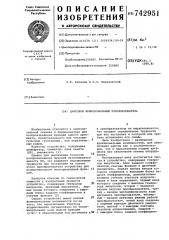

На фиг. 1 представлена структурная схема предложенного преобразонателя; на фиг.2 — схема блока управления, Схема содержит генератор 1 импульсов, блок 2 управления, к — разрядный двоичный умножитель 3, счетчик

l5 4 участков аппроксимации, блок 5 задания коэффициентов, счетчик 6 функции, входы 7 „ — разрядного параллельного кода аргумента, вход 8 запуска, нход 9 — числоимпульснсго

2Q кода. аргумента и вход признака режима 10,элементы 11-15 И, триггер 16, элементы 17 и 18 2И-ИЛИ, элементы

19-20 ИЛИ, элементы 21,22 НЕ, входы

23-25, выходы 26 — 28. д Преобразователь работает в режиме вычисления функции по числоимпульсному коду аргумента и н режиме вычисления функции по параллельному коду аргумента.

В первом режиме на вход 8 поступает импульс зпуска Хо,, на вход 9 импульс последовательного кода аргумента, а на вход 10 — логический сигнал О о= По импульсу Х д блок 2 управления производит установку начальных условий вычисления, т.е, на втором выходе генерирует импульс, по которому двоичный умножитель 3 и счетчик 4 устанавливаются в О, а счетчик

40 функции б — в состояние, соответствующее у (О} .

По каждому импульсу последовательного кода аргумента Х н устройстве осуществляется такт вычислений.

Это происходит следующим образом, Но каждому импульсу блок 2 управления разрешает прохождение импульсов генератора 1 на вход сомножителя двоичного умножителя 3, на входы параллельного сомножителя которого с ныл ходов блока О5 поступает код /K. /.

По двум сомножителям (коду /К / и импульсам генератора 1) дноичнйй умножитель 3 на выходе вырабатывает последовательность импульсов, поступающих на счетный вход счетчика б функции, и изменяют его содержимое в зависимости от значения знакового разряда К> (т.е. при К 70 содержимое счетчика б функции увеличивается, ф) а при К <О уменьшается) . Это продолжается до тех пор, пока на первом выходе двоичного умножителя 3 не вырабатывается импульс переполнения, поступающий на первый вход обратной у5 грязи блока 2 управления.

742951

После окончания этого импульса схема 2 управления запрещает прохождение импульсов генератора 1 на вход числоимпульсного сомножителя двоичного умножителя 3. На этом такт вычисления заканчивается, а следующий такт рачнется только с приходом на преобразователь очередноГ о импульса кода аргумента.

Во втором режиме на вход 8 посту- пают импульсы -запуска, а на вход

10 — логический с*гнал П = 1.

<о

По импульсу запуска блок 2 управления производит установку условий вычисления, а именно — на третьем выходе генерирует импульс, по кото-. рому с входов 7 производится запись в двоичный умножитель 3 и счетчик 4 соответственно К), младших и (п), — К() старших разрядов n > — разрядного кода аргумента х; на четвертом выходе генерирует импульс, по которому счетчик б функции устанавливается в состояние, соответствующее у(ф,„о„)

После этого схема 2 управления разрешает прохождение импульсов генератора 1 на вход сомножителя двоичного умножителя 3, на входы параллель

-ного сомножителя которого с выходов блока 5 поступает код /Kj/.

10, за счет обеспечения работы как с

По двум сомножителям (коду /К./ и импульсам генератора 1) двоичный умножитель 3 вырабатывает последова- тельность импульсов, поступающих на счетный вход счетчика 6 функции И изменяют его содержимое в зависимости от значения, знакового разряда K> . (т.е. при К ) 0 содержимое счетчика функции б уменьшается, а при К (О увеличивается).

Процесс вычисления продолжается до тех пор, пока на выходе счетчика

4 не вырабатывается импульс его переполнения, который поступает на второй вход обратной связи блока 2 управления.

2. Преобразователь по н.l, о тл и ч а ю шийся тем, что блок угравления содеркит элементы И, ИЛИ, HE 2И-ИЛИ и триггер, причем первый вход блока управления соединен с

60 первым входом первого элемента И, второй вход которого соединен с выходом триггера, а выход — с первым выходом блока управления, второй вход блока управления соединен с первыми входами второго и третьего эле65

После окончания этого импульса блок 2 управления запрещает прохождение импульсов генератора 1 на вход сомножителя двоичного умножителя 3 и генерирует на третьем выходе импульс, по которому в двоичный. умножитель 3 и счетчик 4 повторно заносится с входов 7 код параллельного аргумента х . Следовательно, после этого в двоичном. умножителе 3 и счетчике 4 содержится код аргумента х, а код у(х) содержится в счетчике б функции.

Технико-экономическая эффективность изобретения заключается в более высоких функциональных воэможностях, а именно преобразователь может воспроизводить функцию аргумента, представленного или последовательным или параллельным кодом.

Формула изобретения

1. Цифровой функциональный преобразователь, содержащий генератор импульсов, блок задания коэффициентов, счетчик функции и двоичный умножитель, первая группа входов которого соединена с выходами блока задания коэффициентов, о т л.и ч а юшийся тем, что, с целью расширения функциональных возможностей числоимпульсным, так и параллельным кодами аргумента, в него введены счетчик участков аппроксимации и

;блок управления, первый вход которого соединен .с выходом генератора импульсов, второй — является входом запуска преобразователя, третий— входом числоимпульсного кода аргумента преобразователя, четвертый— входом признака режима работы .преобразователя, пятый вход соединен с первым выходом двоичного умножителя, шестой — с выходом счетчика участков аппроксимации, седьмой— с выходом блока задания коэффициентов, а первый выход блока управления — с тактовым входом двоичного умножителя, второй — с первыми управляющими входами двоичного умножителя, счетчика участков аппроксимации и счетчика функции, третий — с вторыми управляющими входами двоиччого умножителя и счетчика участков аппроксимации, четвертый и пятый — соответственно со вторым и третьим входами счетчика функции, четвертый вход которого соединен со вторым выходом двоичного умножителя, а выходы счетчика функции являются выходами кода функции преобразователя, вторая группа входов двоичного умножителя являются входами параллельного кода. младших разрядов аргумента, выходами старших разрядов которого являются входы счетчика участков аппроксимации,входы блока задания коэффициентов соединены с выходами счетчика участков аппроксимации и являются выходами старших разрядов аргумента, выходами младших разрядов которого являются выходы двоичного умножителя, третий выход которого соединен с третьим входом счетчика участков аппроксимации.

742951

Иод

ЙОд

9(xj ментов И, третий и пятый входы блока управления соединены с первыми входами соответственно четвертого зле;мента И и первого элемента 2И-ИЛИ, четвертый вход блока управления подключен к первому входу пятого элемента И и через первый элемент НЕ— с первым входом второго элемента

2И-ИЛИ и вторыми входами второго и четвертого элементов И и первого элемента 2И-ИЛИ, кроме того, четв ертый вход блока управления подключен и третьему входу первого элемента

2И-ИЛИ и вторым входом третьего элеМента И и второго элемента 2И-ИЛИ, шестой вход блока управления соединен с четвертым входом первого элемента 2И ИЛИ и вторым входом пятого элемента И, седьмой вход блока управления соединен с третьим и через Второй элемент НŠ— с четвертым входом второго элемента 2И-ИЛИ, 20 выход которого соединен с пятым выходом блока управления, выход первого элемента 2И-ИЛИ соединен со входом триггера, нулевой вход которого соединен с выходом второго элемента И и вторЫм выходом блока управления, а единичный — с выходом первого элемента ИЛИ, первый вход которого соединен с выходом третьего элемента И, первым входом второго элемента ИЛИ и четвертым выходом бло<а управления, а второй — с выходом четвертого элемента И, выход пятого элемента И соединен со вторым входом второго элемента ИЛИ, выход которого соединен с третьим выходом блока управления, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 504195, кл. G 06 F 1/02, 1976 °

2, Авторское свидетельство СССР

В 547788, кл. G 06 G 7/26, 1977 (прототип).

742951

Ю Их (О

Фие 2

Составитель A. Зорина

Редактор Т. Киселева Техред И.Асталош Корректор В. Синицкая

Заказ 3619/15 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раумская наб., д. 4/5

Г

Филиал ППП Патент, г. Ужгород, ул. Проектная,4