Устройство дл прогнозирования неисправностей радиоэлектронной аппаратуры

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социвлистичесник

Республик

G 06 F 15/46 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений н открытий (23) Приоритет

Опубликовано 25.06.80. бюллетень № 23

Дата опубликования описания 25.06.80 (53) УДК 681.326 088. 8) В.М.Ганичев, С.Л.Федченко, В.С.Калашников, А.A.Çâoíoâ, П.П.Бабенко и В.С.Глоба (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ НЕИСПРАВНОСТЕЙ

РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ

Изобретение относится к контрольноизмерительной технике и может быть использовано для поиска и прогнозирования неисправностей радиоэлектронной аппаратуры (РЭА) .

Известны устройства для прогнозирования неисправностей, содержащие датчики параметров объекта, аналого-цифровые преобразователи, коммутаторы, компараторы, анализаторы и блоки прогнозирования неисправностей (1) и (2)

Недостатком известных устройств является ограниченная полнота контpOJI SI

Наиболее близким по технической сущности к предлагаемому является устройство для прогнозирования неисправностей, содержащее последова- 20 тельно соединенные датчики контролируемых параметров, первый коммутатор, первый аналого-цифровой преобразователь, первый вычислитель, а так же регистратор.

Недостатком известного устройства является низкая достоверность, контроля зависящая от неучета информации о возникающих сбоях контролируемой аппаратуры. 30

Цель изобретения — повышение достоверности контроля. Указанная цель достигается тем, что устройство содержит последовательно соединенные датчики контролируемых параметров, первый коммутатор, первый аналогоцифровой преобразователь, первый . вычислитель, а также регистратор, датчики внешних воздействий, датчики сбоев, блок обработки информации и анализатор, первый, второй и третий входы которого соединены соответственно с выходами первого вычислителя, выходами датчиков внешних воздействий и выходами датчиков сбоев, а выход — с первыми входами регистратора и блока обработки информации, вторые входы которого соединены с выходами датчиков сбоев, выход — со вторым входом регистратора и тем, что анализатор содержит первый регистр, первый дешифратор, второй коммутатор, второй аналого-цифровой преобразователь и второй вычислитель первый вход которого через последовательно соединенные. первый дешифратор и первый регистр подключен к третьему входу анализатора, второй вход через последовательно соединен.ные второй аналого-цифровой преоб742958 разователь и второй коммутатор — ко второму входу анализатора, третий вход — к первому входу анализатора, а выход — к выходу анализатора, а таК же тем, что блок обработки ин- формации содержит первый и второй регистры, первый и второй узлы памяти,. генератор импульсов, счетчик, элемент задержки, второй и третий дешифраторы,. элемент сравнения, индикатор и формирователь кода, первый вход которого через второй регистр подключен ко второму входу блока обработки информации, второй вход через последовательно соединенные первый регистр и второй дешифратор— к Выходу первого узла памяти, тре- 15 тий вход - через последовательно совдиненные элементы задержки и гейератор импульсов -- к первом., входу блока обработки информации, а вь-.ход через последовательно соединенные элемент сравнения M индикатор — к выходу блока обработки информации, вход счетчика соединен с выходом генератора импульсов, выход — со вторым входом второго дешифратора и первым входом третьего дещифратора, второй вход которого подключен к выходу второго узла памяти, а выход — ко второму входу узла сравнения.

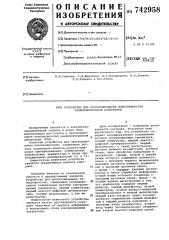

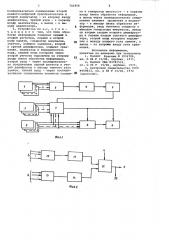

На фиг.1 и îáðàæåíà блок-схема устройства для прогнозирования неисправностей радиоэлектронной аппаратуры; на фи-..2 — функциональная схема анализатора„ на фиг,3 — блок обработки информации, 35 устройство содержит датчики 1 контролируемых параметров, первый коммутатор 2, первый. аналого-цифровой преобразователь .3, первый вычислитель

4, датчики 5 внешних воздействий, 40 . датчики 6 сбоев, анализатор 7, блок

8 обработки информации„регистратор

9, первый регистр 10, первый дешифратор 11, второй вычислитель 12, второй коммутатор 13, второй аналогоцифровой преобразователь 14, первый узел 15 памяти, второй дешифратор 16, первый регистр 17, формирователь 18 кода, элемент 19 сравнения, индикатср 20, второй регистр 21,. элемент

22 задержки, генератор 23 импульсов, счетчик 24, третий,цешифратор 25, второй узел 26 памяти.

Предлагаемое устройство работает следующим образом.

1 э Датчики 1..щ измеряют абсолютные значения параметров контролируемой аппаратуры. Измеренные значения напряжений параметров поступаю- на коммутатор 2. Коммуратор 2 осуществляет периодическую трансляцию выходных 60 сигналов от датчиков 1 через преобразователь 3 на блок 4.

После второго измерения и приема абсолютных значений каждого параметра коммутатор блока 4 определяет раз- 65 ность амплитуд напряжений, соответствующих двум соседним моментам времени. Одновременно измеряется разность между результатом последнего измерения и значениэм предельно допустимого изменения этого же параметра, хранящимся в памяти Блока 4, Вычисленные результаты подвергаются логической обработке в блоке 4. Определяется время оставшееся до выхода параметра эа допуск в соответствии с выражением

А -А

1 î

А„ -А..„() .. -t, 1 (-1 где А, А. - амплитуды измеряемых

1 значений параметра в моменты времени (i u (i †) — соответственно;

А — предельно допустимая амплитуда параметра.

Определение аналоговых значений осуществляется по каждому из п параметров. Вычисленные значения поступают в блок 12 анализатора 7.

Условия, в которых работае-. контролируемая датчиками 5 РЭА, Датчики 5 независимо от датчиков 1 вырабатывают при превышении допускаемых значений параметров внешних условий (температура, напряжение первичных источников питания и т.д„) постоянный уровень напряжения, Периодически коммутатор 13 считывает сигналы с датчиков 5 и синхронно, через преобразователь 14 осуществляет запись показателей датчиков 5 в память блока 12 анализатора 7, Одновременно с измерением контролируемых параметров датчикаьж 1 датчиками 6 производится контроль состояния исправности по наличию сигналов сбоев. При этом сигналы сбоев поступают в регистр 10 анализатора

7. Сформированное на регистре 10 число поступает в параллельном коде на входе шины дешифратора 11 .анализатора 7 и память блока 12.

На выходных шинах дешифратора 11 формируется управляющий сигнал, осуществляющий формирование адреса ячеек памяти блока 12 анализатора 7, в которых содержатся значения параметров времени Т, предшествовавшее сбою контролируемой РЭА, и характеристики сопуствовавших ему сбоев внешних устройств, а также значения расчетного времени выхода эа допуски внутренних параметров, Программа блока 12 в соответствии с управляющим сигналом выбирает иэ памяти значения записанных в эти ячейки параметров и передают их в арифметико-логическое устройство блока 12.

В арифметико-логическ м устройстве блока 12 решается задача определения факторов, причастных к возник742958 новению сбоев по их пространственновременным характеристикам путем проверки одновременности появления сбоев в контролируемой аппаратуре и внешних устройствах, совпадения моментов их появления с изменениями

5 внешних условий, а также возможности выхода внутренних параметров эа допуск по величине t (1) . При этом решение о предстоящем выходе РЭА иэ строя принимается в соответствии с логическим выражением: (а,Ь,c) -а лЬ лсчалЪлсча лолам а лолс (2) где а=1,а-0 — совпадение и несовпадение по времени сбоев контролируемой РЭА со 15 сбоями внешних устройств за время Т соответственно;

Ь-1,Ь=Π— нахождение внутренних параметров в границах, соответствующих допустимой и недопустимой величине расчетного времени выхода их за допуск соответственно;

c=1,c=0 — состояния, характеризуемые внешними условиями, сопутствующими возникновению сбоя, в пределах нормы и не в норме соответственно.

При формировании суждения сигнал сбоя вызван не старением элементов, а случайным изменением внешних условий или сбоем во внешних устройствах, на регистратор 9 выдается сигнал исправности„

При формировании суждения о неисправности арифметико-логическое 40 устройство блока 12 выдает сигнал неисправности на регистратор 9 и одновременно включает в работу— генератор 23 узла 8.

Узел 8 работает следующим образом. 45

Перед началом работы в узел 15 заносятся признаки, характеризующие отклонение в работе проверяемых устройств. Таких признаков может быть

32,. а проверяемых устройств — 16.

В узел 26 для каждого устройства заносится число, характеризующее вероятность отказа соответствующего устройства. B случае поступления сигнала с решающего блока 12 анализатора 7 включается генератор 23, который последовательно выдает 16 импульсов на счетчик 24. Сигналы с регистра 21 поступают на формирователь 18, на который поступает по сигналам счетчика 24 поочередно содержимое каждого из шестнадцати 32. разрядных регистров узла блока 16 через дешифратор 16 и регистр 17, Формирователь 18 последовательно срав нивает содержимое регистра 21 с содержимым регистров узла 15 и выдает код числового значения результата сравнения, который поступает на элемент 19. Управление работой элемента

18 осуществляется сигналами генератора 23, которые поступают через элемент 22. Элемент 19 сравнивает число полученное с формирователя 18, и число иэ узла 26, полученное через дешифратор 25 с помощью счетчика 24.

В случае, если число на выходе формирователя 18 будет больше или равно числу в узле 26, на индикатор 20 поступает сигнал о неисправности соответствующего устройства. В слу чае, если число, полученное формирова. телем 18, будет меньше числа хранящегося в узле 26, сигнала на индикатор 20 не поступит.

Реализация отличительных призна-ков изобретения позволила уменьшить ошибки 2-го ряда примерно в 2 раза, а ошибки 1-ro ряда = в 1,2 раза, т.е. повысить достоверность правильного определения факта приближающегося от. каза РЭА и эа счет этого увелиЧить среднее время между ее отказами в

1,5 раза, а среднее время между сбоями — в раза, повысить вероятность правильного определения места неисправности с 0,6 — 0,8 и снизить время, затрачиваемое на восстановление, на 15-20%.

Формула изобретения

1. Устройство для прогнозирования неисправностей радиоэлектронной аппаратуры, содержащее последовательно соединенные датчики контролируемых параметров, первый к оммутатор, первый аналого-цифровой преобраз ов атель, первый вычислитель, а также регистратор, о т л и ч а ющ е е с я тем, что, с целью повМшения достоверности контроля, устройство содержит датчики внешних воздействий, датчики сбоев, блок обработки информации и анализатор, первый, второй и третий входы которого соединены соответственно с выходами первого вычислителя, выходами датчиков внешних воздействий и выходами датчиков сбоев, а выход — с первыми входами регистра и блока обработки информации, вторые входы которого соединены с выходами датчиков сбоев, выход — со вторым входом регистра.

2, Устройство по п,1, о т л и ч а ю щ е е с я тем, что анализатор содержит первый регистр, первый дешифратор, второй коммутатор, второй аналого-цифровой преобразователь и второй вычислитель, первый вход которого через последовательно соединенные первый дешифратор и первый регистр подключен к третьему входу анализатора, второй вход через

742958 последовательно соединенные второй аналого-цифровой преобразователь и второй коммутатор — ко второму входу анализатора, третий вход — к первому входу анализатора, а выход — к выходу анализатора. 5

3. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок обработки информации содержит первый и второй регистры, первый и второй узлы памяти, " åíåðàòîð импульсов,,щ счетчик, элемент задержки, второй и третий дешифраторы, элемент сравненйя, индикатор и формирователь кода, первый вход которого через второй регистр подключен ко второму входу блока обработки информации, второй вход — через последовательно соединенные первый регистр и второй дешиФратор к выходу первого узла памяти, третий вход — через последовательно соединенные элементы задерж- 20 ки и генератор импульсов — к первому входу блока обработки информации, а выход через последовательно соединенные элемент сравнения и индикатор — к выходу блока обработки информации, вход счетчика соединен с выходом генератора импульсов, выход со вторым входом второго дешифратора и первым входом третьего дешифратора, второй вхсщ которого подключен к выходу второго узла памяти, а выход - ко второму входу узла сравнения.

Источники информации, принятые во внимание при экспертизе

1. Патент франции М 2256706, кл. G 06 F 15/00, опублик. 1975.

2 ° Патент США 93781533, кл. 6 06 Р 15/46, опублик. 1973, 3. Авторское свидетельство СССР

9458833, кл. G 06 F 15/36, 1972 (прототип) °

742958

Составитель Н.Белинкова

Тех ед Н. Бабурка Ко екто Г.Наэа ова

Ре акто T.Êèñåëåâà

Филиал ППП Патент, г. ужгород. ул . Проектная, 4

Эаказ 3620/16 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35 Раушская наб., д. 4/5