Устройство для настройки аналоговых умножителей напряжений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских .

Социалистических

Республик (б1) Дополнительное к авт. свид-ву (51)М. Кл, (22) Заявлено 230178 { 21) 2572470/18-24 с присоединением заявки М— (23) ПриоритетG 06 G 7/16

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 250680. Бюллетень Мо 23

Дата опубликования описания 25,06.80 (53) УДК 681.335 (088. 8) (72) Авторы изобретения

В.H.Òèìoíòååâ, В.А.Ткаченко и В,С.Рысин (71) Заявитель (54) УСТРОИСТВО НАСТРОИКИ АНАЛОГОВЫХ

УМНОЖИТЕЛЕИ НАПРЯЖЕНИИ

Изобретение относится к устройствам контроля и настройки электрических параметров функциональных блоков и может быть использовано в вычислительных устройствах в качестве . устройства настройки аналоговых умножителей напряжений.

Известно устройство, предназначенное для контроля электрических параметров, содержащее ключевые и коммутирующие блоки, блоки индикации (1) .

Это устройство характеризуется сравнительно низкой точностью работы.

Наиболее близким к предложенному является устройство настройки аналоговых умножителей напряжений, содержащее источник тестовых напряжений, первый выход которого соединен с первыми неподвижными контактами первого и второго переключателей, вторые неподвижные контакты которых подключены к шине нулевого потенциала, вход устройства присоединен к входам первого, второго, третьего и четвертого ключевых элементов, вы ход первого ключевого элемента соединен с одним входом дифференциального интегратора, второй вход которого подключен к выходу пятого ключевого элемента, вход которого присоецинен ко второму выходу источника тестовых напряжений, управляющие входы первого и пятого ключевых элементов объединены,выход второго ключевого элемента через последовательно соединенные первый интегратор и шестой ключевой элемент подключен к первому выходу устройства, подвижный контакт первого переключателя соединен со входом седьмого ключевого элемента, подвижный контакт второго переключателя подключен ко второму выходу устройства, третий и четвертый выходы устройства присоединены соответственно к подвижным контактам третьего и четвертого переключателей, первые неподвижные контакты которым подключены к шине нулевого потенциала, вторые неподвижные контакты третьего и четвертого переключателей соединены соответственно с выходами второго и третьего интеграторов, пер- вые неподвижные контакты пятого, шестого и седьмого переключателей подключены к шине нулевого потенциала, вторые неподвижные контакты пятого и шестого переключателей присое742963 динены к третьему выходу источника тесТовых напряжений, управляющие входы третьего и седьмого ключевых элеМентов объединены, подвижный контакт пятого переключателя соединен

q пятым выходом устройства, шестой выход которого подключен к подвйжному контакту седьмого переключателя, второй неподвижный контакт которого присоединен к выходу дифференциального интегратора, подвижный контакт шестого переключателя соединен со входом восьмого ключевого элемента, управляющий вход которого объединен с управляющим входом четвертого ключевого элемента (2), Недостаток.известного устройства состоит в том, что с его помощью невозможно произвести балансировку аналогового умножителя напряжения на переменном токе, так как при работе с напряжением переменного тока выходные напряжения первого, второго и третьего интеграторов равны нулю.

ИзвЕстно, что при работе аналогового умножителя напряжений с сигналами напряжения переменного тока можно получйть более высокую точность перемножения, если балансировку умножителя Производить на переменном токе.

Цель изобретения — повышение точности настройки на переменном токе.

Поставленная цель достигается тем что н устройство введены первый и второй фазоные детекторы, выходы котОрых соединены соответственно со входами второго и третьего интеграторОв, входы первого Фазового детектора присоединены к выходам третьего и сЕдьмого ключевых элементов, входы второго фазового детектора подключе-. ны к выходам четвертого и восьмого ключевых элементов.

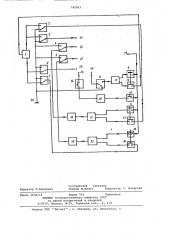

На чертеже изображена функциональная схема устройства настройки аналоговых умножителей напряжений.

Устройство содержит источник 1 тестовых н апряжений, первый, второй, третий, четвертый, пятый, шестой и седьмой переключатели 2 — 8, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой ключевые элементы 9 — 16, дифференциальный интегратор 17, первый, второй и третий интеграторы 18 — 20, первый и второй Фазовые детекторы

21 и 22, вход 23 устройства, первый, второй, третий, четвертый, пятый и шестой выходы 24 — 29 устройства, шийа 30 нулевого потенциала.

Устройство работает следующим образом.

К входу 23 устройства подключен выход аналогового умножителя напряжений; к первому 24, третьему 26, четверторму 27 и шестому 29 ныходам устройства подключены соответствующие балансировочные входы и входы, установки коэффициента перемножения аналогового умножителя напряжений; ко второму 25 и пятому 28 выходам устройства подключены соответствующие информационные входы аналогового умн ожителя напряжений .

В исходном состоянии нторой, третий, четвертый, пятый и шестой выходы 25 — 29 устройства через соответствующие переключатели подключены к шине 30 нулевого потенциала, а все ключевые элементы устройства — разомкнуты. В этом состоянии напряжение на входе 23 устройства должно быть равно нулю, так как равны нулю напряжения на информационных входах аналогового умножителя напряжений.

Наличие напряжения на входе 23 устройства свидетельствует о разбалансировке выходного каскада аналогового умножителя напряжений. При заьы20 канин второго 10 и шестого 14 ключевых элементов первый интегратор 18 начинает интегрировать это напряжение до тех пор, пока оно не станет равным. нулю. По достижении этого мо 5 мента размыкается второй 10 ключевой элемент, при этом на выходе первого интегратора 18 сохраняется напряжение смещения, величина которого компенсирует разбаланс выходного

ЗО каскада аналогового умножителя напряжений. При переключении первого 2 и второго 3. ключевых элементов на второй выход 25 устройства и на один из входов первого фазового детектора

35:21 подаются сигналы от источника 1 тестовых напряжений. При этом напряжение на входе 23 устройства должно оставаться равным нулю, так как на .пятом выходе 28 устройства напряжение равно нулю.

Наличие на входе 23 устройства напряжения переменного тока (на выходе аналогового умножителя напряжений} снидетельстнует о разбалансе умножителя по информационному входу, сня45 нанном с пятым выходом 28 устройства.

Замыкают четвертый 12 и восьмой 16 ключевые элементы. В результате н работу включаются второй Фазовый детектор 22 и третий интегратор 20.

50 Происходит компенсация напряжения переменного тока, после чего четвертый 12 и восьмой 16 ключевые элементы размыкаются. Напряжение же, которое заполнил третий интегратор 20 постоянно пРиложено к четвертому выходу 27 устройства. Аналогичным образом происходит компенсация разбаланса по другому информационному входу аналогового умножителя напряжений.

Затем происходит установка требуе60 мого коэффициента перемножения умножителя. Для этого на второй 25 и пятый 28 выходы устройства (на соот— ветствующие информационные входы аналогового умножителя) через соот65 ветстнующие переключатели подаются

742963 сигналы с выходов источника 1 тестовых напряжений. В работу включается дифференциальный интегратор 17, на входы которого поступают напряжения со входа ?3 устройства (с выхода аналогового умножителя) и опорное . 5 напряжение от источника тестовых напряжений 1. Дифференциальный интегратор 17 интегрирует разность этих напряжений до тех пор, пока она не станет равной нулю. Это соответствует о установке заданного коэффициента перемножения. На этом заканчивается процесс настройки аналогового умножителя напряжений с помощью предложенного устройства, причем течность настройки выше, так как происходит она на переменном токе.

Формула изобретения

Устройство для настройки аналоговых умножителей напряжений, содержащее источник тестовых напряжений, первый выход которого соединен с первыми неподвижными контактами первого и второго переключателей, вторые непод- 25 вижные койтакты которых подключены к шине нулевого потенциала, вход устройства присоединен к входам первого, второго, третьего. и четвертого ключевых элементов, выход первого ключе- 30 ного элемента соединен с одним входом дифференциального интегратора, второй вход которого подключен к выходу пятого ключевого элемента, вход

Которого присоединен ко вто- 3$ рому выходу источника тестовых напряжений, управляющие входы первого и пятого ключевых элементов объединены, выход второго ключевого элемента через последовательно соединенные пер- 4О вый интегратор и шестой ключевой элемент подключен к первому выходу ус1ройства, подвижный контакт первого переключателя соединен со входом .седьмого ключевого элемента, подвижный контакт второго переключателя подключен ко второму выходу устройства, третий и четвертый ныходы устройства присоединены соответственно к подвижным контактам третьего и четвертого переключателей, первые неподвижные контакты которых подключены к шине нуленого потенциала, вторые неподвижные контакты третьего и четвертого переключателей соединены соответственно с выходами второго и третьего интеграторов, первые неподвижные контакты пятого, шестого и седьмого переключателей подключены к шине нулевого потенциала, вторые неподнижные контакты пятого и шестого переключателей присоединены к третьему выходу источника тестовых напряжений, управляющие входы третьего и седьмого ключевых элементов объединены, подвижный контакт, пятого переключателя соединен с пятым выходом устройства, шестой выход которого подключен к подвижному контакту седьмого переключателя, второй неподвижный контакт которого присоединен к выходу дифференциального интегратора, подвижный контакт шестого переклЮчателя соединен со входом восьмого ключевого элемента, управляющий вход которого объединен с управляющим входом четнертого ключевого элемента, о т л и ч а ю щ е е с я тем, что, с целью повышения точности настройки на переменном токе, в него введены пЙрвый и второй фазовые детекторы, выходы которых соединены соответст;— венно со входами второго и третьего интеграторов, входы первого фазового детектора присоединены к выходам третьего и седьмого ключевых элементов, входы второго фазового детектора подключены к выходам четвертого и восьмого ключевых элементон.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9399802, кл. G 01 R 31/28, 1971.

2. Авторское свидетельство СССР

9618748, кл. G 06 С 7/16, 1975 (прототип) .

7429б3

Составитель Сапунова

Техред И.Пежо Корректор Г. Назарова

Редактор Т.Киселева

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Заказ 3620/lб Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5