Запоминающее устройство для коммутационной системы связи

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик п»743023

К АВТОРСКО (61) Дополнительно (22) Заявлено 05.07 с присоединением за (23) Приоритет—

Опубликовано

Дата опублико (51) M. Кл.2

С 5/02

С 11 С Гпоо

Гасударственный камитвт

СССР (53) УДК 681.327..6 (088.8) но делам изобретений и открытий (72) Авторы изобретения

В. М. Гинзбург и О. Н. Карышева (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЛСТВО

ДЛЯ КОММУТАЦИОННОЛ СИСТЕМЫ СВЯЗИ

Изобретение относится к вычислительной технике, в частности к запоминаюшим устройствам и предназначено для использования в устройствах памяти программ коммутационных систем связи, а также в различных системах управления, например, в системах управления производственными процесса ми.

Известно запоминающее устройство для коммутационной системы связи {1J, содержащее долговременное запоминающее устройство, в котором хранятся программы обслуживания. Долговременные запоминающие устройства (ДЗУ) обеспечивают длительное устойчивое хранение информации и позволяют сравнительно недорого построить устройства памяти большой емкости.

Общим недостатком всех известных ДЗУ является неоперативность смены информации, так как для этого требуется механическая перестройка — замена металлических карт, твисторов, перешивка обмоток ферритовых сердечников. Этот недостаток проявляется при необходимости оперативной коррекции программы и особенно ощутим в коммутационных системах переменной структ .ры, в частности, в системах связи с подЭ вижными объектами.

Наиболее близким по технической сущности к данному изобретению является устройство (21, содержащее два накопителя постоянной памяти и один накопитель оперативной памяти, регистр выборки числа и регистр выборки накопителя постоянной памяти, при этом первый выход регистра .выборки накопителя постоянной памяти соединен с первым входом первого накопителя

10 постоянной памяти, а второй выход — с первым входом второго накопителя постоянной памяти, первый выход регистра выборки числа соединен с третьим входом первого накопителя постоянной памяти, первым входом накопителя оперативной памяти и третьим

15 входом второго накопителя постояннои памяти, а второй выход — соединен со вторым входом накопителя оперативной памяти, вторым входом первого накопителя постоянной памяти, вторым входом второго накопителя постоянной памяти.

Недостатком такого устройства является невозможность одновременного считывания информации из долговременной н оперативной памяти. Поэтому использование

743023 оперативной памяти в качестве устройства коррекции информации в ДЗУ требует сложного внешнего устройства управления, обеспечивающего сбор и совместную обработку информации из оперативной и долговременной памяти. S

Цель изобретения — повышение быстродействия устройства.

Это достигается тем, что устройство содержит блок элементов И, инвертор и два элемента ИЛИ, при этом соответствующие выходы накопителей постоянной памяти соединены со входами блока элементов И, другой вход которого соединен с выходом инвертора, вход которого подключен к выходу первого элемента ИЛИ, первый и второй выходы накопителя оперативной памяти соединены соответственно с первыми и вторыми входами первого и второго элементов ИЛИ, а третий и четвертый вход второго элемента ИЛИ соответственно соединены с первым и вторым выходами блока элементов И.

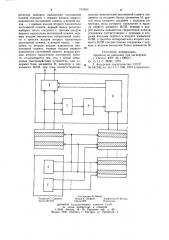

На чертеже приведена блок-схема запоминающего устройства для коммутационной системы связи.

Устройство содержит два накопителя 1, 2 постоянной памяти и накопитель 3 оперативной памяти, регистр,4 выборки числа, регистр 5 выборки накопителя постоянной памяти, блок элементов И 6, первый элемент ИЛИ 7, второй элемент ИЛИ 8, инвертор 9.

Устройство работает следующим образом.

В накопителях 1 и 2 постоянной памяти з0 записана информация, определяющая работу коммутационной системы в различных случаях. Например, если устройство используется в системе связи с подвижными объектами, то в каждом из накопителей 1 и 2 записывается программа работы системы

ЗЯ при движенйи подвижного объекта по одной из возможных трасс или в одном из районов, т. е. накопители 1 и 2 являются библиотекой программ работы коммутационной системы. 46

Для работы коммутационной системы одновременно используется программа, записанная в одном накопителе 1, которая соответствует текущей ситуации, например, трассе движения подвижного объекта. Если эта программа подлежит изменению, например, при временном или экстренном изменении трассы, когда перепрограммирование соответствующего накопителя 1 нецелесообразно или невозможно из-за ограничения времени, то новая программа полностью или в только та ее часть, которая отличается от старой программы, вводится в накопитель

3 оперативной памяти.

Процессор коммутационной системы (на чертеже не показан) для своей работы запрашивает программу из устройства памяти.

При этом регистр 4 выборки числа обращается к одному из накопителей 1 или 2, причем, именно к тому, в котором хранится нужная часть программы.

Кроме того, регистр выборки накопителя 5 постоянной памяти обращается к определенному числу выбранного накопителя 1 или 2, обеспечивая выдачу на выходы накопителя 1 или 2 информации, хранящейся в выбранном числе выбранного накопителя.

Информация с выходов поступает на входы блока элементов И 6.

Одновременно с помощью регистра 4 выборки числа процессор обращается к аналогичному числу накопителя 3 оперативной памяти, обеспечивая выдачу на его выходы хранящейся в данном числе информации. Информация с выходов накопителя 3 оперативной памяти поступает на входы второго элемента ИЛИ 8 и на входы первого элемента ИЛИ 7.

Если в опрашиваемом в данный момент числе накопителя 3 оперативной памяти не записано никакой информации, то на выходах накопителя 3 информация не появляется. При этом сигналы с выходов накопителя 1 и 2 постоянной памяти проходят через блок элементов И 6 и второй элемент ИЛИ 8.

Если в опрашиваемом числе накопителя оперативной памяти 3 записана информация, то на выходах этого накопителя появляются соответствующие сигналы, которые через первый элемент ИЛИ 7 и инвертор 9 воздействуют на управляющий вход блока элементов И 6 и запирают элементы И 6. При этом сигналы с выходов накопителя 1 и 2 постоянной памяти не поступают на входы блока элементов И 6. В то же время на выходы запоминающего устройства через второй элемент ИЛИ 8 проходят сигналы с выходов накопителя 3 оперативной памяти.

Таким образом, обеспечивается преимущественное прохождение на выходы запоминающего устройства информации, записанной в оперативном накопителе и тем самым обеспечивается коррекция программы, записанной в накопителях постоянной памяти.

Запоминающее устройство для коммутационной системы связи позволяет упростить устройство управления коммутационной системы, обеспечивающего сбор и совместную обработку информации из оперативной и долговременной памяти.

Эффективность данного запоминающего устройства заключается также и в том, что оно ускоряет процесс коррекции любой части программы работы коммутационной системы.

Формула изобретения

Запоминающее устройство для коммутационной системы связи, содержащее два накопителя постоянной памяти и один накопитель оперативной памяти, регистр вы» борки числа и регистр выборки накопителя постоянной памяти, при этом первый выход

743023

Составитель В. Вакар

Редактор С. Суркова Техред К. Шуфрнч Корректор М. Вигула

Заказ 3474/44 Тираж 662 Подписное

ПНИИПИ Государственного комитета СССР по делам изобретений и открытий! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент>, г. Ужгород, ул. Проектная, 4 регистра выборки накопителя постоянной памяти соединен с первым входом первого накопителя постоянной памяти, а второй выход — с первым входом второго накопителя постоянной памяти, первый выход регистра выборки числа соединен с третьим входом первого накопителя постоянной памяти, первым входом накопителя оперативной памяти и третьим входом второго накопителя постоянной памяти, а второй выход — соединен со вторым входом накопителя оперативной памяти, вторым входом первого накопителя постоянной памяти, вторым входом второго накопителя постоянной памяти, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит блок элементов И, инвертор и два элемента ИЛИ, пои этом соответствующие выходы накопителей постоянной памяти соединены со входами блока элементов И, другой вход которого соединен с выходом инвертора, вход которого подключен к выходу первого элемента ИЛИ, первый и второй выходы накопителя оперативной памяти соединены соответственно с первыми и вторыми входами первого и второго элементов

ИЛИ, а третий и четвертый вход второго элемента ИЛИ соответственно соединены с первым и вторым выходами блока элементов И. ю

Источники информации, принятые во внимание при экспертизе

1. Патент ФРГ № 1190517, кл. G 11 С 29/00, 1973.

2. Авторское свидетельство СССР № 491156, кл. G 11 С 17/00, 1974 (прототип) .