Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскна

Социалистические

Республик (li) 743031

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свид-ву— (22) Заявлено03,04.78 (2I ) 2600731/18-24 с присоединением заявки М(23) Приоритет

Опубликовано 25.06-80. Бюллетень №23

Дата опубликования описания 28.06.80 (51) M. Кл.

611 С 11/00 тевудерстееииый квнитет

СССР вв делан изебретеиий и атирытий (53) УДK681.327. .66 (088.8) (72) Авторы изобретения

В. С. Голубев и Ю. В. Герасимов (7I ) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике.

Известны запоминающие устройства, содержащие накопитель, датчики кода адреса, дешифраторы адреса, группы элементов И и ИЛИ, обеспечивающих подклю- чение датчика кода адреса к дешифратору адреса, входных и выходных информационных шин к соответствующим шинам устройства (1). то

Недостатком устройства является то, что для случая записи многоразрядного кода требуется введение дополнительного оборудования в разрядную часть ЗУ (согласующие устройства, дополнительные

15 разряды накопителя) или снижение частоты обращения к запоминающему устройству, которое связано с дополнительными затратами времени на формирование кода адреса для записи (считывания) избыточных разрядов, информационного кода.

Наиболее близким по технической сутцности является запоминающее устройство, которое содержит накопитель, дешифратор адреса, датчик кода адреса с выходами, подключенными непосредственно к коммутатору и датчик кода адреса с выходами, подключенными к коммутатору через инверторы (датчик кода адреса с прямыми и инверсными выходами), коммутатор (первая и вторая группы элементов И), схем выделения сигналов (третья и четвертая группы элементов И), элементы

ИЛИ, делители частоты, схемы формирования контрольных символов (2J, Недостаток этого устройства — ограниченные возможности для случая записи информационного кода с числом разрядов, превышающим число разрядов нако пителя.

Цель изобретения- расширение области применения устройства при условии минимальных временных и аппаратурных затрат за счет записи информационного кода с числом разрядов, превышающим число разрядов накопителя.

7430

31 4 верснвму колу адреса. Б режиме Гапись (на шину 16 подается сигнал, разрешающий запись) одна поповина информационного кода, подаваемого на шины 15 и поступающая на входы элементов 10 И, по сигналу опрос записывается в накопитель по прямому коду адреса, а вторая половина информационного кода, поступающая на входы элементов И 11 по сигналу опроса, задержанного элементом 12, записывается в накопитель по инверсному коду адреса.

B режиме считывание на шину 17 подается сигнал, разрешаю>пий считывание.

При этом сигнал "опрос обеспечивает считывание одной половины информационного кода, записанного по прямому коду адреса, а после задержки элементом 12 также и второй половины информационного кода, записанного по инверсному копу адреса.

Предложенное устройство обладает большими возможностями. Оно обеспечивает хранение как информационного кода с числом разрядов, не превышающим число разрядов накопителя, так и информационного кода, число разрядов которого превышает (не более чем в 2 раза) число разрядов накопителя. При этом емкость накопителя используется зффектив но.

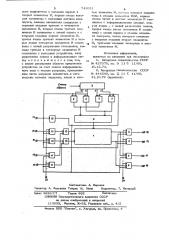

Устройство содержит накопитerrb 1, 35 дешифратор 2 адреса, датчик 3 кода апреса, имеющий прямые выходы 4 и инверсные выходы 5, первые, вторые, третьи, четвертые пятые и шестые элементы 6-11 И, элемент 12 задержки, элементы 13 ИЛИ, шину 14 опроса, информационные шины 15, шину 16 разрешения записи, шину 17 .разрешеыия считывания и выходы 18 устройства.

Устройство работает следующим образом.

По сигналу смена адреса, поступающему íà ахоп датчика 3, кода адреса, на его выходах 4 и 5 вырабатываются соответственно прямой и инверсыый коды адреса. Опрос накопителя осуществляется при поступлении сигнала опрос на шину 14. При этом накопитель опрашивается вначале по адресу, 55 соответствующему прямому коду адреса, а затем тот же импульс опроса, задержаыный элементом 12 задержки 5 обеспечивает опрос накопителя по ин3

Поставленная цель достигается тем, что в запоминающее устройство содержащее накопитель, одни из входов которого соединены с выходами элементов

ИЛИ, другие входы накопителя соедине5 ны с выходами дешифратора адреса, входы которого подключены к выходам первых и вторых элементов И, первые входы которых соединены с выходами датчика кода адреса, выходы накопителя соединены с первымл входами третьих и четвертых элементов И, вторые входы третьих элементов И соединены с шиной опроса и с вторыми входами первых weментов И, третьи входы третьих элементов И и вторые входы четвертых элементов И соединены с шиной разрешения считывания, выходы третьих и. четвертых элементов И соединены с выходами устройства, шину разрешения записи и ин-. 20 формационные шины, введены элемент задержки, пятые и шестые элементы И, выходы которых подключены к входам элементов ИЛИ, первые входы пятых и шестых элементов И соединены с информационными шинами, вторые входы — с шиной разрешения записи, третьи входы пятых элементов И соединены с шиной опроса и входом элемента задержки, выход которого соединен с вторыми входами вторых элементов И, третьими входа ми четвертых и шестых элементов И.

Сущность изобретения, поясняется чертежом.

Полученный эффект достигается минимальными аппаратурными и временными затратами. Не требуется значительные аппаратурные затраты на дополнительные разрядные блоки согласования входов и выходов устройства с входными и выходными шинами накопителя, имеющими место при увеличении разрядов накопителя для записи многоразрядного кода, не требуется существенных временных затрат для смеыы кода адреса в датчике кода адреса, имеющих место при использовании малоразрядного накопителя для записи многоразрядного информационного кода путем деления информационного кода на части и записи каждой части по вновь сформированному коду адреса в датчике кода адреса.

Формула изобретения

Запоминающее устройство, содержащее ыакопитель, одыи из входов которого соединены с выходами элементов ИЛИ, другие входы накопителя соединены с выходами дешифратора адреса, входы кото74303

Составитель A. Воронин

Редактор А. Федькина Твхред И. Нипц Корректор Г. Назарова

Заказ 3626/17 Тираж 662 одписное

ЦНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

113035,. Москве, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 рого подключены к выходам первых и вторых элементов И, первые входы которых соединены с выходами датчика кода адреса, выходы накопителя соединены с первыми входами третьих и четвертых элементов И, вторые входы третьих элементов И соединены с шиной опроса и с вторыми входами первых элементов И, третьи входы третьих элементов И и вторые входы четвертых элементов И соединены с шиной разрешения считывания, выходы третьих и четвертых элементов И соединены с выходами устройства, шину разрешения записи и информационные шины, о т л и ч а ю щ е е с я тем, что, с цепью расширения области применения устройства за счет записи информацион-ного кода с. числом разрядов, превышающим число разрядов накопителя,в него введены элемент задержки, пятые, и шес1 6 тые элементы И, ам оды которых подклю чены к входам элементов ИЛИ, первые входы пятых и шестых элементов И соединены с информационными шинами. вторые входы — с шиной разрешения записи, третьи входы пятых элементов И соединены с шиной опроса и входом элемента задержки, выход которого соединен с вторыми входами вторых элементов

И третьими входами четвертых и шестых элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 427379, кл. Ь 11 С 11/00, 10. 12.71.

2. Авторское свидетельство СССР

¹ 444240, кл. (д 11 С 11/00, 31.10,72 (прототип).