Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii 743035

-е (61) Дополнительное к авт. свил-ву— (22) Заявлено31.03.78 (2! )2596714/18-24 (51) M. Кл. с присоединение и заявки,№

5 11 С 17/00

Государственный комитет (23 ) П риоритет— до делам изобретений и открытий

Опубликовано 25.06.80. Бюллетень № 23

Дата опубликования описания 28.06.80 (53) УДК 681.327.. 6(088.8) (72) Авторы изобретения

И. М. Соколов и А. В. Николаев (7т) Заявитель (54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО

Изобретение относится к вычислител ной технике и может быть использовано в цифровых вычислительных машинах, в устройствах ввода-вывода, в устройствах управления и в устройствах обработки информации.

Известны запоминающие устройства, построенные на интегральных микросхемах ОЗУ с использованием биполярных и МОП-транзисторов f13 .

Известно запоминающее устройство, каждое число в котором образовано набором И. =* микросхем ОЗУ, параллельно обьединеннык по адресным шинам и по шинам управления, и содержащие накопи15 тель, первые выходы которого соединены с одними из входов коммутаторов,, дешифратор, входы которого соединены с вторыми выходами накопителя, а выходы дешифратора связаны с другими входами коммутаторов. Я, Наиболее близким техническим решением к данному является устройство, содержащее микросхему ОЗУ (где й2

-разрядность слов, выбираемых из запоминающего устройства, причем, предполагается, что в каждой микросхеме ОЗУ .хранятся только одноразрядные слова), при этом каждая микросхема ОЗУ состоит из матрицы элементов памяти, I адресные шины которой подключены к адресным шинам микросхемы ОЗУ через дешифратор адреса, информационные шины устройства с о еди иены ч ерез оди н элемент И с выходными информационными шинами, а через другой элемент И с выходными информационными шинами микросхемы ОЗУ, управляющие входы элементов И соединены через блок управления с упра вляющи ми ши нами микросхемы ОЗУ. Входы дешифраторов адреса всех микросхем ОЗУ подключены параллелт нок выходам регистра адреса, входы которого подключены к адресным входам запоминающего устройства. Входы блоков управления всех микросхем ОЗУ связаны с управляющими входами запоминающего устройства. Информапионные

55 входы запоминающего устройства подключены ко входам элементов И соответствующих микросхем ОЗУ, а информационные выходы запоминающего устройства связаны со входами элементов

И соответствующих микросхем ОЗУ Г31

Недостатком этого устройства является то что B многопрограммньех ЦВМ универсального типа и в ОЗУ одновременно размещается несколько рабочих прогреми которые выполняются B принятой последовательности. В этом случае ошибка при формировании адреса приводит к считыванию или записи и информациц в

ОЗУ по этому ошибочному адресу, который может принадлежать даже другой, не выполняемой, программе, что приводит к искажению предлагаемой информации и к снижению надежности работы запоми нающего устройства.

Цель изобретения — повышение надежности работы запола нающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее регистр адреса, подкл|оченный через дешифраторы к матричным накопителям, выходы которых подключены через элементы И к информационным входам и выходам устройства, и блоки управ лепин, введены дополнительный элемент

: И, коммутатор, элементы ИЛИ и дополнительный дешифратор, входы которого соединены с выходами регистра адреса, а выходы через соответствующие элементы ИЛИ вЂ” с входами коммутатора, выход которого подключен z одному из входов дополнительного элемента И, другой вход дополнительного элемента И подключен к шине записи,, а выход — к соответствующим входам блоков управления.

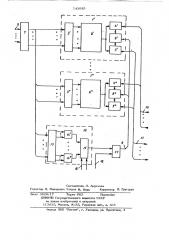

На чертеже представлена блок-схема устройства.

Устройство содержит микросхемы

1 ОЗУ (где и — .разрядность слов, выбираемых из запоминающего устройства, причем предполагается, что в каждой микросхеме ОЗУ хранятся только одноразрядные слова), каждая микросхема 1

ОЗУ состоит из матричного накопителя

2, адресные шины которого подключены к адресным шинам микросхемы 1 ОЗУ через дешифратор Э адреса, информационные шины устройства 2 соединены через элемент 4 И с входными информФционными шинами, а через элемент 5И с выходными информационными шинами микросхемы 1 ОЗУ управляющие входы

5 4 элементов 4 и 5 И соединены через блок 6 управления с управляющими шинами микросхемы 1 ОЗУ. Входы дешифраторов 3 адреса всех микросхем 1 03> подключены параллельно к.выходам регистра 7 адреса, входы которого подключеныы к адр ес ным входам 8 за номи наюшего устройства. Входы блоков 6 управления всех микросхем 1 ОЗУ соединены с управляющим входом 9. Информационные входы 10 запоминающего устройства подключены ко входам элементов 4 И соответствующих микросхем 1 ОЗУ, а информационные выходы 11 запоминающего устройства соединены со входами элементов 5 И с оотв етствуюши х микросх ем 1

ОЗУ. Селектор 12 адресов состоит из дешифратора 13, выходы которого соединены через К-многовходовых элементов 14 ИЛИ с соответствующими входами коммутатора 16 (где К вЂ” количество используемых программ в ОЗУ). При этом управляющие входы 1 6 коммутат<>ра 15 соединены с внешним устройством управления, а.выход коммутатора 15 подключен ко входу элемента 17 И, другой вход 18 которой также соединен с внешним устройством управления, а выход элемента 17 И подключен ко входу

9. Входы дешифратора 13 подключены к выходам регистра 7 адреса.

Устройство работает следующим образом.

Перед началом работы на один из входов 16 подается, напряжение из внешнего устройства управления. При этом к выходу селектора 12 адресов подключается только один из многовходовых элементов 14 ИЛИ, обеспечивающий выборку адресов только для заданной программы ч обеспечивающий блокировку выборки адресов из других, не заданных, программ, записанных в матрицы элементов 2 памяти микросхем 1 ОЗУ. Далее, при поступлении сигналов записи на входы 18 запоминающего устройства и приема кода адреса со входов 8 в регистр 7 адреса осуществляется запись информации, поступающей со входов 10, по одному и тому .же разрешенному адресу во все й. =микросхем 1 ОЗУ, причем каждый вход 10 соединен со входом элемента 4 И только одной микросхемы 1 ОЗУ. При поступлении сигналов считывания на входы 18 запоминающего устройства и приема кода адреса со входом 8 в регистр 7 адреса осуществляет ся считывание информации по одному и

743035 гому же разрешенному адресу во всех

И-микросхемах 1 ОЗУ. На выходе каж.— дой микросхемы 1 ОЗУ появится выходной информационный сигнал, совокупность таких сигналов, появляюшихся на выхо- дах 10 запоминающего устройства соответствует одному разрядному слову. запоминающего устройства.

Запоминаюшее устройство, в отличие от известного позволяет повысить надежность работы его за счет: исключения возможности ошибочных обрашений к не заданным программам, записанным в матричных накопителях микросхем ОЗУ исключения возможности искажения информации, записанной в матричных накопителях Микросхем ОЗУ обеспечения возможности обходить неисправные ячейки памяти как .",:в процессе эксплуатации, так и при изготовлении запоминаюшего устройства.

Формула изобретения

Запоминаюшее устройство, содержащее регистр адреса, подключенный через дешифраторы к матричным накопителям, выходы которых подключены через элементы И к информационным входам и выходам устройства, и блоки управления> подключенные к элементам И, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно- содержит дополнительный элемент

И, коммутатор, элементы ИЛИ и дополнительный дешифратор, BxoRbf которого соединены с выходами регистра адреса, а выходы через соответствуюшие элементы ИЛИ вЂ” с входами коммутатора, выход которого подключен к одному из входов дополнительного элемента И, другой вход дополнительного элемента

15 И подключен к шине записи, а выход— к соответствующим входам блоков управления.

Источники информации, принятые во внимание при экспертизе

20 1. Старов Ф. Г. и др. Полупроводниксвые интегральные запоминающие устройства,"Энергия, Ленинградское отделение, 1973, с. 62-77, рис. 4-3,45,4-8 и 4-10.

21 2. Преснухин Л. Н. и др. Цифровые вычислительные машины. М., Высшая школа, 1974, с. 214-216, рис.4.51.

3. Преснухин Л. И. и др. цифровые вМчислительные машины. М., Высшая

30 школа, 1974, рис. 4.51 а (прототип).

;43035

Составитель Л. Амусьева

Г едактор П. Макаревич Техред H. Яинц Корректор ГГ ГР"горук

3аказ 3626/3.7 Тирачс 662 Подписное

11НИИПИ Государственного комитета СССР по делам изобретений и открытий

313035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ПГ1П Патент, r. Ужгород, ул. Проектная, 4