Устройство сдвига цифровой информации

Иллюстрации

Показать всеРеферат

О П -9Г С А И Е

ИЗЬБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

»»743036

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 25.12.76 (21) 2435021/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.

G 11 С 19/00

Государственный комитет

СССР

Опубликовано 25.06.80. Бюллетень № 23

Дата опубликования описания 05.07.80 (53) УДК 681.327..67 (088.8) о ленам изобретений и открытий (72) Авторы изобретения

В. В. Куванов, В. М. Миролюбский, Г. А. Кузьмин и В. И. Редченко (71) Заявитель (54) УСТРОЙСТВО СДВИГА ЦИФРОВОЙ ИНФОРМАЦИИ

Изобретение относится к вычислительной технике и может быть использовано в различных устройствах преобразования последовательного парафазного кода в параллельный код.

Известны устройства сдвига цифровой информации, состоящие из регистра, ячейки которого содержат по четыре элемента И и по два триггера (1) .

Недостатками их являются сложность и невысокое быстродействие.

Наиболее близким по техническому реше- to нию к предлагаемому является устройство сдвига цифровой информации, содержащее два регистра сдвига на триггерах, входы каждого из которых соединены с выходами предыдущего триггера через вентили, управляющие входы которых подключены к соответствующим шинам синхронизации (2) .

Кроме того, это устройство содержит счетный триггер, два элемента И и элемент

ИЛИ, образующие формирователь синхроимпульсов, подключенный своими выходами к шинам синхронизации.

Это устройство имеет большее быстродействие, однако его недостатком является сложность из-за большого количества элементов И, триггеров и связей между элементами, что обусловливает также низкую надежность.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в устройство сдвига цифровой информации, содержащее регистр сдвига на Д-триггерах, вход сброса каждого из которых соединен с шиной сброса, тактовый вход — с выходом соответствующего первого и второго элементов И, а информационный вход — с инверсным выходом предыдущего,Ц -триггера, первые входы первого и второго элементов

И соединены с выходом элемента ИЛИ и со счетным входом Т-триггера, вторые входы первого и второго элементов И соединены соответственно с прямым и инверсным выходами Т-триггера, входы элемента ИЛИ соединены с первой и второй парафазными входными шинами, введен параллельный регистр на Д-триггерах, информационный вход каждого из которых соединен со второй парафазной входной шиной, вход разрешения — с прямым выходом соответствующего Д-триггера регистра сдвига, тактовый вход — с соответствующим выходом

743036 первого и второго элементов И, а вход сброса — с шиной сброса, подключенной к входу сброса Т-триггера.

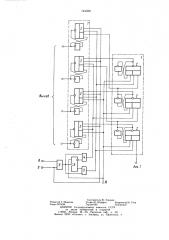

На чертеже представлена функциональная схема устройства.

Устройство содержит регистр сдвига 1 на Д-триггерах 2, первый 3 и второй 4 элементы И, элемент ИЛИ 5, Т-триггер 6, параллельный регистр 7 на Д-триггерах 2, первую 8 и вторую 9 парафазные входные шины, шину сброса 10. Выходом устройства являются выходы Д-триггеров 2 параллельного регистра 7.

Перед началом сдвига на шину сброса

10 подается импульс, который устанавливает в исходное состояние регистры 1 и 7 и Т-триггер 6, характеризующиеся высоким уровнем на инверсном выходе Т-триггера 6 и низкими уровнями на инверсных выходах Д-триггеров 2 регистра сдвига 1.

При поступлении единичной информации высокий уровень поступает на информационные входы всех Р -триггеров 2 параллельного регистра 7, однако только первый

Д-триггер 2 этого регистра 7 изменяет свое состояние на обратное. По заднему фронту импульсов на первой 8 или второй 9 парафазных информационных входных шинах

Т-триггер 6 изменяет свое состояние, тактируя в дальнейшем запись во второй Д-триггер 2 параллельного регистра 7. Поступление второго импульса информации переключает второй Д-триггер 2 регистра сдвига 1, закрывая запись в первый триггер 2 параллельного регистра 7. При этом второй триггер 2 параллельного регистра 7 или изменяет свое состояние на обратное (при единичной информации на входе),или остается в исходном состоянии.

Последующая запись информации в

Д-триггеры 2 параллельного регистра 7 происходит аналогично и определяется разрядностью регистров 1 и 7.

Предлагаемое устройство имеет меньшее количество элементов.

Формула изобретения

Устройство сдвига цифровой информации, содержащее регистр сдвига на Д-триггерах, вход сброса каждого из которых соединен с шиной сброса, тактовый вход — с выходом соответствующего первого и второго элементов И, а информационный входс инверсным выходом предыдущего Д-триггера, первые входы первого и второго элементов И соединены с выходом элемента

ИЛИ и со счетным входом Т-триггера, вторые входы первого и второго элементов И соединены соответственно с прямым и инверсным выходами Т-триггера, входы элемента ИЛИ соединены с первой и второй го парафазными входными шинами, отличающееся тем, что, с целью упрощения устройства, оно содержит параллельный регистр на Д-триггерах, информационный вход каждого из которых соединен со второй парафазной входной шиной, вход разрешения— с прямым выходом соответствующего Д-триггера регистра сдвига, тактовый вход — с соответствующим выходом первого и второго элементов И, а вход сброса — с шиной сброса, подключенной к входу сброса Т-триггера.

Источники информации, принятые во внимание при экспертизе

1. Шигин А. Г. Цифровые вычислительные машины. М., Энергия, 1971, с. 178 — 179. и 2. Авторское свидетельство СССР № 476601, кл. G 11 С 19/00, 1972 (прототип).

743036

Составитель Ю. Ушаков

Редактор Т. Иванова Техред К. Шуфрич Корректор Н. Стец

Заказ 3474/44 Тираж 662 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент>, г. Ужгород, ул. Проектная, 4