Умножитель частоты с переменным коэффициентом умножения

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 0) 0777 (21) 2502192/18-21 с присоединением заявки Мо (23) Приоритет—

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано 25.06.80,Бюллетень М 23

Дата опубликования описания 2506.80 (72) Авторы изобретения

В.Э.Штейнберг, Б.П.Касич и P.Ã.ßêóïîâ (71) Заявитель (54) УМНОЖИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ

КОЭФФИЦИЕНТОМ УМНОЖЕНИЯ

Изобретение относится к области кодирования и преобразования информации и может найти применение при разработке цифровых измерительных устройств и систем управления в качестве цифрового узла преобразования частоты повторения импульсов с пробным коэффициентом передачи.

Известны умножители частоты с переменным коэффициентом умножения, содержащие счетчик, цепи установки кода в счетчик, дешифратор и элемент задержки, предназначенное для деления частоты повторения импульсов на коэффициенты, заданные кодом. 15

Недостатком известного устройства является реализация только целочисленных коэффициентов пересчета и ограниченный диапазон их значений (1), Известны также умножитель частоты с переменным коэффициентом умножения, содержащий счетчик импульсов, первый вход которого соединен с выходом логического элемента ИЛИ, а выходы соединены соответственно со входами двух блоков ключей и первым входом регистра памяти, второй вход которого соединен с первой шиной управления и первым входом импульсного сумматора, второй вход которого соединен со вто= рой шиной управления, третий вход— с входной шиной, а выход подключен к первому входу логического элемента

ИЛИ, причем входы управления первого блока ключей соединены с шиной кода управления (2).

Недостатком известного умножителя является узкий диапазон изменений коэффициента умножения.

Целью настоящего изобретения является расширение диапазона изменения коэффициента умножения.

Поставленная цель достигается тем, что в умножитель частоты с переменным коэффициентом умножения, содержащий счетчик импульсов, первый вход которого соединен с выходом логического элемента ИЛИ, а выходы соединены соответственно со входами двух блоков ключей и первым входом регистра памяти, второй вход которого соединен с первой шиной управления и первым входом импульсного сумматора, второй вход которого соединен со второй шиной управления, третий вход ° с входной шиной, а выход подключен к первому входу логического элемента

ИЛИ, причем входы управления первого

743180

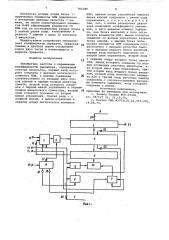

25 блока ключей соединены с шиной кода управления, введены элемент задержки, два блока вентилей и блок логических элементов ИЛИ, выход которого соединен со входом управления второго блока ключей, а выходы блока логи ческих элементов ИЛИ соединены соответственно с выходом регистра памяти и выходом первого блока вентилей, первый вход которого подключен ко второй шине управления, второй входк первому входу второго блока вентилей, выход которого соединен со входом установки счетчика импульсов и ко второй шине кода управления, причем второй вход второго блока вентилей, второй, вход логического элемен- 15 та ИЛИ и третий вход регистра памяти соединены с соответствующими выходами элемента задержки, вход которого соедпнен с шиной, На фиг.1 приведена структурная 20 электрическая схема умножения частоты с переменным коэффициентом ум ножения; на фиг.2 — схема импульсов сумматора; на фиг.3 — схема выпол- нения соединений первой и второй .группы вентилей, группы схем ИЛИ и регистра хранения для одного разряда.

Устройство содержит импульсный сумматор 1, логический элемент 2

ИЛИ, счетчик 3 импульсов, блоки 4 и 5 ключей, элемент 6 задержки, ре..истр 7 памяти, первый и второй блоки 8 и 9 вентилей, блок 10 логических элементов ИЛИ. Устройство также содержит входные шины 11 и 12 импульс-З5 ного сумматора 1, шины 13 и 14 управления, шину 15 приведения кода знаменателя элемента 6 задержки, шины

16, 17 18 первого, второго и третьего выходов элемента 6 задержки, шины gp

19 и 20 кода управления, шины 21 установки счетчика 3 импульсов., шины

23 выходов счетчика 3 импульсов и выходную шину 23 устройства.

Импульсный сумматор 1 содержит триггеры 24, вентили 25 и 26, элемент 27 ИЛИ.

Узлы устройства связаны следующим образом. Первый счетный вход импульсного сумматора 1 подключен к входной шине 11, второй счетный вход подклю.чен .к входной шине 12, связанной с объединенными выходами второго блока

5 ключей, первый управляющий вход объединен с первыми входами первого бл ка 8 вентилей и подключен к шине 55

13 управления, второй управляющий вход объединен со входом установки в нуль регистра 7 памяти и подключен к шине 14 управления, а выход импульсного сумматора 1 подключен к ц первому входу элемента 2 ИЛИ. Вход элемента 6 задержки подключен к шине

15.приведения кода знаменателя, первый выход 16 соединен со вторыми входами второго блока 9 вентилей, второй в ход 1 7 соединен со вторым в ходом элемента 2 ИЛИ, выхоц которой подключен ко входу счетчика 3 импульсов.

Третий выход 18 элемента 6 задержки подключен ко входу разрешения записи регистра 7 памяти. Вторые входы блока 8 вентилей объединены с первыми входами блока 9 вентилей и подключены к шинам 20 кода управления, Выходы блока 8 вентилей подключены к первым входам блока 10 логических элементов ИЛИ, Выходы блока 9 вентилей подключены ко входам 21 установки счетчика 3 импульсов, единичные выходы 22 которого соединены со входами регистра 7 памяти, инверсные выходы которого подключены ко вторым входам блока 10 логических элементов ИЛИ, выходами связанных с потенциальными входами второго блока 5 ключей, импульсные входы которых подключены к нулевым выходам счетчика 3 импульсов.

Импульсные входы первого блока 4 ключей подключены также к нулевым выходам счетчика 3 импульсов, потенциальные входы связаны с шинами 19 кода управления, а выходы объединены и подключены к выходной шине 23 устройства.

Элементы, образующие импульсный сумматор 1, связаны следующим образом. Счетный вход триггера 24 объединен с первым входом вентиля 25 и подключен к первой входной шине 11, второй вход вентиля 25 подключен к единичному выходу триггера 24, нулевой выход которого подключен к 7-К входам триггера, единичный вход которого соединен через первый управляющий вход с шиной 13 управления, а нулевой вход триггера 24 объединен с первым входом вентиля 26 и подключен ко второй входной шине управления 12.

Второй вход вентиля 26 подключен к шине 14 управления„ Выходы вентилей 25 и 26 подключены ко входам элелента 27 ИЛИ, выход которой соединен с выходом импульсного сумматора 1.

Устройство может работать в двух режимах: в режиме понижения частоты импульсов с коэффициентом передачи

Кп 4 1 и заданным отношением двух о чисел Я и &; в режиме частоты повторения импульсов с коэффициентом передачи Км, 1 и заданным также отношением чисел Q u P.

В режиме понижения частоты импульсов устройство работает следующим образом.

На шине 13 управления устанавливается разрешающий сигнал, а на шине

14 управления - запрещающий, в результате чего импульсный сумматор 1 устанавливается в режиме вычитания, регистр 7 памяти устанавливается в нулевое состояние;вентили блока 8 вентилей отпираются. При подаче .кода числа Р на шины 20 кода управления, 743180

50

Кп Ч /!! g

2 код числа Р инвертируется вентилями блока 8 вентилей и повторно инвертируется вентилями блока 9 вентилей.

При этом, поскольку регистр 7 памяти находится в нулевом состоянии, то на его инверсных выходах присутствуют единичные потенциалы, не препятствующие прохождению кода числа Р с выходов вентилей блока 8 через вентили блока 9 нентилей. Для этого необходимо, чтобы блоки 8 и

9 нентилей, а также блок логических элементов ИЛИ были выполнены на элементах И-НЕ.

При подаче числа Q на шины 19 кода управления, с объединенных выходов блока 5 ключей поступают импульсы на второй счетный вход 12 импульсного сумматора 1 и, поскольку они не совпадают по времени со входными импульсами, поступающими на первую входную шину 11, то с каждым импульсом с второй входной шины 12 триггер

24 устанавлинается в нулевое состояние, запирая вентиль 25. Следующий входной импульс, поступающий на счетный вход триггера. 24 и первый выход вентиля 25, на выход вентиля 15 не проходит, а только переключает триггер 24 в единичное состояние, при котором отпирается вентиль 25, Поскольку импульсный сумматор 1 реализует операцию вычитания импульсов, то коэффициент передачи двоичного умножения, образованного счетчиком 3 импульсов блок ключей 5 и импульсным сумматором 1, работающим в режиме вычитания, равен

К = — (1

tt p и изменяется в пределах от 1 до 1/2.

Коэффициент передачи двоичного умножени/, образованного счетчиком 3 импульсов и блока 4 ключей, равен

К = Q/2 где 2- разрядность счетчика 3 импульсов, а суммарный коэффициент передачи устройства в режиме понижения частоты равен

/ /!

КП/ — Kn Ke — Q/P < 1

/ представлен н дробной форме и задается отношением кодов чисел Q и Р.

В режиме повышения частоты импульсов устройство работает следующим образом.

На шине 14 управления устанавливается положительный потенциал, а на шине 13 управления †нулевой, .в результате чего блок 8 вентилей запирается, регистр 7 памяти освобож-. дается для приема кодон, триггер 24 принудительно устанавливается в единичное состояние, а вентиль 26 отпирается. Тем самым импульсный сумматор 1 реализует режим сложения входных импульсов, поступающих со входной

11 шины с импульсами обратной связи.

Поскольку коэффициент передачи двоичного умножения, образованного счетчиком 3 импульсов блока 5 ключей и импульсного сумматора 1, работающего в режиме сложения, равен

2 ФФ

2!!-P для обеспечения коэффициента переФ дачи К/!,, равного

К/ =

Ф необходимо на потенциальные входы блока 5 ключей подать дополнительный код числа P. Для этого по окончании установки кода числа Р на шинах 20 кода управления или в момент окончания изменения кода числа Р, н зависимости от условий использования устройства, на шину 15 приведения кода знаменателя элементов задержки подается импульс, который через короткие промежутки времени появляется поочередно на шинах 16, 17 и. )8 элемента

6 задержки. При этом импульсом, поступившим с шины 16, отпираются блок 9 вентилей и в счетчик 3 импульсов по шинам установки записывается инверсный код числа P. Вторым импульсом с шины 17 элемента б задержки н счетчик 3 импульсов добавляется единица, а третьим импульсом с шины 18 в регистр 7 памяти с шины 22 записываегся иннерсный и увеличенный на единицу

З5 код числа Р. На следующем примере видно, что в регистр 7 памчти записывается дополнительный код числа P: допустим, что число Р=9, или, в двоичном коде, 1001. Тогда в счетчик 3

40. импульсов запишется первым импульсом код 0110, а после второго импульса в счетчике 3 импульсов зафиксируется число 1110, т.е. н регистр 7 памяти запишется третьим импульсом чис45 ло Р=7, обеспечивающее коэффициент

К, равный

К и. — р

Коэффициент передачи двоичного умножения, образованного счетчиком 3 импульсов блока 4 ключей, как и в первом режиме .работы устройства, ра-вен а суммарйый коэффициент передачи устройства s режим понышения частоты импульсов равен

/. // Q

К//.2. K tt К И р т.е. представлен также в дробной форме и задан отношением кодов чисел

ОиР.

743180

Поскольку вторые входы блока 10 логических элементов ИЛИ подключены к инверсным выходам регистра 7 па,мяти, то после инвертирования элементов И-НЕ образующими элементов 10

ИЛИ код на потенциальных входах блока . 5

5 ключей равен коду, записанному в регистр 7 памяти с шины 22 счетчика

3 импульсов.

Предлагаемое устройство обеспечивает коэффициенты передачи, представ- 1О ленные в дробной форме отношением кодов двух чисел и изменяющиеся в широких пределах.

Формула изобретения

Умножитель частоты с переменным коэффициентом умножения, содержащий счетчик импульсов, первый вход кото.рого соединен с выходом логического элемента ИЛИ, а выходы соединены 20 соответственно со входами двух блоков ключей и первым входом регистра памяти, второй вход которого соединен с первой шиной управления и первым входом импульсного сумматора, второй 25 вход которого соединен со второй шиной управления, третий вход - с входной шиной, а выход подключен к первому входу логического элемента

ИЛИ, причем входы управления первого блока ключей соединены с шиной кода управления, отличающийся тем, что, с целью расширения диапазона изменений коэффициента умножения, в него введены элемент задержки, два блока вентилей и блок логических элементов ИЛИ, выход которого соединен со входом управления второго блока ключей, а выходы блока логических элементов ИЛИ соединены соответственно с выходом регистра памяти и выходом первого блока вентилей, первый вход которого подключен ко второй шине управления, второй вход к первому входу второго блока венти лей, выход которого соединен со входом установки счетчика импульсов и ко второй шине кода управления, причем второй вход второго блока вентилей, второй вход логического элемента ИЛИ и третий вход регистра памяти соединены с соответствующими выходами элемента задержки, вход которого соединен с шиной.

Источники информации, принятые во внимание при экспертизе

1. Заявка Японии 950-29306, кл. 98/5/С 31, 31.10 75.

2. Патент США РЗ?53125,кл.30?-225, 14.08.73.

74 3180

Фиа2

Составитель В.Чижов

Техред Э. Фечо Корректор С.Шекмар

Редактор 3.Шубенко

Филиал ППП Патент, r. Ужгород, ул . Проектная, 4

Заказ 3630/19 Тираж 995- Подпи сн ое

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5