Делитель частоты импульсов

Иллюстрации

Показать всеРеферат

о и Й"А - йФе

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик ()743204

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополнительное к авт. саид-ау (22) Заявлено 12.04.77 (21) 2474958д 8 21 с присоединением заявки РЙ (51)М. Кл, Н 03 К 23/02

Гааударетамнпий кемитет

СССР иа делам изеаретений и аткрытий (23) Приоритет

Опубликовано 25.06.80. 61оллетеиь М 23

Дата опубликования описания 25.06.80 (53) УДК 621,374.8 (088.8) (72) Автор изобретения

А. С. Рыбаков (71) Заявитель

Рижский ордена Трудового Красного Знамени политехнический институт (54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ

Изобретение относится к импульсной технике.

Известен делитель частоты импульсов, содержащий регистр сдвига, триггер цикла, пусковое устройство, источник входной частоты, управляющий триггер, вход которого подключен к выS ходу ячейки регистра сдвига, и логические элементы И, соединенные с входами регистра сдвига (Ц.

Недостатком данного делителя является от1О носительная сложность.

Наиболее близким по технической сущиости к предлагаемому является делитель чаетоты импульсов, содержащий регистр сдвига, С вЂ” в

15 ход которого соединен со входной шиной, а

Д вЂ” вход подключен к выходу лоттиеского эле-. мента И вЂ” НЕ, входы которого соединены с выходами последних разрядов регистра сдвига, логический элемент НЕ, вход которого лодключен к выходу последнего разряда регистра сдвига,и выходной логический элемент И вЂ” НЕ (21, Однако данный делитель не обеспечивает иолучения дробного коэффициента деления.

11ель изобретения — получение дробного коэффициента деления.

Поставленная цель достигается тем, что в делитель частоты импульсов, содержащий регистр сдвига, С вЂ” вход которого соединен со входной шиной, а Д вЂ” вход подключен к выходу логи. ческого элемента И вЂ” НЕ, входы которого соединены с выходами последних разрядов регистра сдвига, логический элемент НЕ, вход которого подключен к выходу последнего разряда регистра сдвига, и выходной логический элемент И вЂ” НЕ, введены трехвходсвый элемент

И вЂ” НЕ и логический элемент ИЛИ, первые входы которых соединены с входной шиной, вторые входы соединены с выходом предпоследнего разряда регистра сдвига, третьи входы подключены к выходу логического элемента И вЂ” HE.

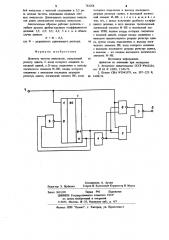

На чертеже приведена структурная электрическая схема описываемого делителя частоты.

Лелитель.частоты содержит регистр 1 сдвига, логический элемент И вЂ” НЕ 2, выходной логический элемент И вЂ” НЕ 3, логический элемент

НЕ 4, логический элемент ИЛИ 5, трехвходовый логический элемент И вЂ” НЕ 6. Входные сигналы

3 743204 поданы на входную шину 7, выходной сигнал снимается с выхода 8.

Принцип работы делителя заключается в следующем.

Рассмотрим работу устройства на примере делителя частоты следования импульсов с коэффициентом деления 2,5. Для получения такого коэффициента деления регистр 1 должен содержать три разряда, т. е. N = 3. В этом случае выходы регистра (N — 1) н и соответствуют 10 выходам второго и третьего разрядов регистра 1.

3а исходное состояние устройства принимается наличие уровней логического "0" на всех выходах регистра 1 сдвига. При этом уровнями д

"0", поступающими с N — 1 и N. выходов регистра, на выходе логического элемента И вЂ” НЕ 2 поддерживается логическая "1", которая поступает на Д вЂ вх регистра 1, На выходе логического элемента И-НЕ 6 присутствует логическая 2р

"1", поддерживаемая уровнем "О", поступающим с выхода и — 1 регистра 1. На выходе логического элемента ИЛИ 5 — логическая "1", поддерживаемая уровнем "Г с выхода логического элемента НЕ 4, на входе которого присутствует уровень "0", поступающий с выхода и регистра 1. Логические "1" с выходов логических элементов 5 и 6.поступают на входы логического элемента И-НВ 3, при этом íà его выходе присутствует . уровень логического "0", который Зр подается на выход S.

После окончания первого счетного импульса на входной шине 7 происходит сдвиг информации в регистре 1 на адин разряд, на выходе первого разряда появляется уровень "1" и в регистре устанавливается код 100. Других изменений сигналов на выходах элементов при этом не происходит.

После окончания второго счетного импульса происходит очередной сдвиг информации в ре- 4р гистре 1 на один разряд и в нем устанавливается код 110. Других изменений сигналов на выходах элементов не происходит.

Третий счетный импульс, поступивший на входную шину 7, открывает логический элемент 45

И вЂ” НЕ 6, так как на двух других его входах присутствуют уровни логических "1", поступающих с и — 1 выхода регистра 1 и с выхода логического элемента НЕ 4. На выходе логического элемента И-НЕ 6 появляется логический

"О", который, поступая иа вход логического элемента И-НЕ 3, вызывает появление на его выходе уровня "1", далее поступающего на вмход 8, После окончания третьего счетного импульса 55 происходит очередной сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 111. Логические "1". с й-1 и N выходов регистра, поступая на оба входа логичес4 кого элемента И вЂ” HF. 2, вызывают появление на его выходе уровня логического "0", далее поступающего на Д вЂ” вход регистра 1. Кроме того, "1" с N выхода регистра поступает на вход логического элемента НЕ, на выходе которого появляется уровень "0", который, воздействуя на один нз входов логического элемента И вЂ” НЕ 6, запирает его и íà его выходе появляется логическая "1", а так как на выходе логического элемента ИЛИ 5 также присутствует логическая "1", поддерживаемая уровнем

"1" с N — 1 выхода регистра, то на выходе логического элемента И вЂ” НЕ 3 появляется уровень логического "О", далее поступающий на выход 8.

После окончания четвертого счетного импульса происходит сдвиг информации в регистре 1 на один разряд, на выходе первого разряда появляется уровень "0" и в регистре устанавливается код 011. Других изменений сигналов на выходах элементов не происходит, После окончания пятого счетного импульса происходит очередной сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 001. Логический "О" с выхода и — 1 регистра, поступая на один иэ входов логического элемента И вЂ” НЕ 2, вызывает появление на

его выходе уровня логической "1", далее поступающего на информационный вход регистра

1. На всех трех входах логического элемента

ИЛИ 5 присутствуют уровни логического "О", поступающие с N — 1 выхода регистра 1, с выхода логического элемента НЕ 4 и с входной шины 7, поэтому на выходе логического элемента ИЛИ 5 устанавливается уровень логического "0", который, поступая на вход логического элемента И вЂ” FfE 3, вызывает появление на его выходе логической 1", далее поступающей на выход 8, Шестой счетный импульс, поступивший на входную шину 7, проходит логический элемент

ИЛИ 5 и, поступая на один нз входов логического элемента И вЂ” НЕ 3, вызывает появление на его выходе уровня логического "0", так как на другом его входе присутствует уровень

"1", поступающий с логического элемента

И вЂ” НЕ 6.

После окончания шестого счетного импульса в очередной раз происходит сдвиг информации в регистре 1 на один разряд и в нем устанавливается код 100.

После окончания каждого из последующих счетных импульсов происходит сдвиг информации в регистре 1 на один разряд, при этом регистр последовательно принимает пять устойчивых состояний, соответствующих кодам: 110, 111, 011, 001, 100, затем цикл работы устройства вновь повторяется. При этом на выходе 8 формируется выходной сигнал, представляющий со743204

Формула изобретения

20

Составитель А. Артюх

Редактор 3. Шубенко Техред Ж. Кастелевич Корректор И. Муска

Заказ 3631/20 Тираж,995 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная,4 бой импульсы с частотой следования в 2,5 раза меньше частоты следования входных счетных импульсов, Длительность выходных импульсов равна длительности входных импульсов.

Аналогичным образом работает делитель с любым другим ц>обно-кратным коэффициентом деления: 1,5; 2,5; 3,5; 4,5; 5 и т. д. в общем случае равным

К = N — 0,5, где Й вЂ” разрядность сдвигающего регистра. 30

Делитель частоты импульсов, содержащий регистр сдвига, С вЂ” вход которого соединен со входной шиной, а Д вЂ” вход подключен к выходу логического элемента И вЂ” НЕ, входы которого соединены с выходами последних разрядов регистра сдвига, логический элемент НЕ, вход которого подключен к выходу последнего разряда регистра сдвига, и выходной логический элемент И вЂ” НЕ, отличающийся тем, что, с целью получения дробного коэффициента деления, в него введены трехвходовый логический элемент И вЂ” НЕ и логический элемент ИЛИ, первые входы которых соединены с входной шиной, вторые входы соединены с выходом предпоследнего разряда регистра сдвига, третьи входы подключены к выходу логического элемента НЕ, вход которого соединен с выходом последнего разряда регистра сдвига, а выходы — ко входам выходного логического элемента И вЂ” НЕ.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 463234, кл. Н 03 К 23/02, 11.06.73.

2. Патент США N 3943379, кл. 307 — 225 й, 14.08.74,