Регенератор двоичных сигналов

Иллюстрации

Показать всеРеферат

О (."А-НИ E

ИЗОБРЕТЕНИЯ

Союз Советскнк

Соцналнстнческнк

Республик (ii> 743211

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 20.10,77 (21) 2535144/18-09 с присоединением заявки ¹ (23) Приоритет

Опубликовано 2506.80. Бюллетень ¹ g 3

Дата опубликования описания 2506.80 (51) м. кл.

Н 04 В 3/02

Государственный комитет

СССР но делам изобретений и открытий (53) УДК 621 394 (088. 8) (72) Автор изобретения

A . .Е. Крас ковс кий (71) Заявитель

Ленинградский ордена Ленина институт инженеров железнодорожного транспорта им. академика В.Н.Образцова (54) РЕГEHEPATOP ДВОИЧНЫХ СИГНАЛОВ

Изобретение относится к радиотехнике и может использоваться в аппаратуре передачи дискретной информации.

Известен регенератор двоичных сигналов, содержащий блок элементов буферной памяти, дна объединенных по входу распределителя для записи и считывания информации, задающий гене- 10 ратор, подключенный к входу блока синхронизации, и выходной триггер (11

Однако такой регенератор не обеспечивает высокой точности регенерации.

Цель изобретения — повышение точности регенерации.

Для этого в регенератор двоичных сигналов, содержащий блок элементов буферной памяти, два объединенных по входу распределителя для записи и считывания информации, задающий генератор, подключенный к входу блока синхронизации, и выходной триггер, введены асинхронный приемник, элемент ИЛИ, блок элементов записи, блок элементов считынания, блок элементов ИЛИ, ключ и последовательно соединенные блок добавления, блок вычитания, распределитель и коммутатор, один выход коммутатора через первый счетчик подключен ко нходу блока добавления, второй выход через второй счетчик подключен к другому входу блока вычитания, а третий выход подключен к другим входам первого и нторого счетчиков, причем выходы асинхронного приемника подключены к входам блока элементов записи, а через элемент ИЛИ вЂ” к другому входу коммутатора и другому нходу блока синхронизации, первый выход которого подключен к другому входу блока добавления, а второй выход подключен к входу ключа, выход которого подключен к управляющему входу первого распределителя для записи и считывания информации, разрядные выходы которого подключены к входам блока элементов считывания, выходы которого через блок элементов ИЛИ подключены к входам выходного триггера, при этом четвертый выход коммутатора подключен к упранляющему входу второго распределителя для записи и считывания информации, разрядные выходы которого через последовательно соединенные блок элементов записи и блок элементов буферной

743211 пам-.:-.:. подключены к другим входам блока элементов считывания, причем выходы блоКа элементов памяти подключены соответственно к другим входам блока элементов записи, при этом соответствующий разрядный выход второго распределителя для записи и считывания информации подключен к другому входу ключа, а выход задающего генератора подключен к другому входу асинхронного приемника, при этом на третий вход ключа и другие входы первого и второго распределителей для записи и считывания информации подан сигнале установка нуля .

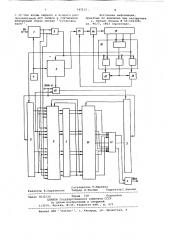

На чертеже дана структурная электрическая схема предложенного регенератора.

Регенератор двоичных сигналов содержит блок 1 элементов буферной памяти, распределители 2 .и 3 для записи и считывания информации, задающий генератор 4, блок 5 синхронизации, выходной триггер б, асинхронный приемник 7, элемент ИЛИ 8, блок 9 элементов записи, блок 10 элементов считывания, блок 11 элементон ИЛИ, ключ 12, блок 13 добавления, блок 14 вычитания, распределитель 15, коммутатор 16, счетчики 17 и 18.

Устройство работает, следующим образом.

Сигнал двоичной информации поступает на вход асинхронного приемника

7, на выходах которого. в зависимости от входного сигнала формируются импульсы, соответствующие границам (энакопеременам) элементарных посылок. Импульсы, соответствующие положительным знакопеременам (0 двоичной информации переходит в 1 ) снимаются с одного входа, импульсы отрицательных знакоперемен (1 переходит в 0 ) — с другого выхода.

Асинхронный приемник 7 устраняет дробления посылок и работает по дискретному принципу, для чего на один из входов его подается сигнал частоты дискретизации от задающего генератора 4. При этом специальных синхронизирующих импульсов для работы асинхронного приемника 7 не требуется. Импульсы положительных и отрицательных знакоперемен но входном сигнале подаются на входы блока 9 элементов записи. С выхода блока 5 синхронизации через блоки добавления 13 и вычитания 14 поступает на вход распределителя 15 импульсный сигнал с частотой, превышающей в 4 раза тактовую частоту f . Распределитель 15 рассчитан на 4 выхода и одновременно выполняет функцию обычного счетчика, поэтому сигнал с 4-ro выхода распределителя 15 имеет тактовую частоту и управляет работой распредЕлителя 2.

При отсутствии фазовых флуктуаций во входном сигнале импульсная часто55

65 качание входного сигнала продолжается и дальше и превышает +1/2 с,(или

-1/2 со, то происходит еще одно вычитание (или добавление), что приводит к изменению фазы сигнала записи на 1/2 тактового периода.

При ослаблении качания (изменении фазы в сторону нормального положения) происходит обратная подстройка — путем добавления и вычитания импульсов установится первоначальная нормальная та и Фаза сигнала с выхода распределителя 15 совпадает с тактовой частотой fg. При появлении фазовых флуктуаций, особенно коррелированных, входной сигнал смещается по фазе в сторону, тогда как фаза сигнала записи без принятия специальных мер оста- . ется неизменной нследствие высокой инерционности олока 5 синхронизации, Если при этом осуществлять запись информации в блок 1 элементов с неизменной тактовой частотой, то появл. ются ошибки, когда амплитуда качаний совместно с шумовыми флуктуациями фазы границ посылок превышает полонину длительности посылок.

15 Для того, чтобы при записи в блок

1 элементов ошибок не происходило, фаза сигнала записи должна повторять фазовые качания входного сигнала, т.е. в соответствии с фазой входного

;щ сигнала должна изменяться фаза управляющих импульсов выхода распределителя 15.

При отсутствии качаний сигнала на входе регенератора фазовое положение 5,нефлуктуирующих границ посылок соот ветстнует середине тактового периода импульсной последовательности с выхода распределителя 15. Реальные шумовые флуктуации границ посылок обычно невелики и н основном находятся в промежутке от +1/4 0 (где с у- длительность неискаженной элементарной . посылки) .

Качания фазы входного сигнала принодят к тому, что, начиная с некоторого момента времени фаза границы эле-. ментарной посылки приобретает регулярное смещение, которое, превышая значение 1/4 со, начинает совпадать во времени либо с (— 1/4 т ), либо с

4р (+1/4 со ) состояниями распределителя

15. Если таких совпадений насчитывается три подряд, то происходит добавление.или вычитание импульсов на входе распределителя 15

Это, в свою очередь, принодит изменению фазы импульсов (сигнала записи) на +1/4 (или -1/4) периода тактовой частоты fo и обеспечивает слежение эа фазоным качанием входного сигнала, так как после такой подстройки фазы сигнала записи фазоное положение последующих границ элементарных посылок приходится уже опять примерно на середину тактового периода стробирующих импульсов..Если

743211

10 фаза .гнала записи. Вероятность смещения "раницы посылки за пределы

«+1/4т три раза подряд из-за обычных краевых искажений ничтожно мала.

Сигнал на вход каждого из счетчиков 17 и 18 поступает с выхода коммутатора 16, на входы которого подаются импульсы знакоперемен во входном сигнале и потенциалы с выхода распределителя 15.

Импульсы с выходов счетчиков 17 и 18 поступают на входы блоков добавления 13 и вычитания 14.

Перевод процесса записи из одной ячейки блока 1 элементов в другую происходит в момент появления очередного стробирующего импульса (сигнала записи) . В связи с этим первоначальная запись информации в каждую последующую ячейку осуществляется в зависимости от того, что записано в предыдущей ячейке. Если в предыдущей ячейке была записана 1 (или О ), то и в последующую вводится 1 (или, соответственно; О ).

Этот процесс осуществляется в моменты переключения ячеек блока 1 элементов °

Если в течение нового тактового интервала знакоперемена двоичной информации отсутствует, то и состояние ячейки блока 1 элементов.не изменяется. Если знак посылки изменился, автоматически меняется состояние последующей ячейки.

Последовательность считывания и переключения с одной ячейки блока 1 элементов на другую обеспечивается распределителем .3.

Считывание информации в регейераторе отстает от записи на время, равное n/2 т„, где и — число ячеек блока элементов (в нашем случае п = 4) .

Для предотвращения переполнения блока элементов максимальный уход фазы входного сигнала в этом случае допускается равным «+n/2т- . Запаздывание цикла считывания относительно цикла записи на время 2 со осуществляется следующим образом.

Началом цикла записи можно считать . момент появления заднего фронта первого импульса, поступившего на вход распределителя 2. Для обеспечения отставания цикла считывания на 2 ч о он должен начаться в момент появления заднего фронта третьего импульса, который совпадает с задним фронтом импульса на втором выходе распределителя 2. Поэтому сигнал с этого выхода открывает через ключ 12 доступ тактовым импульсам на вход распределителя 3. Ключ 12 закрывается импульсом установка О, который формируется в момент включения аппаратуры.

Этим же импульсом в момент начала

65 работы регенератора осуществляется установка нуля распределителей 2 и 3.

Таким образом, в регенераторе двоичных сигналов происходит уменьшение вероятности ложного приема информации и обеспечение высокой цикловой устойчивости тактовой синхронизации.

Формула изобретения

Регенератор двоичных сигналов, содержащий блок элементов буферной памяти, два объединенных по входу распределителя для записи и считывания информации, задающий генератор, подключенный к входу блока синхронизации, и выходной триггер, о т л и ч а ю шийся тем, что, с целью повышения точности регенерации, введены асинхронный приемник, элемент

ИЛИ, блок элементов записи, блок элементов считывания, блок элементов

ИЛИ, ключ и последовательно соединенные блок добавления, блок вычитания, распределитель и коммутатор один выход коммутатора через первый счетчик подключен ко входу блока добавления, второй выход через второй счетчик подключен к другому входу блока вычитания, а третий выход подключен к другим входам первого и второго счетчиков, причем выходы асинхронного приемника подключены к входам блока элементов записи, а через элемент ИЛИ вЂ” к другому входу коммутатора и другому входу блока синхро. низации, первый выход которого подключен к другому входу блока добавления, а второй выход подключен к входу ключа, выход которого подключен к управляющему входу первого распределителя для записи и считывания информации, разрядные выходы которого подключены к входам блока элементов считывания, выходы которого через блок элементов ИЛИ подключены к входам выходного триггера, при этом четвертый выход коммутатора подключен к управляющему входу второго распределителя для записи и считывания информации, разрядные выходы которого через последовательно соединенные блок элементов записи и блок элементов буферной памяти подключены к другим входам блока элементов считывания, причем выходы блока элементов памяти подключены соответственно к другим входам блока элементов записи, при этом соответствующий раэрядный выход второго распределителя для записи и считывания информации подключен к другому входу ключа, а выход задающего, генератора подключен к другому входу асинхронного приемника, при этом на третий вход ключа

7432 1,1

Составитель Т.Маркина

Техред Л.Теслюк Корректор С.Шекмар

Редактор В. Эарванская

Заказ 3632/20 Тираж 729 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 и др" гие входы первого и второго распределителей для записи и считывания информации подан сигнал установка нуля .

Источники инфоомации, принятые во внимание при экспертизе

1. Патент Японии 9 45-102308, кл. 96/7, 1963 (прототип) .