Устройство для передачи информации

Иллюстрации

Показать всеРеферат

Л;» < F. ÿ,,;. : - - .ь т „ " "(У ;:.: оибла те:. «»:.-,. .-. ев„ ъ4 в»,»

ОП ИЕ

ИЗОБРЕТЕНИЯ

Союз Советскнк

Социалистических

Республик (1) 743220

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Заявлено 060378 (21) 2588029/18-09 с присоединением заявки Йо (23) Приоритет

Опубликовано 2506,80.Бюллетень Но 23

Дата опубликования описания 2506.80 (51)М. Кл.2

Н 04 Ь 17/02Р

Н 04 L 25/16

Государственный комитет

СССР по делам изобретений и открытий (53) УДК621.394 61 (088. 8) (72) Автор изобретения

Р . Т . Сафаров (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ

Изобретение относится к электросвязи и может использоваться в телеметрий.

Известно устройство для передачи информации, содержащее входной преобразователь аналог-цифра, и-выходов которого соединены с входами блока вычитания, к другим входам которого подключены выходы сумматора, к двум управляющим входам которбго и к управляющим входам формирователя выходного сигнала подключены знаковые выходы блока вычитания, причем к синхронизирующим входам входного преобразователя аналог-цифра, блока 15 вычитания, формирователя выходного сигнала и сумматора подключен выход синхронизатора (1).

Однако в известном устройстве наблюдается значительное количество 20 ошибок передачи и избыточность информации.

Цель изобретения — уменьшение ошибок передачи и избыточности передаваемой информации. 25

Для этого в устройство для передачи информации, содержащее входной преобразователь аналог-цифра, и-выходов которого соединены с входами блока вычитания, к другим входам ко- 30

Ф торого подключены выходы сумматора, к двум улравляющим входам которого и к управляющим входам формирователя выходного сигнала подключены знаковые выходы блока вычитания, причем к синхронизирующим входам входного преобразователя аналог-цифра, блока вычитания, формирователя выходного сигнала и сумматора подключен выход синхронизатора, введены блок выделения сигнала старшего разряда и блок. кодирования сигнала старшего разряда, при этом и-информационных выходов блока вычитания подключены к входам блока выделения сигнала старшего разряда, (n-к) выходов которого, где (n-1) к О, подключены к дополнительным входам сумматора и к входам блока кодирования сигнала старшего разряда, выходы которого подключены к информационным входам формирователя выходного сигнала, кроме того, блок выделения сигнала старшего разряда содержит (n-1) ииверторов, (n-1) элементов И и элемент ИЛИ,, при этом выход каждого из инверторов подключен к .одному из входов соответствующего элемента И и к одному из входов всех последующих элементов И, другой вход каждого

743220 из элементов И соединен с входом последующего инвертора, вход каждого иэ инвертбров является одним из входов блока выделения сигнала старшего разряда, выходами которого являются выходы всех элементов И, кроме первых (k-1) элементов И, и выход элемента ИЛИ, к входам которого подключены вход первого инвертора и выходы (К-1) первых элементов И, кроме того, блок кодирования сигнала старшего разряда содержит коммутатор и (n-К) /2 ячеек, состоящих из элемента ИЛИ и двух элементов И, при этом первый вход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом второго элемента И, к второму входу которого и второму входу первого элемента И подключены выходы коммутатора, первый и второй входы каждого из элементов ИЛИ соединены с дополнительными входами элемента ИЛИ последующей ячейки и являются входами блока кодирования сигнала старшего разряда, выходами которого являются выходы элементов И (где п — число выходов, а К вЂ” число разрядов).

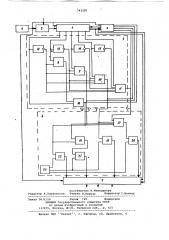

На чертеже приведена структурная электрическая схема предложенного устройства.

Устройство для передачи информации содержит блок 1 вычитания, входной преобразователь 2 аналог-цифра, сумматор 3, синхронизатор 4, блок 5 выделения сигнала старшего разряда, блок б кодирования сигнала старшего разряда, формирователь 7 выходного сигнала, кроме того, блок 5 выделения сигнала, старшего разряда состоит из (п-1) элементов 8, 9, 10 и 11 И, (n-1) инверторов 12, 13, 14 и 15 и элемента 16 ИЛИ, а блок 6 кодирования сигнала старшего разряда состоит из (n-К) /2 ячеек, каждая из которых состоит из элемента 17 ИЛИ (или 18) и двух элементов 19 и 20 И (или 21 и 22) и коммутатора 23.

Устройство работает следующим образом.

Синхронизатор 4 вырабатывает сигналы,.необходимые для обеспечения работы всех основных блокон устройстна. Входной сигнал Л (f.) н преобразователе 2 аналог-цифра представляется в виде периодически следующих и-разрядных двоичных сигналов н параллельной форме, которые подаются в блок 1 вычитания, на вторые входы которого с выхода сумматора 3 поступают в цифровой форме значения оценок 3м (t) входного сигнала W () .

Блок 1 вычитания вычисляет величину и знак разности двух входных величин, представляемых в виде цифровых сигналов.

В блоке 5 выделения сигнала определяется сигнал старшего разряда, не равный нулю. Например, если на вход

60 блока 5 выделения сигнала поступает сигнал 00101011, то íà его третьем выходе будет сигнал, свидетельствующий о том, что третий разряд равен 1.

Этот сигнал подается одновременно в сумматор 3 и блок б кодирования сигнала старшего разряда. На вход сумматора 3 подаются также сигналы знака разности + или -) . Число, соотнетствующее выделенному сигналу старшего разряда, добавляется к ранее записанному в сумматоре 3 числу.

В блоке б кодирования формируется сигнал в виде неравномерного кода.

При этом числа 1,2,4,8,16... представляются соответственно сигналами

1,10, 11,110,111. В формирователе 7 формируется сигнал с учетом знака разности. Так, если на вход блока б кодирования подавались числа -1, -2, -4, -8 и -1б,„-то на выходе формирователя 7 вырабатываются соответственно сигнала 0,01, 00,001 и 000. Сигналы с меняющимся числом разрядов представляются в непрерывной или импульсной форме .

Схема блока 5 выделения сигнала соответствует 5-ти разрядному коду разности д (t< ) и Л (t; ), где Л (ti ) значение входного сигнала н цифроной форме; Л" (t ) — значение оценки в цифровой форме в момент

Блок 5 выделения сигнала старшего разряда работает следующим образом.

Если на его вход подается, например, сигнал 01011, то единичный сигнал появляется только на выходе эле-. мента 16 ИЛИ, так как единичная посылка второго разряда пройдет через элемент 8 И на вход элемента 16 ИЛИ.

Элементы 9-11 И при этом будут заперты, так как с выхода инвертора 13 на их вторые входы не подается положительный потенциал. При поступлении, например, сигнала 00010 единичная посылка четвертого разряда пройдет через элемент 10 И, на первые три входа которой подаются единичные сигналы с выходов инверторов 12, 13 и

14. Элемент 16 ИЛИ включается н том случае, если используется лишь часть дельта-сигналон. Например, если разность Х (,) и 3 (;) представляется

9-ти разрядным кодом, то н общем случае необходимо передавать сигналы, имеющие веса, равные 1,2,4,8,16,32, 64,128 и 256. Если использовать только часть из них, допустим, .сигналы с весами 1, 2, 4, 8 и 16, то при 9-ти входах блок 5 выделения сигнала будет содержать 5 выходов. При этом входы 1,2,3 и 4 старших разрядов (неса 256, 128, 64 и 32) будут подключены к одному выходу через элемент 16 ИЛИ .

Блок б кодиронания старшего разряда имеет число входов, равное числу используемых дельта-сигналов. На схеме входы обозначены весами этих сиг74 3220

55 валов. Коммутатор 23 вырабатывает несколько сдвинутых на величину длительности выходной посылки т последовательностей управляющих импульсов. Первая последовательность подается на вход элемента 20 И,. второй вход которого подключен к выходу элемента 17 ИЛИ, соединенного своими входами са всеми входами блока б кодирования. Вторая последовательность подается на первый вход элемен- 1О та 19 И, второй вход которого соединен со входом блока б кодирования, на который подается сигнал с весом, равным 2, а.также на первый вход элемента 21 И, второй вход которого связан с выходом элемента 18 ИЛИ, входы которого связаны с входами блока б кодирования, на которые подаются сигналы с весами, равными 4 и 8. Третья последовательность подается на первый вход элемента 22 И, второй вход которого связан со входам блока б кодирования, на который поступает сигнал с весом, равным 8.

В блоке б кодирования сигналы на выходах элементов 20 и 21 И обозначим 25 индексами 1, а на выходах элементов

19 и 22 И вЂ” индексами О.

При подаче на вход блока б кодирования сигнала с весом, равным 4 (вход 4 ) формируется сигнал 11 3О следующим образам. С выхода элемента 18 HJIH на один вход элемента 20 И подается входной сигнал с весом, равным 2, с входа 2 блока б кодирования. На другой вход этого элемента поступает первый управляющий (отпирающий) импульс. При этом на выходе получается сигнал 1. Второй отпирающий импульс коммутатора 23 подается на входы элементов 19 и

21 И. Сигнал с весом, равным 2 (co входа 2 ) блока б кодирования проходит через элемент 21 И. Этот выходной сигнал соответствует посылке 1.

В отличие ат известного данное устройство обеспечивает уменьшение ошибки перегрузки, а за счет обнаружения и исправления части ошибок оно дает воэможность уменьшить и величину ошибок накопления. Кодирование с основанием 4 и 2 позволяет сократить длину кодовых комбинаций, т.е. уменьшить количество передаваемых по каналу посылок (импульсов) .

Формула изобретения

1. Устройство для передачи информации, содержащее входной преабразо- Я) в ат ель ан алог-цифра, и-выходов к старого соединены с входами блока вычитания, к другим входам которого подключены выходы сумматора, к двум управляющим входам которого и к 65 управляющим входам формирователя выходного сигнала подключены знаковые выходы блока вычитания, причем к синхронизирующим входам входного преобразователя аналог-цифра, блока вычитания, формирователя выходного сигнала и сумматора подключен выход синхронизатора, о т л и ч а ю щ е е— с я тем, что, с целью уменьшения сиаибок передачи и избыточности передаваемой информации, введены блок выделения сигнала старшего разряда и блок кодирования сигнала старшего разряда, при этом и-информационных выходов блока вычитания подключены к входам блока выделения сигнала старшего разряда, (n-к) выходов ко— торого, где (n-1) К > О, подключены к дополнительным входам сумматора и к входам блока кодирования сигнала старшего разряда, выходы которого подключены к информационным входам формирователя выходного сигнала.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок выделения сигнала старшего разряда содержит (n-1) инверторов, (n-1) элементов И и элемент ИЛИ, при этом выход каждого из инверторов подключен к одному из входов соответствующего элемента И и к одному из входов всех последующих элементов И, другой вход каждого из элементов И соединен с входом последующего инвертора, вход каждого из инверторов является одним из входов блока выделения сигнала старшего разряда, выходами которого являются выходы всех элементов И, кроме первых (к-1) элементов

И и выход элемента. ИЛИ, к входам ко торога подключены вход первого инвертара и выходы (к-1) первых элементов И.

3. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок кодирования сигнала старшего разряда содержит коммутатор и (n-K)/2 ячеек, состоящих из элемента ИЛИ и двух элементов И, при этом первый вход первого элемента И соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом второго элемента И, к второму входу которого и второму входу первого элемента И подключены выходы коммутатора, первый и второй входы каждого иэ элементов ИЛИ соединены с дополнительными входами элемента ИЛИ последующей ячейки и являются входами блока кодирования сигнала старшего разряда, выходами которого являются выходы элементов И (где n — число выходов, а

К вЂ” число разрядов) .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9527834,:,кл . Н 04 L 25/00, 1975 (прототип) .

Составитель A. Меньшикова

Редактор В. 3 арванская Техред Я, Вир ак Корректор С .Шекмар

3акаэ 36 32/20 Тираж 729 Подписное

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4