Устройство кодирования и декодирования видеоинформации

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистических

Республик (1ц743227

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву (22) Даявлено 281177 (21) 2548153/18-09 (51)M. КЛ. с присоединением заявки М

H 04 N 7/16

Государственный комитет

СССР ио делам изобретений н открытий (23) Приоритет

Опубликовано 2506,80 Бюллетень Hо 23

Дата опубликования описания 2596ÂÎ (53) УДК 621. 397 (088. 8) (72) Автор изобретения

Ю.И. Попашенко (7 3 ) 3 а я в итель (54) УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ

ВИДЕОИНФОРМАЦИИ

Изобретение относится к области телевидения.

Известно устройство кодирования и декодировани я видаоин формации, содержащее последовательно включенные входной согласующий усилитель, селектор синхросигнала, блок управления, коммутатор сигнала иэображения и,выходной согласующий усилитель, второй вход которого соединен с вторым выходом селектора синхросигнала, выход которого подключен к входу генератора импульсов тактовой частоты (1) .

Однако известное устройство обла 19 дает недостаточно высокой помехоустойчивостью и степенью маскировки видеоинформации.

Целью изобретения является повышение степени маскировки видеоинфор- 20 мации и помехоустойчивости.

Для этого в устройство кодирования и декодирования видеоинформации, содержащее последовательно включенные входной согласующий усилитель, 2э селектор синхросигнала, блок управления., коммутатор сигнала изображе- . ния и выходной согласующий усилитель, второй вход которого соединен с вторым выходом селектора синхросмтнала 30 выход которого подключен к входу генератора импульсов тактовой частоты, введены пос; едовательно включенные блок выбора кода, генератор последовательности псевдослучайных чисел, второй вход которого соединен с выходом генератора импульсов тактовой частоты, коммутатор адресного сигнала, соединенный, вторым и третьим входами соответственно с выходом генератора импульсов тактовой частоты и с вторым выходом блока управления, первый адресный регистр и первый блок памяти, второй вход которого и выход соединены соответственно с вторым выходом и вторым входом коммутатора сигнала изображения, последовательно включенные второй адресный регистр, соединенный входом с вторым выходом коммутатора адресного сигнала, и второй блок памяти ВтОрОй ВхОд и Выход кОтОрОro соединены соответственно с третьим выходоМ и третьим входом коммутатора сигнала иэображения, аналого цифровой преобразователь, вход и выход которого соединены соответственно с входом селектора синхросигнала и с четвертым входом коммутатора сигнала иэображения, причем

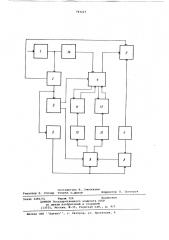

743227 второй выход блока выбора кода соединен с третьим входом выходного согласующего усилителя, Н а чертеже предст авлен а структурная электрическая схема предложенного устройства.

Устройство кодирования и декодирования вицеоинформации содержит последовательно включенные входной согласующий усилитель 1, селектор сийхросигнала 2, блок управления

3, коммутатор 4 сигнала изображения и выходной согласующий усилитель 5, второй вход которого соединен с вторым выходом селектора синхросигнала 2. Выход последнего подключен к входу генератора импульсов тактовой частоты б. Кроме того устройство кодирования содержит блок 7 выбора кода, генератор 8 последовательности псевдослучайных чисел, коммутатор 9 адресного сигнала, пер вый адресный ре ги стр 10 и первый бло к памяти 11, второй адресный регистр 12 и второй блок памяти 13, аналогоцифровой преобразовател - >.4, Второй вход генератора 8 последовательности псевдослучайных чисел соединен с выходом генератора б импульсов тактовой частоты. Второй и третий входы коммутатора адресного сигнала 9 соединены соответственно с выходом генератора б импульсов .тактовой частоты и с вторым выходом блока управления 3, Второй вход и выход первого блока памяти 11 соединены соответственно с вторым выходом и вторым входом коммутатора 4 сигнала иэображения. Вход второго адресного регистра 12 соединен с вторым выходом коммутатора 9 адресного сигнала. Второй вход и выход второго блока памяти ).3 соединены соответственно с третьим выходом и третьим входом коммутатора 4 сигнала изображения. Вход и выход аналогоцифрового преобразователя 14 соедийены соответственно с входам селектора синхросигнала 2 и с четвертым входом коммутатора сигнала изображе,ния 4, Второй выход блока 7 выбора кода соединен с .третьим входом выходного согласующего усилителя 5.

В режиме кодирования устройство работает следующим образом.

Исходный полный видеосигнал через входной согласующий усилитель

1 поступает на вход селектора синхросигнала 2. Выделенный им сиríал синхронизации поступает на блок управления 3 и генератор б импульсов тактовой. частоты. В последнем сигнал синхронизации осуществляет фазирование последовательности импульсов тактовой частоты. Выход входного согласующего усилителя 1 соединен также через аналого-цифровой преобразователь 14 с четвертым входом коммутатора 4 сигнала изображения, осуществляющего последовательное (через кадр) подключение выходного сигнала аналого-цифрового пре, образователя 14 к входам либо первого блока памяти 11, либо второго блока памяти 13. Последовательность переключения задается поступающим на коммутатор 4 сигнала изображения сигналом .блока управления 3. Вхо-ды блоков памяти 11 и 13 соединены соответственно с выходами адресных регистров 10 и 12, на входы которых поступают выходные сигналы с коммутатора 9 адресного сигнала, также управляемого блоком управления 3.

На второй вход коммутатора поступает последовательность импульсов тактовой частоты от генератора 6 импульсов тактовой частоты, на первый последовательность псевдослучайных

Я чисел от генератора 8 последовательности псевдослучайных чисел. Последовательность содержит числа от единицы до N, где N число номинальных элементов раз25 ложения в исходном видеоси гн але .

Порядок следования чисел в последовательности определяется сигналом управления, поступающим на управляющий вход генератора от блока выбора

Зо кода 7. Код последовательности псев- дослучайных чисел поступает на выходной согласующий усилитель 5 для замешивания в зашифрованный видеосигнал а интервалах обратного хода.

На выходной согласующий усилитель 5. подаются также синхросигнал с выхода селектора синхросигнала 2 и зашифрованный видеосигнал с выхода коммутатора 4 сигнала изображения.

Коммутаторы 4 и 9 работают синфазно так, что в том кадре, в котором на первый блок памяти 11 поступает исходный видеосигнал, первый адресный регистр 10 соединяется с генератором 6 импульсов тактовой часто45 ты. В этом же интервале времени второй блок памяти 13 соединяется своим выходом через коммутатор 4 сигнала иэображения с входом выходного согласующего усилителя 5, а на второй адресный регистр 12 (работающий при этом в режиме прямой установки числа, а не в режиме счета) поступает последовательность псевдослучайных чисел. В следующем кадре выход первого блока памяти 11 будет подключен коммутатором к входу выходного согласующего усилителя 5» первый адресный регистр 10 — к выходу генератора 8 последовательности псевдослучайных чисел и поле пабО мяти блока памяти 11, заполненное по закону развертки исходного видеосигнала, будет считываться по псевдослучайному закону. В этом же интервале времени второй блок памя65 ти 13 будет соединен своим входом

743227 тор 8 последовательности псевдослучайных чисел. В режиме декодирования на адресный регистр заполняемого блока памяти должен быть подключен генератор 8 последовательностей псевдослучайных чисел, а к адресному регистру считываемого блока памяти должен быть подключен генератор 6 импульсов тактовой частоты.

Переход от режима кодирования к режиму декодирования осуществляется внутренней коммутацией в блоке уп50 с выходом аналого-цифрового преобразователя 14, а второй адресный регистр 12 — с выходом генератора импульсов тактовой частоты 6. После памяти блока памяти 13 будет заполняться по закону развертки исходного видеосигнала.

Работа устройства в режиме декодирования отличается от описанной тем, что при работе блока памяти в режиме записи на его адресный регистр поступает .через коммутатор 9 адресного сигнала последовательность псевдослучайных чисел. Порядок следованиячисел в последовательности, как и при кодировании, определяется сигналом управления от блока 7 выбора 15 кода. При этом адрес ячейки памяти, в которую записывается мгновенное значение сигнала иэображения, будет соответствовать адресу ячейки памяти кодирующего устройства на пере- . 2(( дающем конце, из которой это мгновенное значение сигнала изображения извлечено при передаче. В результате по истечении интервала прямого хода по кадру после памяти будет 25 заполнено в той последовательности мгновенных значений сигнала изображения, которая соответствует исходному изображению, Для считывания декодированного сигнала с блока памяти его адресный регистр коммутатором 9 адресного сигнала подключается к генератору 6 импульсов тактовой частоты и считывание производится по закону развертки исходного видеоси гн ала.

Из описания режимов кодирования и декодирования очевидно, что различие между ними состоит только во взаимной фазировке коммутаторов 4 и 9. В режиме кодирования к адресному регистру блока памяти 11 или 13 должен быт ь подключен ген ератор 6 импульсов тактовой частоты, а к ад- . ресному регистру считываемого блока памяти должен быт ь подключен ген ера- 45 равления 3. Возможность использования одного и того же устройства и на передающей и на приемной стороне с переключением режима прием-передача дает значительные технические преимущества при эксплуатации àïïàратуры.

Формула изобретения

Устройство кодирования и декодирования видеоинформации, содержащее последовательно включенные входной согласующий усилитель, селектор синхроси гнала, блок управления, коммутатор сигнала изображения и выходной согласующий усилитель, второй вход которого соединен с вторым выходом селе ктора сии хро си гн ал а, выход которого подключен ко входу генератора импульсов тактовой частоты, отличающееся,тем,что, с целью повышения степени маскировки видеоинформации и помэхоустойчивости, введены последовательно включенные блок выбора кода, генератор последовательности псевдослучайных чисел, второй вход которого соединен с выходом генератора импульсов тактовой частоты, коммутатор адресного сигнала, соединенный вторым и третьим входами соответственно с выходом генератора импульсов тактовой частоты и с вторым выходом блока управления, первый адресный регистр и первый блок памяти, второй вход которого и выход соединены: соответственно с вторым выходом и вторым входом коммутатора сигнала иэображения, последовательно включенные второй адресный регистр, соединенный входом с вторым выходом коммутатора адресного сигнала, и второй блок памяти, второй вход и выход которого соединены соответственно с третьим выходом и третьим входом коммутатора сигнала иЗображения, аналого-цифровой преобразователь, вход и выход которого соединены соответственно ,с входом селектора синхросигнала и с четвертым входом коммутатора сигнала иэображения, причем. второй выход блока выбора кода соединен с третьим входом выходного согласующеro усилителя.

Исгочники информации принятые во внимание при экспертизе

1. Пагент Японии Р 51-12483, кл. 97 (5) А15, 1976 (прототип) .

743227

Составитель Н. Сьюлякова

Редактор Е. Гончар Техред О. Дюлай Корректор . р екто Н. Григорук

Закая 3490/51 Тираж 729 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретениЯ и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4