Устройство для числового программного управления станком

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 17.04.78 (21) 2605360/18-24 с присоединением заявки Ж— (23) Приоритет— (5l)M. Кл.

g 05 В 19/18

1Ъсударстеенный комитет

СССР

Опубликовано 30.06.80. Бюллетень .% 24 (53) УДК

62-50 (088.8) по делам изобретений и открытий

Дата опубликования описания 30.06.80

В. А. Яковенко и В. М. Опенкин (72) Авторы изобретения (71) Заявитель. (54) УСТРОЙСТВО ДЛЯ ЧИСЛОВОГО ПРОГРАММНОГО УПРАВЛЕНИЯ

СТАНКОМ

Устройство относится к автоматике и может быть использовано в числовом программном управлении металлорежущим станком.

Известно устройство для числового программного управления станками с последовательным

5 вводом программы в электронные блоки памяти

Устройство имеет две памяти, промежуточная память постоянно связана с читающим устройством, а рабочая память постоянно работает на цепи коммутации выходов делителя перемещения (1j.

t0

Наиболее близким техническим решением к предлагаемому является система числового программного управления Н вЂ” 22 — 1М, предназначенная для программного управления токар15 ными станками. Устройство содержит блок ввода информации, преобразователь, интерполятор, блок управления шаговым приводом (2).

Недостаток устройства заключается в том, что в случае завершения отработки перемещения на частоте, близкой к частоте приемистости шагового двигателя, и прихода команды Hà реверс, происходит сбой шагового двигателя, ошибка отработки программы и брак детали.

Цель изобретения — упрощение устройства и надежная отработка заданной частоты при реверсе шагового двигателя.

Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные блок ввода информации, преобразователь кода, блок буфферной памяти, блок оперативной памяти, интерполятор, блок управления и щитовый привод, введены блок сравнения, первый ключ и последовательно соединенные второй ключ и элемент задержки, выход которого подключен ко входу преобразователя кода и выходу первого ключа, первый вход которого подсоединен к первому выходу блока сравнения, а второй вход —. к выходу интерполятора, первые входы блока сравнения соединены со вторыми выходами блока буферной памяти, а вторые входы — со вторыми выходами блока оперативной памяти, а второй выход —, со вторым входом второго ключа.

Причем блок сравнения содержит элементы

И вЂ” НЕ, ИЛИ, инвертор, элемент И, коммутирующий элемент, счетчик и триггер, первый эле,мои. И вЂ” НЕ выходом соединен с первым вхоО П И С А Н И Е,744465

ИЗОЬРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

7444

10 ков.

40 равен "О"

45 Предложенное устройство обеспечит надежную отработку программы на всех частотах.

3 дом первого элемента И, а выход первого элемента ИЛИ подключен ico второму входу первого элемента И, выход которого йодключей к первому входу второго элемента ИЛИ, соединенного выходом с первым входом второ.

ro элемента И, второй вход которого подсоединен к выходу триггера, соединенного входом через счетчик с выходом коммутирующего элемента, причем второй вход второго элемента

ИЛИ подключен к выходу третьего элемента

И, первый вход которого подсоединен к выходу второго элемента И вЂ” НЕ, а второй вход— к выходу третьего элемента ИЛИ, первые и вторые входы элементов первого И вЂ” НЕ, первого

ИЛИ, второго И вЂ” НЕ, третьего ИЛИ и коммути; рующего элемента подключены к соответствующим первым и вторым входам блока сравнения.

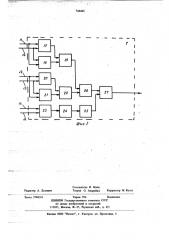

На фиг. 1 представлена структурная схема устройства, на фиг. 2 — схема блока сравнения информации.

Устройство содержит блок 1 ввода информации, преобразователь 2, буферную память 3, рабочую память 4, интерполятор 5, блок б управления шаговым приводом, блок 7 сравнения, ключи 8 и 9, элемент 10 задержки, каналы 11, 12 и 13 передачи информации из блока 3 буферной памяти в блок 7 сравнения, каналы 14, 15 и 16 передачи информации из блока 4 оперативной памяти в блок 7 сравнения.

Устройство работает следующим образом.

Считывание информации с программоносите.ля (на чертеже не показан) блоком 1 ввода информации, преобразование информации в последовательный двоичный код преобразовате"лем 2 и запись ее в буферную память 3 производится одновременно с отработкой информации предыдущего кадра интерполятором 5.

По окончании отработки кадра в интерполяторе 5 формируется сигнал "Конец отработки кадра", по которому преобразователь 2 вырабатывает сигналы переписи. информации из буферной памяти 3 в оперативную память 4 и сигнал считывания очередного кадра.

При наличии в программе реверса движений по одной из координат на шаговый привод поступают импульсы, частота следования которых равна суМме частот импульсов предыдущего и последующего кадров.

При этом возможны сбои шагового привода, если суммарная частота превысит частоту его

-пр иемистости.

Вышеперечисленные состояния (реверс, движений, суммарная частота) определяются блоком 7 сравнения информации, который вырабатывает сигналы управления ключами 8 и 9, В зависимости от состояния. выходных сигналов блока 7 сравнения информации сигнал

"Конец отработки кадра" с интерполятора 5 поступает на преобразователь 2 через ключ 8

65 4 или через ключ 9 с временной задержкой, определяемой элементом 10 задержки.

Величина временной задержки определяется временем, необходимым для останова шагового привода йосле отработки предыдущего кадра.

Блок сравнения информации работает следующим образом.

При поступлении сигналов по каналам 11, 14, несущих информацию знака по адресу Х в соседних кадрах, на элементы 17 И вЂ” НЕ, 18

ИЛИ и 19 И, на выходе последнего устанавливается уровень "1" при разноименных знаках или уровень "О" при одноименных знаках, Аналогично работает схема сравнения знаков соседних кадров по адресу Z, состоящая из элементов 20 И вЂ” НЕ, 21 ИЛИ и 22 И.

Сигналы с выходов элементов 19 и 22 И поступают на элемент 26 ИЛИ, выходной уровень которого равен "1" при наличии "1" на .выходе хотя бы одной из схем сравнения знаПо каналам 13, 16 сигналы в виде последовательного двоичного кода, несущие информацию о частоте отработки в соседних кадрах, через коммутирующий элемент 23 последовательно записываются в счетчик 24, емкость которого пропорциональна частоте приемистости шагового привода.

При превышении суммарной частотой отработки соседних кадров частоты приемистости шагового привода счетчик 24 вырабатывает импульс переполнения, который устанавливает триггер

25 в состояние "1".

Состояния триггера 25 и схем сравнения знаков по адресам Х и Z анализируются элементом 27 И, на выходе которого устанавливается уровень "1" при совпадении признаков;.зменения знака по адресам Х или Z в соседних кадрах и превышения суммарной частотой отработки соседних кадров частоты приемистости шагового привода.

При отсутствии одного из перечисленных признаков выходной уровень элемента 27 И

Формула изобретения

1. Устройство для числового программного управления станком, содержащее последовательно соединенные блок ввода информации, преобразователь кода, блок буферной памяти, блок оперативной памяти, интерполятор, блок управления и шаговый привод, причем второй выход преобразователя кода подключен ко вторым входам блоков ввода информации, буферной и оперативной памяти, о т л и ч а ю m е е с я

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР К 257265, кл. Q 05 В 19/02, 1969.

2. Сергиевский Л. В. Электронные устройства систем ЧПУ. М., "Машиностроение", 1977, с. 17 — 21 (прототип), 5 7444 тем, что, с целью упрощения устройства, в него введены блок сравнения, первый ключ и последовательно соединенные второй ключ и элемент задержки, выход которого подключен ко входу преобразователя кода и выходу первого ключа, первый вход которого подсоединен к первому выходу блока сравнения, а второй вход — к выходу интерполятора, первые входы блока сравнения соединены с вторыми выходами блока буферной памяти, вторые входы — с вторыми 1p выходами блока оперативной памяти, а второй выход — со вторым входом второго ключа.

2. Устройство по п. 1., о т л и ч а ю щ е ее я тем, что блок сравнения содержит элементы

И вЂ” НЕ, ИЛИ, инвертор, элемент И, коммутирую- 1з ший элемент, счетчик и триггер, первый элемент

И вЂ” НЕ выходом соединен с первым входом nepsor о элемента И, а выход первого элемента

ИЛИ подключен ко второму входу первого элемента И, выход которого подключен к пер- эп вому входу второго элемента ИЛИ, соединен65 6 ного выходом с первым входом второго элемента И, второй вход которого подсоединен к выходу триггера, соединенного входом через счетчик с выходом коммутирующего элемента, причем второй вход второго элемента ИЛИ подключен к выходу третьего элемента И, первый вход которого подсоединен к выходу второго элемента И вЂ” НЕ, а второй вход — к выходу третьего элемента ИЛИ, первые и вторые. входы элементов первого И вЂ” НЕ, первого ИЛИ, второго

И вЂ” НЕ, третьего ИЛИ и коммутирующего элемента подключены к соответствующим первым и вторым входам блока сравнения.

744465 (6 ь

Составитель И. Швец

Техред О. Андрейко Корректор М. Коста

Редактор А. Долинич

Заказ 3788/10

Филиал ППП "Патент", 1. Ужгород, ул. Проектная, 4

Тираж 956 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5