Преобразователь двоичного кода в двоично-десятичный код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Республик

<« 744546

К АВТОРСКОМУ СВИ ИТЕЛЬСТВУ (о 1) Дополнительное K авт. свид-ву (22) Заявлено 130177 (21) 2453773/18-24 (51)М. Кл.2

G 06 Г 5/02 с присоединением заявки ¹

/ (23) Приоритет

Опубликовано 3006.8О. Бюллетень № 24

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681,325 (088. 8) Дата опубликования описания 3006.80 (72) Авторы изобретения

В. И.Гупалов, Б.(и, Павлов и Б.П.Подборонов

I г, (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД

30

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для преобразования инФормации при вводе и выводе из ЭЦВ(я.

Известен преобразователь двоичного кода в двоично-десятичный код, содержащий каскады регистров, управляющие триггеры и вентили. Сущность работы этого преобразователя состоит в том, что исходный код поступает последовательно, начиная со старших разрядов. Содержимое в отдельных тетрарадах сдвигается влево или вправо в зависимости от наличия или отсутствия переноса из ближайшей тетрады. Направ- ление сдвига тетрады единиц зависит от значения очередного двоичного разряда (1).

Недостатком преобразователя является невысокое быстродействие, которое может быть оценено неравенством ÂP 25 где „р — время преобразования;

n — разрядность преобразуемого кода;

T — период следования такто- вых импульсов, Наиболее близким по технической сущности к предложенному является преобразователь двоичного кода в двоично-десятичный код, содержащий дешифратор, двоично-десятичный накапливающий сумматор, входы которого соединены с выходами дешифратора, блок управления, выходы которого соединены с управляющим входом двоично-десятичного йакапливаюшего сумматора и входом дешифратфра (2).

Кроме того, известное устройство ,содержит коммутатор и элементы ИЛИ.

Сущность работы известного преобразователя состоит в том, что последовательный двоичный код поступает на дешифратор, на выходе которого вырабатывается двоично-десятичный эквивалент двоичного кода. Далее двоично-десятичный эквивалент разряда подекадно суммируется с содержимым двоично-десятичного сумматора.

Недостатком такого преобразователя является низкое быстродействие .

Цель изобретения — повышение быстродействия.

Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный код, содержащий

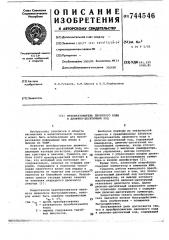

744546 дешифратор, двоична-десятичный накапливающий сумматор входы KoTopoI Î соединены с выходамн дешифратора, блок управления, выходы которого соединены с управляющим входом двоична-десятичного накапливающего сумматора и входом дешифратора, введен и-разрядный сдвигающий регистр, выходы которого соединены со входами дешифратора, а управляющие входы соединены с выходами сброса и сдвига блока управления, причем выход младшего 1О разряда и-разрядного сдвигаюшего регистра соединен со входом младшего разряда двоична-десятичного накапливающего сумматора, выходы которого являются выходами устройства. . II5

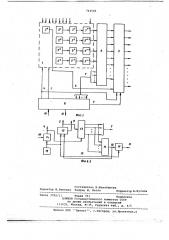

На фиг. 1 представлена схема преобразователя; на фиг. 2 — структурная схема блока управления.

Преобразователь содержит и-разрядный сдвигающий регистр 1, дешифратор

2, двоична-десятичный накапливающий .сумматор 3, выходы 4 и 5 сброса и сдвига (соответственно), вход б младшего разряда двоична -десятичного накапливающего сумматора, управляющие входы 7,.блок 8 управления, шину 9 суммирования, шины 10 и 11 начала и конца преобразования (соответственно).

Структурная схема блока управления {фиг. 2) состоит из схемы 12 формирования тактовых импульсов, двоичного счетчика 13 на m состояний (m — число необходимых для преобразования сдвигов), схемы 14 син" хронизации запуска преобразователя, схемы 15 совпадения, шины 16 разрешения сдвига, схемы 17 Формирования . Конец преобразования, шийы 18 тактовых импульсов, гечератора 19 тактовых импульсов. 40

ПреобразоватеЛь работает следующим образом.

По сигналу Чачало преобразования (шина 10) схема 14 синхронизации запуска преобразователя вырабатывает на шине 4 сброса импульс, который осушествляет установку в 0 сумматора 3, запись преобразуемогокода в регистр 1, сброс счетчика 13 и установку на входах 7 нулевого кода. В соответствии с содержимым старшей тетрады регистра 1 и кодом на входах 7 дешифратор 2 формирует двоична-десятичный эквивалент преобразуемой тетрады. Далее на шине 9 схема 12 формирования тактовых им- 55. пульсов формирует импульс суммирования, который осуществляет занесение двоична-десятичного эквивалента в сумматор 3. Затем на выходе 5 вырабатывается импульс сдвига, который обеспечивает сдвиг содержимого регистра 1 на четыре разряда влево, причем содержимое счетчика 13 и соответственно код на входах 7 унеличивается на единицу. Далее формируется двоична-десятичный эквивалент очередной тетрады и описанный процесс повторяется. Содержимое младшего разряда регистра 1 подается на сумматор 3 н стирается первым импульсом сдвига.

Преобразование заканчивается, когда на входах 7 формируется код, равный m. С появлением этого кода схема 15 совйадения формиоует на шине 16 сигнал, запрещающий даль-, нейшие сдвиги в регистре 1. Подача тактовых импульсов сдвига и тактовых импульсов суммирования прекращается, Схема 17 формирует на шине 11 сигнал Конец преобразования .

Таким образом, предлагаемое устройство обладает более высоким быстродействием. Для преобразования

16-тиразрядного двоичного када предложенным устройством необходимо

4 х 2 = 8 тактов (сдвнг и суммирование на каждую тетраду преобразуемого када), в то время, как в известном устройстве необходимо затратить как минимум 45 тактов, так как сложение двоична-десятичных эквивалентов происходит подекадно для каждого разряда двоичного кода.

Формула изобретения .Преобразователь двоиччого.кода в двоична-десятичный код, содержащий дешифратор, дноично-десятичный накап-линающий сумматор, входы которого соединены с выходами дешифратора, блок управления, выходы которого соединены с управляющим входом двоична-десятичного накапливающего сумматора и входом дешифратора, о т л ич а ю шийся тем, что, с целью повышения быстродействия, он содержит и-разрядный сдвйгающий регистр, выходы которого соедичены со входами дешифратора, а управляющие входы соединены с выходами сброса и сдвига блока управления, причем выход младшего разряда п-разрядного сдвигающего регистра соединен со входом младшего разряда двоична-десятичного накапливаюшего сумматора, выходы которого янляюся выходами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 291196, кл. G 06 F 5/О?, 1969, 2. Авторское свидетельство СССР

9 503234, кл. G 06 F 5/02, 1974 (прототип).

744546

Составитель Н.шелобанова

Редактор И,Нанкина Техред М. Петко корректор В.Бутяга

Заказ 3792/11 Тираж 75 1 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул.Проектная,4