Устройство для деления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Соаетскик

Социалистических

Республик (61) Дополнительное к авт. саид-ву (22) Заявлено 170378 (21) 2591680/18-24 (51) м. к.2. G 06 F 7/39 с присоединенИем заявки Йо

Государственный комитет

СССР но делам изобретений и открытий (23) Приоритет

Опубликовано 3006.8Q Бюллетень Но 24

Дата опубликования описания 3006,80 (53) УДК681. 325. 5 (088. 8) (72) Авторы изобретения

A.Ï.Ñòàõoâ и В.A Ëóæåöíèé

Винницкий политехнический институт. (71) Заявитель (5 4) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ регистра делимого, регистра частного и сумматора соединены с соответствую- щими выходами блока управления, выход регистра частного является выходом устройства, первый вход регистра делимого является первым входом устройства, вход регистра делителя является вторым входом устройства, выход регистра делителя соединен со входом преобразователя прямого кода

s обратный (31.

Недостатком этого устройства для деления является невозможность деления чисел, представленных в р-кодах

Фибоначчи.

Цель изобретения — расширения функционалЬных возможностей устройства.

Данная цель достигается тем, что устройство для деления дополнительно содержит генератор последовательности обобщенных чисел Фибоначчи и регистр остатка, выход которого соединен са вторым входом регистра делимого, а вход соединен со вторым выходом сумматора, второй вход сумматора соединен с выходом генератора последовательности обобщенных чисел Фибоначчи, вход которого соединен с выходом преобразователя прямоИзобретение относится к вычислительной технике и предназнано для деления многоразрядных чисел в р-кодах Фибон аччи .

Известно устройство для деления, содержащее регистр делимого, регистр делителя, схему сравнения, генератор тактовых импульсов, сумматор, и осуществляющее деление многоразрядных двоичных чисел (1) .

Известно также устройство для деления двоичных чисел, содержащее регистр делимого, регистр делителя, регистр частного и параллельный сумматор (2) . 15

Недостатком таких устройств для деления является невозможность деления чисел представленных в р-кодах

Фибоначчи.

Наиболее близким к предлагаемому 20 является устройство для деления, содержащее регистр делителя, преобразователь прямого кода в обратный, регистр делимого и регистр частного, сумматор, первый выход которого соединен со входом блока управления, первый вход сумматора соединен с выходом регистра делимого, управляю щие входы регистра делителя, преобразователя прямого кода в обратный, 30

744564

Разряд,Р ря0

0

15) 12-10= 2(5 0

40 ) 37-25 = 12

О.

65

105 102-65 = 37

55

60 го кода в обратный, управляющие входы генератора последовательности обобщенных чисел Фибоначчи и регистра остатка соединены с соответствующими выходами блока управления.

При делении чисел в р-кодах Фибоначчи образуют последовательность обобщенных чисел Фибоначчи. Начальное число последовательности с номером нуль соответствует йулевому разряду р-кода Фибоначчи частного и является делителем, а 1-е число последовательности, соответствующее 1-му

Разряду р-кода Фибоначчи частного, образуется путем сложения в р- коде

Фибоначчи (1-1) -го и (i-p-1) -го чи сел последовательности обобщенных 15 чисел Фибоначчи. Числа последовательно сравнивают в р-кодах Фибойаччи с делимым до тех пор, пока не определится 8 -ое число, которое является первым" числом в полученной последо- Щ вательности большим делимого. После этого в (Р -1)-й разряд р-кода Фибоначчи частного записывают единицу, а (3 -1) -ое число последовательности обобщенных чисел Фибоначчи вычйтают в р-коде Фибоначчи из делимого. Полученный остаток сравнивают в р-коде

ФИбоначчи с числами полученной последовательности и выделяют m-oe число последовательности, которое являет = ся наименьшим числом последовательности, большим чем остаток. После чего в (m-1) -й разряд р-кода ФибонаЧчи частного записывают единицу, а (m-1) -ое число образованной последовательности вычитают в р-коде Фибоначчи из предыдущего остатка, получая при этом очередной остаток. Процесс сравнения чисел последовательности с остатком и -вычйтание повто ряют до тех пор, пока остаток не ста- 40 нет меньше делителя. При этом контролируют, чтобы в р-коде Фибоначчи частного в каждой группе из (р+1) подряд идущих разрядов кода встречалось не более одной единицы. НарУшение этого условия является признаком неправильного выполнения операции деления.

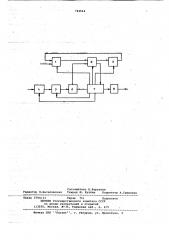

На чертеже изображена блок-схема устройства для деления.

Устройство для деления содержит регистр 1 делимого, предназначенный для хранения р-кода Фибоначчи дели-. мого; сумматор 2, осуществляющийсложение р-кодов Фибоначчи поступающих на его входы; регистр 3 остатка, в котором хранится р-код Фибоначчи разности делимого (остатка) и числа из последовательности обобщенных чисел Фибойаччиу регистр 4 делителя, предназначенный для хранения р-кода

Фибоначчи"делителя; hpеобраэователь

5 прямого кода в обратный, осуществляющий преобразование прямого р-кода

Фибоначчи делителя в обратный р-код

Фибоначчи, который является исходным кодом последовательности кодов формируемой генератором 6 последовательности обобщенных чисел Фибоначчи, блок 7 управления; регистр 8 частно-. го, в которой формируется результат деления в р«коде Фибоначчи. Первый выход сумматора 2, являющийся выходом переноса старшего разряда, соединен со входом блока 7 управления.

Первый вход регистра 1 делимого является первым входом сумматора, а вход регистра 4 делителя является вторым входом устройства. Выход регистра 8 частного является выходом устройства. устройство для деления работает следующим образом.

Если делимое равно 102, делитель

5, то в исходном состоянии в регистре 1 делимого записывается р-код

Фибоначчи числа 102, в регистре 4 делителя — р- код Фибоначчи числа 5; содержимое регистра остатка 3 и регистра частного 8 равно нулю. НулеВое число последовательности обобщенных чисел Фибоначчи, формируемое генератором б, равно обратному р-коду ,Фибоначчи делителя.

Под действием управляющих сигналоз, поступающих иэ блока 7 управления, генератор б начинает формировать обратные р-. коды Фибоначчи чисел последовательности, приведенной в таблице.

Код с выхода генератора 6 поступает на второй вход сумматора 2, который осуществляет сложение этого кода с кодом делимого. При этом на вход переноса младшего разряда сумматора 2 постоянно подается единица, т.е. сложение выполняется как бы с дополнительным кодом. Если на выходе переноса старшего разряда сумматора

2 отсутствует сигнал переноса, то это означает, что код, поступающий из регистра 1, меньше кода, поступающего с выхода генератора 6. Если же на выходе переноса старшего разряда сумматора 2 формируется единичный сигнал, то это значит, что код, по744564 ступающий из регистра 1, больше кода поступающего с выхода генератора б.

Каждый код, формируемый на выходе сумматора 2 и являющийся положительной разностью входных кодов, записывается в регистр 3 остатка.

При сложении прямого кода делимого и обратного кода седьмого числа последовательности будет отсутствовать единичный сигнал на выходе переноса старшего разряда сумматора 2.

Это свидетельствует о том, что 10 данное число последовательности превышает делимое. При этом в шестой разряд регистра 8 частного записывается единица (см.таблицу) .

Отсутствие на входе блока 7 управ- Я ления единичного сигнала, поступающего с выхода переноса старшего разряда сумматора 2,приводит к следующему.

Блок 7 управления формирует управляющий сигнал, под действием которого 2О код положительной разности между делимым и предыдущим (шестым) числом последовательнбсти, полученный на предыдущем такте работы и хранимый в регистре 3, переписывается в регистр 1. Блок 7 управления, кроме того, вырабатывает управляющие сиrналы, обеспечивающие формирование с самого начала последовательности чисел генератором 6. При этом нулевым числом является обратный код делителя. Сумматор 2 вновь формирует код разности, который записывается в регистр 3 но теперь это разность между первым остатком и очередным числом последовательности. При сло- З5 женин обратного кода пятого числа последовательности и прямого кода первого остатка на выходе переноса старшего разряда сумматора 2 формируется нулевой сигнал, свидетельст- 40 вующий о том, что число последовательности больше остатка. Реакция блока 7 управления на этот сигнал такая же, как и в предыдущем случае.

Код второго остатка переписывается g$ из регистра 3 в регистр 1. Генератор б начинает формировать последовательность чисел с самого начала. Кроме ° того в четвертый разряд регистра 8 частного записывается единица. Код gg третьего числа последовательности оказывается больше кода второго остатка, следовательно во второй разряд регистра 8 частного записывается единица. Код третьего остатка переписывается иэ регистра 3 в регистр 1.

Генератор 6 вновь начинает формировать последовательность чисел. При сложении кодов нулевого числа последовательности, являющегося делителем, и третьего остатка оказывается, что остаток меньше делителя, а это является признаком окончания деления.

При этом с выхода переноса старшего

) разряда сумматора 2 поступает нуле вой сигнал на вход блока 7 управлени я, который прекращает формирование управляющих сигналов.

Таким образом, признаком окончания операции деления является наличие нулевого сигнала на входе блока

7 управления после выработки им управляющего сигнала, обеспечивающего сложение сумматором 2 кода, поступающего иэ регистра 1, и кода нулевого числа последовательности.

Введение дополнительных узлов и связей позволяет расширить функЦиональные воэможности устройств для деления а именно позволяет выполнять деление чисел„ представленных р- кодами Фибоначчи, которые обладают способностью обнаруживать искажения двоичных комбинаций.

Формула из обрет ени я устройство для делениями содержащее регистр делителя, преобразователь прямого кода в обратный, регистр делимого, ре гистр частного, сумматор, первый выход которого соединек(со входом блока управления, первый вход сумматора соединен с выходом ре-, гистра делимого, управляющие входы регистра делителя, преобразователя прямого кода в обратный, регистра делимого, регистра частного и сумма- тора соединены с соответствующйми выходами блока управления, выход регистра частного является выходом устройства, первый вход регистра делимого является первым входом устройства, вход регистра делителя является вторым входом устройства, выход регистра делителя соединен со входом преобразователя прямого кода в обратный, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения операции деления чисел в р-кодах Фибоначчи, устройство дополнительно содержФт генератор последовательности обобщенных чисел Фибоначчи и регистр остатка, выход которого соединен со вторым входом регистра делимого, а вход соединен со вторым выходом сумматора, второй вход сумматора соединен с выходом генератора последовательности обобщенных чисел

Фибоначчи, вход которого соединен с выходом преобразователя прямого кода в обратный, управляющие входы генератора последовательности обобщенных чисел Фибоначчи и регистра остатка соединены с соответствующими выходами блока- управления °

Источники информации, принятые во внимание при экспертизе

1. Авторское свидет ель ст во СССР

9396689, кл. G 06 F 7/39, 1973.

2. Авторское свидетельство СССР

9330451, кл. G 06 F 7/39, 1973..

3. Карцев N.A. Арифметика цифровых машин. М., Наука, 1969, с. 494 (прототип).744564

Составитель В.Березкин

Редактор Л.Веселовская Техред М. Кузьма Корректор A. Гриценко

Заказ 3794/13 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Ф

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4