Параллельный двоичный сумматор

Иллюстрации

Показать всеРеферат

ЬП ИСАНИЕ

ИЗЬБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДИТЕЛЬСТВУ

„„74456?

Союз, Советскик

Социалистическик

Республик (61) Дополнительное к авт. свил-ву . (22) Заявлено04.04.78 (21) 2599304/18-24 (53)NL. Кл.

G 06 Р 7/50 с присоединением заявки М

Гооуаарствооиый комитет

СССР ао делан, изооретеиий и открытий (23 ) П риори тет

Опубликовано 30.06.80- Бюллетень М 24 а (53) УДК 681. .325а5 (088.8) Дата опубликования описания 03.07.80

А. Б. Берлин, В. В. Макаренко, В. С. Ношенко, А. И. Офин, И. В. Разин и А. Н. Яблонский (72) Авторы изобретения (71) Заявитель

{S4) ПАРАЛЛЕЛЬНЫЙ ДВОИЧНЫЙ СУММАТОР

Изобретение относится к вычислительной технике и может использоваться при построении вычислительных устройств в телевизионных автоматических анализаторах изображений, осуществляющих, например обнаружение и измерение размеS ров дефектов проката по изображениям шлифов металлов. а

Известен параллельный двоичный сум1О матер, содержащий последовательно включенные сумматоры аналогового тица, выходные сигналы которых через шлейфы, содержащИе последовательно включенные линию задержки и усилитель с коэффици.ентом усиления меньшим единицы, поданы на входы собственных сумматоров jl).

Однако в этом устройстве последовательное включение сумматоров не позвоФтяет получить какого-либо выигрыша йо сравнению с одним сумматором. Недостаткам данного устройства, содержащего как один сумматор, так и несколько, вклю2 ченных последовательно, является ниЛГйтт точность суммирования сигналов.

Наиболее близким по технической сущности к данцому является полный одноразрядный комбинационный, сумматор, выход "сумма которого через устройство задержки на ф тактов соединен с одним иэ его входов, а выход. "перенос через устройство задержки на один такт соединен с другим его входом, а на третий вход одноразрядного комбинационного сумматора подан входной сигнал 2 .

Данное устройство не позволяет проводить селективное суммирование выдеосигнала от нескольких источников, следующих в общем сигнале, полученном, например путем построчного сканирования поля изображения, поэтому его применение для измерения объема каждого дефекта отдельно не эффективно иэза необходимости предварительной селекции от каждой трещины, что приводит к снижению скорости измерения дефектов на иэображениях шлифов металлов.

567 4

10 д5 одноразрядных сумматоров образуется

1 тот же код, что и на входе устройства

3 744

Цель изобретения — расширение области применения параллельного двоичного сумматора за счет независимого суммирования двоичных сигналов от разных источников.

Поставленная цель достигается тем, что в параллельном двоичном сумматоре, содержащем одноразрядные комбинацион ные сумматоры, выход переноса каждого из которых, кроме первого, соединен с одним из входов последующего одноразрядного комбинационного сумматора, а выход суммы — с выходом сумматора, элементы И и элементы задержки, выход суммы каждого одноразрядного комбинациойного сумматора подключен к одному из входов соответствующего элемента И, выход которого через элемент задержки

"соединен с друтим" вхбдом данного одно«. разрядного комбинационного сумматора, другие входы элементов И соединены с входом начальной установки сумматора.

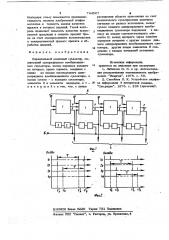

На фиг. 1 изображена структурная схема устройства.;.на фиг. 2 — диаграмма работы устройства.

Параллельный двоичный сумматор содержит одноразрядные комбинационные сумматоры 1, выходы "сумма 5 которых через элементы И 2 и элементы задержки 3 соединены с входами данных одноразрядных комбинационных сумматоров и выходом 4 параллельного двоичного сум-, матора. Другие входы одноразрядных комбинационных сумматоров соединены с входом 5 параллельного двоичного сум матора, а другие входы элементов И соединены с входом 6 начальной установки сумматора. Элементы задержки 3 выполнены в виде регистра сдвига. Время задержки регистра сдвигa ìoæíî менять щ тем изменения числа его действующих разрядов илй изменением частоты синхронизирующих импульсов. Величина заt держки регистра сдвига выбирается равной интервалу времени Т между поступлениями информации, которая:селективно суммируется в отдельной последовательности. Кодовые комбинации в каждой последовательности приходят с интервалом Т или кратному ему (2T, 3T ...). . Кодовые последовательности разделяются между собой во времени. Минимальный интервал времени 1 между кодовыми комбинациями различных последовательностей равен =1/ > где Р— частота " "6йнйрЪнизирующи импульсов регистра сдвига. Максймально возможное число кодовых последовательностей, которые

50 устройство может суммировать раздельно, составляет N-Т/t .

Предложенный сумматор работает следующим образом.

До момента времени (фиг.2) происходит начальная установка сумматора.

В момент времени t на вход 5 сумматора поступает, например параллельный . двоичный код числа три (фиг.2) от источника сигнала А, что соответствует логической единице на третьих входах первого и второго одноразрядных сумматоров и нулю на этом же входе других сумматоров. При этом на выходах "сумма в этот же момент времени. Одновременно с этим с выходов "сумма" каждого одноразрядного сумматора сигнал логической "1" или "О" через свой элемент

И 2 (фиг. 1) подается на вход. регистра сдвига.

Ф

В момент t> (фиг.2) на вход сумматора приходит сигнал от источника сигнала В в виде параллельного двоичного кода числа 12, при этом на выходе "сум-, ма" одноразрядных сумматоров формируется тот же код числа 12. В момент времени t+ равно через время, равное

2. периоду следования кодов от источника сигнала А, на вход устройства поступает очередная кодовая комбинация (параллельный двоичный код числа 1) и одновременно на другие входы одноразрядных

l сумматоров приходит сигнал с собственного регистра сдвига, т.е. поступает кодовая комбийация,, сформированная на выходах "сумма одноразрядных суммато1 ров в момент времени tä . При этом на выходе "перенос" (Р ) первого одноразрядного сумматора образуется сигнал логической "1", а на ;выходе

"сумма" одноразрядных сумматоров сформируется двоичный код числа 4. Так в момент времени на выходах "сумма" одноразрядных сумматоров образуется код, равный сумме кодов, поступивших на вход устройства в моменты времени ð, и 4p . В момент времени„ ф 4 2. устройство работает уочно так же, как и в момент времени 1, при этом на выходах "сумма одноразрядных сумматоров образуется код 13, т.е. суммарный код сигналов, поступивших от источника В в . момент времени 1@ и 6 .

Предложенный сумматор по сравнению с известным позволяет повысить точность сложения амплитуд электрических сйгналов от каждого дефекта в отдельности, 5 744567 6 благодаря этому повышается производи- расширения области применения эа счет тельность анализа изображений шлифов независимого суммирования двоичных металлов и точность оценки качества сигналов от разных источников, выход проката и готовых изделий. Такой конт- суммы каждого одноразрядного комбироль позволяет повысить качество выпус- 5 национного сумматора подключен к одкаемой продукции и снизить процент бра- ному из входов соответствующего элека за счет своевременного вмешательства мента И, выход которого через элемент в технологический процесс проката н об- задержки соединен с другим входом данработки иэделий. ного одноразрядного комбинационного сумfQ матора, другие входы элементов И соеФ о р м у л а и э,о б р е т е н и z динены с входом начальной установки сумматора.

Фиг.1.

ВмОд44

8ходы

tp

2р

1р

Ер

Зр фр

Jp фр

А 6

ЫНИИПИ Заказ 5220 Тираж 751 Подписное

Филиал ППП Патент, г. Ужгород, ул, Проектная,4

Параллельный двоичный сумматор, содержаший одноразрядные комбинационные сумматоры, выход переноса каждого из которых, кроме первого, соединен с одним иэ входов последующего одноразрядного комбинационного сумматора, а выход суммы — с выходом сумматора, элементы И и элементы задержки, о т —. л и ч а и ш и Й с я тем, что, с целью

) Источники ин юрмации, принятые во внимание при экспертизе

1. Либенсон М. Н. и др. Автоматизация распознавания телевизионных изображений. Энергия, 1975, с. 50.

2. Самойлов Л. К. Устройства эадерж20 хи информации в дискретной технике.

"Сов.радио, 1973, с. 239 (прототип}.