Умножитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ " 744569

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву (22) Заявлено 16.03.77 (21) 2462447/18 24 (5l ) М. Кл.

G 06 F 7/52

Н 03 В 19/00 с присоединением заявки Ж

Государстееииык комитет

СССР (23) Приоритет (53) УДК 681.327 (088.8), ив делам изобретеиий и открытий

Опубликовано 30.06.80. Бюллетень М 24

Дата опубликования описания 30.06.80 (72) Авторы изобретения

В. П. Галас, Б. А. Староверов и А. Н. Ширяев (71) Заявитель

Ивановский энергетический институт им. В. И. Ленина (54) УМНОЖИТЕЛЬ ЧАСТОТЫ

Изобретение относится к автоматике и вы числительной технике и может быть использовано в устройствах, требующих повышения частоты электрических сигналов.

Известно устройство для умножения частот, содержащее триггеры, элементы И, генератор управляемой частоты, делитель частоты, и-разрядные суммирующие и выппающие счетчики, осуществляющие преобразование входной частоты умножителя в цифровой код (1).

Однако преобразование частоты в цифровой код сопровождается погрешностью, пропорциональной величине дискретности сигнала, заполняющего и-разрядные вычитающие счетчики.

Поэтому, обеспечивая дальнейшее расширение частотного диапазона и повышенное быстродействие, такой умножитель отличается йедостаточной точностью умножения, а также сложностьЮ технической реализации, Наиболее близким техническим решением к предлагаемому изобретению является умножитель частоты, содержащий управляемый генера тор, делитель частоты, выход которого соединен с первым вхощм первого элемента И и, через элемент задержкй, с первым входом первого триггера, первый выход которого под;ключен ко второму входу первого и первому входу второго элементов И, второй выход первого триггера подключен к первым входам

5 третьего и четвертого элементов И, второй вход первого триггера через второй элемент задержки соединен со входом устройства и вторым входом третьего элемента И, выходы первого и третьего элементов И подключены, со10 ответственно, к первому и второму входам второго триггера, выходы которого подключены, соответственно, ко вторым входам второго и четвертого элементов И, выход которого

15 подключен к первому входу интегратора, выход которого подключен ко входу управляемого генератора, выход которого соединен с выходом умножителя и входом делителя частоты (2).

Недостатком умножителя является низкая точность и ограниченный диапазон коэффициен-, тов умножения.

Цель изобретения — повышение точности и расширение диапазона умножения.

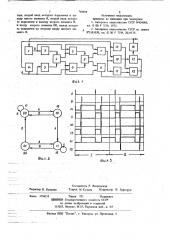

569 4 прета, поэтому импульс А входной;астоты не

1 пропускается на вход триггера 9. Этот импульс через промежуток времени t, сформированный элементом 5 задержки, переключает триггер 4 в единичное состояние, На направленном графе это соответствует переходу из состояния 17 в состояние 18, В этом состоянии с выхода триггера 4 подается сигнал запрета на элемент 2 И, поэтому импульс Б частоты обратной связи не проходит через элемент 2 И на вход триг!

О гера 9, Однако, через промежуток времени t, сформированный элементом задержки 3, он изменяет состояние триггера 4 (переход.из состояния 18 в 17 на направленном графе), подготавливая запрет импульсу А на прохождение через элемент б И. Таким образом, чередованйе входных А и обратной связи Б импульсов приводит к переключению триггера 4, состояние триггера 9 при этом не меняется. Приход подряд двух импульсов (например входных) 15

20 приводит к такому состоянию, когда s момент появления входного импульса А на одном из входов элемента 6 И, на другом присутствует разрешающий потенциал. В этом случае триггер

9 переключается в единичное состояние. Это соответствует переходу из состояния 18 в 19.

Величина широтно-импульсного сигнала с выхода триггера 4, когда он переходит иэ состояния 17 в состояние 18 и обратно, а также из состояния 19 в состояние 20 и обратно, 25

30 пропорциональна фазовому рассогласованию частот А и Б, Триггер 9 переключается с приходом подряд двух одноименных импульсов, т. е. с изменением знака фазового рассогласования. Таким образом, триггер 4 определяет величину, а триггер 9 выявляет знак фазового рассогласования.

В установившемся режиме широтно-импульсный сигнал с выхода триггера 4 подается с помощью элемента 7 И на вход элемента 10 И, 35

40 где суммируется с постоянным по длительности сигналом одновибратора 14, который запускается каждым импульсом А входной частоты, Кроме того, инвертированные широтно-импульсный и одновибратора сигналы суммируются элементом 12 И. Суммарные сигналы с выхода элементов 10 И и 12 И подаются на прямой и инверсный входы интегратора 15 соответственно, Сложение этих сигналов поясняется вре45 менной диа.раммой (фиг. 3), где цифрами

50 обозначены сигналы с выходов соответствующих элементов блок-схемы, показанной на фиг. 1.

На первом участке диаграммы длительность широтно-импульсного сигнала 7 несколько больше pJIHTQJlsHocTH импульсов одновибратора 14 и на прямой вход интегратора 15 подаются узкие импульсы 10. При суммировании инвертированных широтно-импульсного 11 и одновибратора 13 сигналов на инверсный вход интег.

3 744

Цель изобретения достигается тем; что умножитель содержит первый и второй элементы

НЕ, пятый и шестой элементы И и одновибратор, вход которого подключен ко входу умножителя, выход — к первому входу пятого эле5 мента И и,через первый элемент НЕ, к первому входу шестого элемента И, выход которого подключен к первому входу интегратора, вто рой вход которого подключен к выходу пятого элемента И, второй вход которого подключен к выходу второго элемента И и входу вто. рого элемента НЕ, выход которого подключен ко второму входу шестого элемента И.

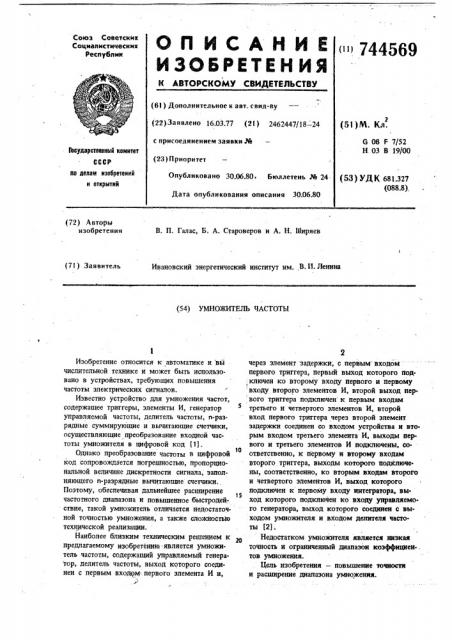

На фиг. 1 представлена блок-схема умножителя частоты; на фиг. 2 — направленный граф; на фиг, 3 — временная диаграмма работы элемейтов уь1но>кителя.

Умножитель частоты содержит делитель 1 частоты, выходом соединенный с первым входом элемента 2 И и,через элемент задержки 3, с первым входом триггера 4, второй вход которого связан через элемент 5 задержки с вхо- дом умножителя и первым входом элемента

6 И. Первый выход триггера 4 подключен квторым входам элементов 2 и 7 И, а второй .выход — ко вторым входам элементов 6 и

8 И. Выходы элементов 2 и 6 И подключены к входам триггера 9, первым выходом соеди. ненного с первым входом элемента 7 И, а вторым выходом — с первым входом элемента

8 И. Выход элемента.7 И подключен ко второму входу элемента 10 И, и через инвертор

11, к второму входу элемента 12 И.

Первый вход элемента 12 И через инвертор

13 связан с первым входом элемента 10 И и выходом одновибратора 14, вход которого подключен к входу умножителя. При этом, выход элемента 10 И соединен с прямым входом интегратора 15, а выходы элементов 8 и 12 И связаны с инверсным входом интегратора 15, выход которого подключен к входу управляемого генератора 16. Выход генератора 16 соединен с входом делителя 1 частоты.

Умножитель частоты работает следующим образом.

В исходном состоянии на первых выходах триггеров 4 и 9 присутствуют нулевые потен-. циалы. Эти состояния триггеров принимают за нулевые, а состояние, когда нулевые потенциалы присутствуют на вторых выходах этих триггеров, принимают за единичные. На направленном "графе (фиг. 2) эти состояния обозначены через 1 и 0 и показаны в кружках, а стрелками обозначены переходы из одного состояния в другое под действием отдельных импульсов А или Б. Общее состояние схемы, когда оба триггера в нулевых состояниях, обозначено цифрой 17. В этом состоянии на элемент

6 И с выхода триггера 4 подается сигнал за-

5 74456 ратора подается нулевой сигнал 12. С выхода интегратора 15 снимается постоянное напряжение, при котором управляемый генератор генерирует импульсы с частотой f> N, где f>>— частота входных импульсов, М вЂ” коэффициент деления делителя 1 частоты. Как видно из диаграммы (фиг. 3), величина фазового рассогласования импульсов А и Б в установившемся режиме равна длительности импульсов одновибратора. При увеличении, по каким-либо причинам, величины фазового рассогласования импульсов А и Б увеличивается длительность им- пульсов 10 на прямом входе интегратора 15, а уменьшение рассогласования приводит к исчезновению импульсов 10 и появлению импуль- ц сов 12 (П участок временной диаграммы фиг. 3) на инверсном входе интегратора.

Следовательно, выходное напряжение интегратора и частота управляемого генератора 16 изменяются в необходимую сторону до тех пор, 2q пока величина фазового рассогласования не станет равной длительности импульсов одновибратора 14, При резком изменении входной. частоты изменяется знак фазового рассогласования, и на 25 инверсный вход интегратора 15 подается широтно-импульсный сигнал с выхода элемента 8 И, изменяя в необходимую сторону напряжение интегратора и частоту управляемого генератора.

Благодаря этому, в схеме умножителя исключается режим биений и устраняется опрокидывание регулирования. Исключение цепи тактования из схемы известного устройства для умножения частот и введение одновибратора и дополнительных логических элементов И поз- З воляет в установившемся режиме работы умножителя значительно уменьшить длительность импульсов, поступающих на интегратор 15, что обеспечивает уменьшение пульсации выходного напряжения интегратора и увеличение равномерности выходной частоты умножителя (точность умножения). При этом (в противоположность известному), на вход триггера 4 поступают две последовательности импульсов с фазовым сдвигом, по времени равным длительности импульсов одновибратора, что значительно больше величины с. Это обеспечивает нормальную работу умножителя, а именно исключает одно. временный приход импульсов на вход тригге/ ра 4 при значительных внешних возмущениях, 5О вызывающих фазовый сдвиг поступающих последовательностей имйульсов. Из временных диаграмм на фиг, 3 видно, что длительность входных импульсов интегратора 15 не зависит от времени Г, а определяется в установившемся режиме только величиной утечки напряжения на интеграторе. Ввиду того, что в предлагаемом умножителе утечка напряжения интегратора не должна обеспечивать расход (списывание) напряжения интегратора, накопленного за время

, как это делается в известном, то, конструктивно, интегратор может выполняться с величиной утечки напряжения на порядок меньшей, чем в противопоставляемом устройстве, что улучшает точность 1гмножения.

Исключение цепи тактования устраняет также зону нечувствительности в замкнутом контуре регулирования схемы умножителя. Благодаря этому, понижение входной частоты умножителя не приводит к искажению фазового ° положения импульса входного сигнала и увеличению неравномерности выходной частоты.

Устойчивость умножителя в этом случае увеличивается.

Таким образом, исключение из схемы умножителя цепи тактования и введение новых элементов — одновибратора, инверторов и дополнительных элементов И позволяет повысить точность и расширить диапазон коэффитщентов умножения умножителя. Сравнительные испытания данного устройства с известным устройством показали, что введение новых элементов дает возможность обеспечить мгновенную точность умножения частоты не хуже 0,01% в диапазоне изменения коэффициентов умножения от 20 до 1000.

Формула изобретения

Умножитель частоты, содержащий управляемыи генератор, делитель частоты, выход которого соединен с первым входом первого элемента И и, через элемент задержки, с первым входом первого триггера, первый выход которого подключен ко второму входу первого и первому входу второго элементов И, второй выход первого триггера подключен к первым входам третьего и четвертого элементов И, второй вход первого триггера через второй элемент задержки соединен со входом устройства и вторым входом третьего элемента И, выходы первого и третьего элементов И подключены, соответственно, к первому и второму Входам второго триггера, выходы которого подключеиы, соответственно, ко вторым входам второго и четвертого элементов И, выход которого подключен к первому входу интегратора, выход которого подключен ко входу управляемого генератора, выход которого соединен с выходом умножителя и входом делителя частоты, о тл и ч а ю шийся тем, что, с целью повышения точности и расширения диапазона умножения умножителя, он содержит первый и второй элементы НЕ, пятый и шестой элементы И и одновибратор, вход которого, подключен ко входу умножителя, выход — к первому входу пятого элемента И и, через первый элемент НЕ, к первому входу шестого элемента И, выход которого подключен к первому входу интегра 445 о9

Составитель P. Яворовская

Техред M. Кузьма Корректор Н. Григорук

Редактор И. Канкина

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3794/13

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

7 тора, второй вход которого подключен к выходу пятого элемента И, второй вход которо го подключен к выходу второго элемента И и входу второго элемента НЕ, выход которого подключен.ко второму входу шестого элемента И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР Р404085, кл. 6 Об F 7/39, 1973.

2. Авторское свидетельство СССР по заявке

F2183038, кл. 6 06 F 7/39, 20.10.75.