Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Союз Советскнк

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<" 744572 (6l ) Дополнительное к авт, свид-ву (22) Заявлено 03.04.78 (21) 2600632/18 — 24 с присоединением заявки,% (51) М. Кл.

6 06 F 9/16

Воударствввиый комитет

СССР (23) Приоритет

Опубликовано 30.06.80. - Бюллетень ¹24

II0 делам иэобрвтеиий и открытий (53) УДК 681.14 (088.8) Дата опубликования описания 30.06.80 (72) Авторы изобретения

Н. А. Сирота и О. И. Таран

Киевский ордена Трудового Красного Знамени завод вычислительных и управляющих машин . (7l ) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано в микропрограммных процессорах ЦВМ.

Известны микропрограммные устройства управления, содержащие память микрокоманд, дешифраторы, генератор тактирующих импуль5 сов (1).

НеДостатком устройства является невозможность выполнения операции переписи содержи- . мого памяти микрокоманд в оперативную лаю мять.

Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее блок памяти, генератор тактовых импульсов, регистр, т5 дешифраторы, логические схемы И и ИЛИ (2).

Недостатком устройства является невозможность использования его для выполнения переписи содержимого памяти микрокоманд в оперативную память, так как оно работает по одному циклу. Цикл работы устройства должен быть различным в зависимости от того, выбраНа ли в данном цикле микрокоманда, подлежащая обработке (обычный цикл), нли микрокоманда, подлежащая переписи в оперативную память. Если в цикле выбрана микрокоманда для переписи в оперативную память, то в отличие от обычного цикла необходимо запретить все действия но выбранной микрокоманде и сформировать адрес перехода на продолжение микропрограммы переписи.

Цель изобретения — расширение функциональ. ньтх возможностей за счет осуществления перепйси содержимого памяти микрокоманд в оперативную память.

Эта цель достигается тем, что в устройство, содержащее генератор тактирующих импульсов, выход которого соединен с первым входом де- . шифратора выборки, второй вход которого соединен с выходом регистра адреса, а выход— со входом блока памяти, выход которого соединен со входом регистра микрокомаиддервая и вторая группы выходов регистра микрокоманд соединены с первой и второй группами входов блока формирования адреса микрокомвнды соответственно, третья группа выходов регистра микрокоманд соединена с первой группой входов дешифратора микроопераций, четвертый

744572 выход регистра микрокоманд соединен с первым выходом устройства, третья группа входов блока формирования адреса микрокоманды со,единена с группой входов устройства, введены группа элементов И, группа элементов ИЛИ, триггер н элемент задержки, причем вход элемента задержки соединен с первым выходом дешифратора микроопераций, вторая группа выходов которого соединена со второй группой выходов устройства, выход элемента задержки соединен со входом триггера, единичный выход триггера соединен с первыми входами элементов ИЛИ группы и с третьим выходом устройства, вторые входы элементов ИЛИ группы соединены с вйходом блока формирования адреса микрокоманды, а выходы — со входами старших разрядов регистра адреса, нулевой выход триггера соединен со вторым входом дешифратора микроопераций и с первыми входами элементов И группы, вторые входы кото- рых соединены с выходами блока формирования адреса микрокоманды, а выходы — со входами младших разрядов регистра адреса.

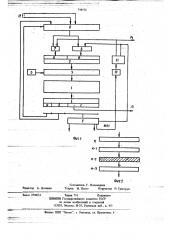

"На фиг, 1 представлена блок-схема устройства; на фиг. 2 — часть микропрограммы, выполняющей перепись содержимого памяти микрокоманд в оперативную память.

Микропрограммное устройство управления содержит блок 1 памяти (память микрокоманд), регистр 2 адреса, дешифратор 3 выборки, регистр 4 микрокоманд, генератор 5 тактовых импульсов, блок 6 формирования кода адреса микрокоманды, группу элементов 7 ИЛИ группу элементов 8 И, дешифратор 9 микроопераций, элемент 10 задержки, триггер 11, вход

12, выходы 13 и 14.

Длина микрокоманды разделена на разряды управления а, которые определяют каким образом должен формироваться адрес следующей микрокоманды, адресную часть Ь, которая используется для формирования адреса следующей микрокоманды и операционную часть с, которая задает набор микроопераций. Нулевой код в операционной части означает отсутствие микроопераций.

Работа устройства в пределах цикла различна, в зависимости от того, выбрана ли на регистр 4 микрокоманд, микрокоманда подлежащая переписи в оперативную память или нет.

При выборке микрокоманды, не подлежащей переписи в оперативную память, устройство работает следующим образом.

По сигналу, поступающему из генератора 5 тактовых импульсов на дешифратор 3 выборки, из памяти микрокоманд 1, считывается микрокоманда по адресу, сформированному в предыдущем цикле на регистре 2 адреса. Считанная микрокоманда принимается HR регистр

4 мнкрокоманд.

4 . Операционная часть микрокоманды подается на дешифратор 9 микроопераций. Триггер 11 установлен- в нулевое состояние .и потенциал, поступающий с нулевого плеча триггера на дешифратор 9, разрешает дешифрацию операционной части микрокоманды и выдачу микроопераций.

Разряды управления а, поступающие иэ резистора микрокоманд 4 на блок 6, определяют каким образом должен сформироваться код адреса следующей микрькоманды, Код адреса формируется по значению адресной части микрокоманды b,ïîñòóïàþùåé с регистра 4, или по значению одного из регистров ветвления.

Коды из регистров ветвления поступают по входу 12.

Регистр 2 адреса микрокоманд условно разбит íà две группы разрядов А и В, на входы которых стоят группы логических элементов

7 ИЛИ и 8 И.

Код адреса, сформированный блоком 6, подается на первые входы элементов 7 и 8.

На вторые входы элементов 7 заведен еди, ничный выход триггера 11, а на вторые входы элементов 8 — нулевой выход триггера 11.

Так как триггер 11 находится в нулевом состоянии, то код адреса, сформированный блоком

6„заносится через элементы 7 и 8 в регистр

2 адреса.

Выход регистра 2 адреса подается на вход дешифратора 3 выборки. Генератор 5 тактовых импульсов выдает очередной сигнал выборки и цикл повторяется снова, Для разбора работы микропрограммного устройства управления во время выборки микрокоманды, подлежащей переписи в оперативную память, рассмотрим алгоритм микропрограммы переписи содержимого памяти микрокоманд в оперативную память.

Микропрограмма переписи состоит изб микрокоманд и за один цикл микропрограммы происходит перепись одной микрокоманды.

На фиг. 2 представлена часть микропрограммы переписи, где происходит выборка из памяти микрокоманд микрокоманды, подлежащей переписи.

Микрокоманда и читает текущее значение адреса памяти микрокоманд из ячейки местной памяти и помещает его на сумматор. Микрокомщца и+1,является микрокомандой, которая формирует адрес микрокоманды по значению младших разрядов .сумматора. То есть микрокоманда n+2 выбирается по текущему значению адреса памяти микрокоманд и является микрокомандой подлежащей переписи. В микрокоманде n+I записана микрооперация (обозначенная M01), которая воздействует на устройство микропрограммного управления таким образом, что запрещается действие по кодам микг

744572

6 процессорах HBM позволяет значительно расширить функциональные возможности процессора.

5 Формул а

5 рокоманды n+2 и выполняется переход на мик рокоманду n+3. Код микрокоманды n+2 помещается в один из информационных регистров и затем записывается в оперативную память.

Микропрограммное устройство управления, во время выполнения указанного участка микропрограммы, работает следующим образом.

После выборки микрокоманды n+1 и установки ее на регистре 4 микрокоманд, разряды управления а поступают на блок 6 и обеспе- 10 чивают формирование кода здреса по содержимому сумматора. Содержимое сумматора поступает по входам 12.

Триггер 11 в нулевом состоянии разрешает занесение кода адреса из блока 6 через элемен- 15 ты 7 и 8 в регистр 2 адреса, Генератор 5 тактовых импульсов выдает сигнзл выборки и начинается считывание микрокоманды и+2, Операционная часть микрокомзнды n+1 по- 2g ступает на дешифратор 9, где расшифровывается и выдается в виде микроопераций.

Микрооперация М01, через элемент 10 задержки, устанавливает в единичное состояние триггер 11. Элемент 10 задержки подбирается 2s таким образом, чтобы триггер 11 устанавливался к моменту установки на регистре 4 кода микрокоманды n+2, Единичное плечо триггера 11 поступает на элементы 7 и обеспечивает установку в единич- 3g ное значение группы старших разрядов А регистра 2 здреса, Нулевое плечо триггера 11 поступает на элементы 8 и обеспечивает занесение в млздшие разряды В регистра 2 нулевого кода. Таким образом в регистре 2 формируется фиксированный адрес микрокоманды n+3. Нулевое плечо триггера 11 поступает также на дешифратор 9, запрещая дешифрацию операционной части микрокоманды n+2. 40

Код микрокоманды n+2 поступает по выходу 13 на вход одного из информационных регистров процессора. Единичный выход триггера 11 по выходу 14 также подается на вход информационного регистра; обеспечивая занесение в него кода микрокоманды n+2.

Триггер 11 динамический, К моменту установки на регистре 4 микрокоманды и+3 он сбрасывается в нулевое состояни В следующем цикле устройство микропрограммного управления работает обычным образом.

Применение предлагаемого микропрограммного устройства управления в микропрограммных изобретения

Микропрограммное устройство управления, содержащее генератор тактирующих импульсов, выход которого соединен с первым входом дешифратора выборки, второй вход которого соединен с выходом регистра адреса, а выход— со входом блока памяти, выход которого соединен со входом регистра микрокоманд, первая и вторая группы выходов регистра микрокоманд соединены с первой и второй группами входов блока формирования адреса микрокоманд соответственно, третья группа выходов регистра микрокоманд соединена с первой с группой входов дешифратора микроопераций, четвертый выход регистра микрокоманд соединен с первым выходом устройства, третья группа входов блока формирования адреса микрокоманды соединена с группой входов устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет осуществления переписи содержимого памяти микрокоманд в,оперативную память, в него введены группа элементов И, группа элементов ИЛИ, трипер и элемент задержки, причем вход элемента задержки соединен с первым выходом дешифратора микроопераций, вторая группа выходов которого соединена со второй группой выходов устройства, выход элемента задержки соединен со входом триггера, единичный выход триггера соединен с первыми входами элементов ИЛИ группы и с третьим выходом устройства, вторые входы элементов ИЛИ группы соединены с выходом блока формирования адреса микрокоманды, а выходы — со входами старших разрядов регистра адреса, нулевой выход триггера соединен со вторым входом дешифратора микроопераций и с первыми входами элементов И группы, вторые входы которых соединены с выходом блока формирования адреса микрокоманды, а выходы — со входами младших разрядов регистра адреса.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР М 264783, кл, G 06 F 9/14, 1968.

2. Авторское свидетельство СССР 8 91201, кл. G 06 F 9/1.6, 1969 (прототип).

744572

44»зд Ул» у

Составитель,Г. Пономарева

Техред М. Петко Корректор Н. Григорук

Редактор А. Долинич

4айййв:юВ Фйю цаа.» а -, Заказ 3794/13

Тираж 751 Подписное

UHNHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4