Устройство для обнаружения и исправления ошибок арифметических операций

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТИЛЬСТВУ

744583

Союз Советских

Социалистических

Реслублнк (61) Дополнительное к авт. свид-ву (22) Заявлено 143.177 (21) 2543552/18-24 с присоединением Заявки № (23) Приоритет

Опу(зликовано 3006.80. Бюллетень ¹ 24

Дата опубликования описания 3006,80

{51) M. К,.2 G 06 F 11/08

Государственный комитет

СССР ио делам изобретений и открытий

{53) УДК 621. 326. 7 (088. 8) (72) Авторы изобретения

И . Я.Акушский, В.М. Бурцев, Л.В. Каплан и Г. Г. Смолко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И:ИСПРАВЛЕНИЯ

ОШИБОК АРИФМЕТИЧЕСКИХ ОПЕРАЦИЙ

Изобретение относится к автоматике и вычислительной технике, в частности может быть использовано для контроля и исправления ошибок при проведении арифметических операций в

ЭВМ.

Известно устройство для контроля работы арифметического устройства ЭВМ содержащее регистр информационных разрядов, регистр контрольных разрядов, блок модульной свертки и схему сравнения (1).

Основными недостатками устройства являются низкие функциональные воз/ можности, заключающиеся в обнаруже- 15 нии одинаковых ошибок.

Наиболее близким по технической сущности к изобретению является устройство для обнаружения и исправления ошибок в системе остаточных клас-20 .сов, содержащее регистр числа, первый и второй регистры контрольных разрядов, выходы которых соединены с первыми входами соответственно первого и второго сумматоров, вторые входы которых соединены с выходами соответственно первого и второго блоков модульной свертки, входы которых объединены и соединены с выходами регистра числа, блока памяти, входы 30

2 | которого соединены с выходами первого и второго сумматора, третий сумматор, выходы которого соединены с выходом регистра числа, выходом блока памяти, выходами первого и второго регистров контрольных разрядов 12).

Недостатком его является узость области использования, а именно только в ЭВМ, работающих в системе,исчисления остаточных классов.

Цель изобретения — расширение области применения устройства, благодаря обеспечению возможности обнаружения и исправления ошибок арифметических операций как в позиционных, так и непоэиционных системах исчисления.

Укаэанная цель достигается тем, что в устройство введены четвертый и пятый сумматоры, третий и четвертый регистры контрольных разрядов, выходы которых соединены с входами соответственно четвертого и пятого сумма-! торов, вторые входы которых соединены с выходами соответственно первого и второго регистров контрольных разрядов, входы которых соединены с выходами ссютветственно четвертого и пятого сумматоров, выходы третьего сумматора соединены со входами первого и второго блоков модульной сверт744583 ки, выходы. которых соединены со входами соответственно третьего и четвертого регистров контрольных раэря» дов.

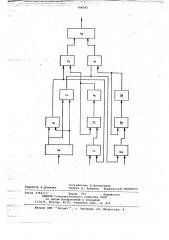

На чертеже приведена функциональная схема устройства для обнаружения и исправления ошибок арифметических операций.

Устройство содержит первый регистр

1 контрольных разрядов второй регистр 2 контрольных разрядов первый сумматор З второй сумматор 4у блок

5 памяти первый блок б модульной свертки, второй блок 7 модульной: свертки, третий сумматор 8, третий регистр 9 контрольных разрядов, четвертый регистр 10 контрольных разрядов, четвертый сумматор 11, пятый сумматор 12. . Работа устройства для обнаружения и исправления ошибок арифметических операций осуществляется в четыре такта.

В подготовительном такте работы устройства на вход третьего сумматора 8 подаются значения информационных частей первого и второго операнда.

Значения контрольных частей первого операнда посылаются в первый и вто рой регистры 1 и 2, а значения конт.-, рольных частей второго операнда — в третий и четвертый регистры 9 и 10 контрольных разрядов.

Для осуществления контроля с коррекцией арифметического устройства каждый из операндов сопровождается двумя контрольными частями, вычисляемыми по формулам

55 истинные значения контрольных частей

60 ®, и $ с выходов первого и второго блоков 6 и 7 модульной свертки и расчетные значения контрольных частей .ф и у с выходов первого и второ.го регистров 1 и 2 подаются на соот65 ветствующие входы первого и второго

rnoal. Р

mod. Р г» 3. y, + AÀ Ф +,", Л а(mod.P, (1)

1 4 ф =" Л сА,>A. A +; +jl AП1 69 (2)

t где P u P значения контрольных

2, модулей;

Jl. - константы системы счисления (i=1,m; j=l,2);

Ю вЂ” значение группы двоичных разрядов (i=1,m) .

При этом, каждый иэ операндов считается состоящим из m групп двоичных разрядов. Число разрядов составляющих группы выбирается исходя из наиболее вероятной кратности ошибки, т.е. Устройство позволяет скорректировать сшибку любой кратности, возникшую внутри группы.

В первом рабочем такте на четвертом и пятом сумматорах 11 и 12 вычисляются промежуточные значения контрольных частей результата, а именно здесь .у и — первые контрольные у. части первого и второго операндов, хранившиеся в регистрах

9и l;

g и g — вторые контрольные части первого и второго операндов, хранившиеся в регистрах

10 и 21 I

М вЂ” знак выполняемой one I0 рации.

Вычисленные значения у и у запоминаются соответственно в первом и

1 втором регистрах 1 и 2.

Одновременно в третьем сумматоре

13 8 находится значение результата выполняемой операции, при этом фиксируются переносы, возникающие иэ груп- . пы в группу.

Зафиксированные моменты переносов

20 со второго выхода третьего сумматора подаются на вторые входы первого и второго блоков модульной свертки б и 7 для определения величин поправок 1 2 и - . Работа каждого иэ этих

К) лк) блоков описана соответствующими срав-. нениями (1) и (2), причем а 1, если в i-ую группу был перенос,и А; = -2 если перенос был иэ i-ой группы (здесь 8 — количество двоичных разрядов в i-ой группе, а i=1 m) .

С выходов первого и второго блоков модульной свертки б и 7 снимаются величины поправок ф> и ), которые запоминаются в третьем и четвертом регистрах 9 и 10 контрольных раэря35 доз.

Во втором такте работы устройства с помощью первого и второго блоков б и 7 модульной свертки вычисляются значения контрольных частей g и

40 результата операции,,который йодается с первого выхода третьего сумматора

2 на первые входы первого и второго блоков б и 7 модульной свертки.

Одновременно вычисляются расчет45 .ные значения контрольных частей и )Г результата по формулам р =ф Ф () mod.Р

Здесь ф ),.ф и, ) хранятся на первых и вторых регистрах 9 и 10 контрольны:: частей и регистрах 1 и 2.

Величины х и $ запоминаются соот и и ветственно на первом и втором регистрах 1 и 2.

В третьем такте работы устройства

744583 .сумматоров 3 и 4 с образованием на их выходах синдрома ошибки равного ! д g — jy mod. Р д ь3 - ttlod

В соответстййй со значением синдрома ошибки д,, подаваемого на входы блока 5 памяти, на его выходе вырабатывается константа сшибки, поступающая на выход устройства для контроля с коррекцией арифметического устройства.

Предлагаемое устройство работает с операндами, представленными в системе остаточных классов, причем в этом случае в качестве групп двоичных разрядов выступают значения остатков числа по рабочим основаниям системы счисления.

Pабота устройства остается беэ изменения, но при выполнении операций в системе счисления остаточных классов отсутствуют связи между группами разрядов. Следовательно, со второго выхода третьего сумматора 8 выдается нулевой сигнал и нет необходимости в вычислении величин поправок " и ф0 и последующей коррекции

1 значений у и g °

Использование в предлагаемом устройстве четвертого и пятого сумматоров, третьего и четвертого регистров контрольных разрядов позволяет расширить область применения устройства, применяя его для контроля с коррекцией ошибок арифметических устройств, 35 работающих как в позиционной системе счисления, так и в системе счислений остаточных классов.

Формула изобретения

Устройство для обнаружения и 4р исправления ошибок арифметических операций, содержащее первый и второй регистры контрольных разрядов, выходы которых соединены с первыми входами соответственно первого и второго сумматоров, вторые входы которых со единены с выходами соответственно первого и второго блоков модульной свертки, а выходы первого и второго сумматоров соединены со входами бло" ка памяти, третий сумматор, о т л и" ч а ю щ е е с s тем, что, с целью расширения области применения устройства, благодаря обеспечению воэможности обнаружения и исправления оши-бок арифметических операций как в позиционных, так и, непозиционных системах исчисления, в устройство введены четвертый и пятый сумматорй, третий и четвертый регистры контрольных разрядов, выходы которых соединены с первыми входами соответственно четвертого и пятого сумматоров, вторые, входы которых соединены с выходами соответственно первого и второго регистров контрольных разрядов, входы которых соединены с выходами соответственно четвертого и пятого сумматоров, выходы третьего сумматора соединены со входами первого и второго блоков модульной свертки выходы которых соединены со входаий соответственно третьего и четвертого регистров контрольных разрядов.

Источники информации, принятые во внимание при экспертизе

1. Ушакова Г.Н. Аппаратный контроль и надежность. специализированных

ЭВМ. М., Советское радио, 1969, с. 64-68.

2. Авторское свидетельство СССР по заявке Р 2439703/24, кл. G 06 F 11/08, 26.01.77 (прототип) .

744583

Составитель В. Евстигнеев

Техред Н. Бабурка КорректорА. Гриценко

Редактор А.Долинич

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Заказ 379 4/13 Тираж 75 1 Подпис но е

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5