Микропрограммный процессор

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистическик

Республик

«>744587 (61) Дополнительное к авт. свид-ву (22) Заявлено 030478 (21) 2600631/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 300680. Бюллетень № 24

Дата опубликования описания 300680

G 06 F 15/00

Государственный комитет

СССР по делам изобретений и открытиИ ($Q) Д((681. 325 (088 8) (72) Авторы изобретения

В.И. Аноприенко, А.Г. Калашник, Н.A. Сирота и В.Н. Харитонов

Киевский ордена Трудового Красного Знамени завод вычислительных и управляющих машин (71) Заявитель (54) МИКРОПРОГРАММНЫЙ ПРОЦЕССОР

Изобретение относится к вычислительной технике и может применяться в цифровых вычислительных машинах с программным управлением.

Известен процессор ЕС 1020, который для подсчета текущего адреса команды использует арифметический блок, где после очередного считывания иэ оперативной памяти полуслова (два байта) происходит увеличение текущего адреса командной информации на два (1) .

Текущий адрес хранится в адресном регистре или в ячейке местной памяти. При выборе команды формата полуслова необходимо в арифметическом блоке сделать операцию два-один раэ, формата слова — два раза, формата три полуслова — три раза. Это приводит к снижению быстродействия процессора, так как арифметический блок занят подсчетом адреса и не может заниматься обработкой команды в то время, когда командная инФормация уже имеется в процессоре.

Наиболее близким по технической сущности к предлагаемому является микропрограммный процессор (модель

5Q система 3 60 фирмы . Л ВМ), который 3() 2 для адресации команд содержит блок выработки адреса команды. Этот блок состоит из 24-разрядного регистра адреса команды и 24-разрядного счетчика адреса команды, которые соединены между собой, а также с выходными шинами суммаТора, регистром адреса оперативной памяти и регистром данных оперативной памяти С22.

Командная информация читается из оперативной памяти по словам (4-е байта) по адресу, определяемому регистром адреса команды, и затем, в счетчике происходит увеличение адреса на число байтов, содержащихся в текущей команде, методом прибавления двойки и (или) четверки к текущему значению счетчика. Затем, в начале следующего цикла обработки команды, происходит передача обновленного адреса из счетчика в регистр адреса оперативной памяти и в регистр адреса команды.

Недостаток данной схемы заключается в том, что для подсчета адреса команды используется много оборудования (24-разрядный счетчик ко744587 манд и 24-разрядный регистр хранения адреса) .

Цель изобретения - сокращение оборудования. микропрограммного процессора путем исключения счетчика команд и регистра адреса команд без потери быстродействия.

Эта цель достигается тем, что микропрограммный процессор, содержатций регистр коммутации, первый адрес ный вход которого соединен с выходом блока местной памяти, информационный вход является входом устройства, второй адресный вход соединен с ныходом арифметического блока, а выходс первыми входами блока местной памяти, регистра команд, арифметичесКого блс.<а и с выходом устройства, выход блока и с выходом устройства, выход регистра команд соединен с первым входом блока микропрограммного управления, выход которого соединен с управляющими входами регистра коммутации, регистра команд, арифметического блока и блока местной памяти, содержит блок формирования остатка, причем первый вход блока формирования остатка соединен с выходом регистра коммутации, второй вход — с выходом регистра команд, а управляющий вход — с выходом блока микропрограммного управления, а выход — со вторыми входами блока микропрограммного управления и арифметического блока.

Причем блок формирования остатка. содержит регистр остатка, дешифратор, двухразрядный сумматор, группы элементов И, элементы И, ЙЛИ, причем входы двух младших разрядов регистра остатка соединены с выходами первого и второго элемента ИЛИ соответственно, первые входы которых соединены с выходами элементов И первой и второй групп соотцетстненно, а вторые входы - с выходами элементов И третьей и четвертой групп соответственно, первые входы элементов И первой и второй групп и вход установки нуля .старшего разряда регистра остатка соединен с соответствующим выходом блока микропрограммного управления, вторые входы элементов И первой и второй групп соединены с выходами соответствующих разрядов регистра коммутации, йервые входы элементов

И третьей и четвертой групп соединены с первым входом элемента И и с соответствующим выходом блока микропрограммного управления, а вторые входы-с первым и вторым выходами двухразрядного сумматора cooT-. ветственно, выход переноса которого соединен со вторым входом элемента

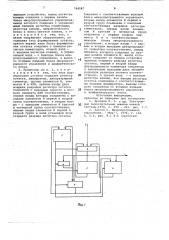

И, выход которого соединен со вхо дом установки единицы старшего разряда регистра остатка, первый и второй входы днухразрядного суммато-ра соединены с единичными выходами двух младших разрядов регистра остатка соответственно, а третий нход — с выходом регистра команд, все выходы регистра остатка соединены с соответствующими входами дешифратора, выходы которого соедидинены со вторыми входами блока микропрограммного управления и арифметического блока, На фиг. 1 изображена блок-схема микропрограммного процессора; на фиг. 2 — функциональная схема блока формирования остатка.

Микропрограммный процессор состоит из блока 1 микропрограммного уп

15 равления, шин 2 входа из оперативной памяти, регистра 3 коммутации, регистра 4 команд, блока 5 местной памяти, блока б формирования остатка, шин 7 выдачи в оперативную память и арифметического блока 8., Щ Выборка и отработка команд выполняется под управлением микропрограмм, которые хранятся и блоке 1 микропрограммного управления, который осуществляет адресацию, выборку микрокоманд

»5 и выдачу сигналов управления но нсе узлы процессора.

Командная информация из оперативной памяти выбирается двойным словами (8 байтов) и по шинам 2 принимается на регистр 3 кЬммутации.

Из регистра 3 коммутации очередная команда помещается в регистр 4 команды, а остаток командной информации — в фиксированные ячейки 5 местной памяти.

Код команды из регистра 4 команды поступает н блок 1 микропрограм-. много. управления и однозначно укаI зывает начало микропрограммы текущей команды.

40 Команды располагаются в оперативной памяти с границы полусМова.

Выбранная командная информация может быть длиной в четыре, три, два или одно полуслово. Если адресация оперативной памяти выполняется с точностью до байта, то три последние разряда адреса указывают количество байтов выбранной командной информации, а два старших разряда из этих трех — количество полуслов.

Очередная отрабатываемая команда может быть длиной в одно, два или три полуслова. Формат (длина) команды определяется соответствующими разрядами кода операции.

В зависимости бт величины выбранной командной информации и формата текущей команды в блоке б формирования остатка устанавливается код, который определяет величину остатка.

После выполнения текущей .команды и выхода на очередную, блок

1 микропрограммного управления анализирует состояние, блока б форми рования остатка, и если остаток ест»

744587

60 то очередная команда или начало ее читается из блока 5 местной памяти и через регистр 3 коммутации помещается в регистр 4 команд, Если в остатке часть команды или остаток нулевой, то происходит чтение командной информации иэ опера- тивной памят и ..

Адрес командной информации хра-. нится в фиксированной ячейке блока 5 местной памяти. При чтении командной информации адрес читается .из блока 5 местной памяти и через регистр 3 коммутации по шинам 7 выдается в оперативную память, Параллельно он поступает в арифметический блок 8, где увеличивается на величину двойного слова и через регистр 3 коммутации опять записывается в блок 5 местной памяти. T. е. во время чтения командной информации происходит подготовка адреса для

20 следующего чтения.

Таким образом, в процессе выполнения программь|, в фиксированной ячейке 5 местной памяти хранится продвинутый адрес, определяющий 25 командную информацию с точностью до двойного слова, и командная информация выбирается иэ оперативной памяти двойными словами.

Для получения адреса следующей 30 команды при выполнении некоторых команд переходов и прерываний, продвинутый- адрес корректируется на величину остатка.

Коррекция выполняется в арифме- 35 тическом блоке 8 и заключается в вычитании константы их текущего адреса командной информации. Константа определяет количество полуслов командной информации, находящейся щ в остатке, и формируется в арифметическом блоке 8 по значениям потенциалов остатка, поступающим иэ блока б формирования остатка.

На фиг. 2 представлен блок б формирования остатка, который состоит из регистра 9 остатка, дешифратора 10, двухразрядного сумматора 11, первой группы элементов И 12, второй группы элементов И 13, элемента И 14, элементов ИЛИ 15.

Величина остатка задается кодом трехраэрядного регистра 9:

000 — остаток длиной четыре полуслова (П04);

X01 — остаток длиной три полуслов а (ПОЗ);

Х10 — остаток длиной два полуслова (П02);

X1l — остаток длиной одно полуслов а (П01 );

100 — остаток отсутствует (ПОО) .

Х вЂ” разряд может принимать любое значение.

Формат команд определяется двумя разрядами кода операции:

01 — команда длиной полуслова;

10 — команда длиной слово;

11 — команда длиной три полуслова.

Во время начальной выборки командной информации (по пуску или выполнению, перехода) значение двух младших разрядов регистра 9 остатка устанавливается по управляющему сигналу lб, приходящему иэ блока 1 микропрограммного управления, и значению разрядов адреса команды, определяющих количество выбранных полуслбв, и поступающих из регистра 3 коммутации по шинам 17 и 18 через элементы 12 И,,15 ИЛИ.

Старший разряд регистра 9 остатка по сигналу lб устанавливается в нуль.

В дальнейшем при переходе на отработку очередной команды, регистр

9 остатка переключается по управляющему сигналу 19, поступающему из блока 1 микропрограммного управления. Переключение заключается в сложении предыдущего значения кода двух младших разрядов регистра 9 остатка с Двухразрядным кодом, определякщим формат команды и поступающим с регистра 4 команд, по шине 20,, на двухразрядном сумматоре 11. Двухраэрядный код суммы через элементы

13 И и 15 ИЛИ заносится в два младших разряда регистра 9 остатка. Если в процессе сложения возникает перенос из старшего разряда, то через элемент 14 И старший разряд регистра

9 остатка устанавливается в единицу.

Выходы регистра 9 остатка поступают на вход дешифратора 10, где происходит дешифрация кода в потенциалы, определяющие величину Ьстатка

ПОО, П01, П02, ПОЗ и FI04. Эти потенциалы поступают в блок 1 микропрограммного управления и арифметический блок 8.

Размещение текущего адреса команды в ячейке местной памяти, счет адреса в пределах;двойных слов в арифметическом блоке и применение блока формирования остатка позволяет отказаться от использования счетчика команд и регистра адреса команд, что приводит к уменьшению оборудования процессора.

Формула изобретения

1, Микропрограммный процессор, содержащий регистр коммутации, первый адресный вход которого соединен с выходом блока местной памяти, информационный вход является входом устройства, второй адресный вход соединен с выходом арифметического блока, а выход — с первыми входами блока местной памяти, регистра команд, арифметического блока и с

744587 выходом устройства, выход регистра команд соединен с первым входом блока микропрограммного управления, вьжод которого соединен с управляющими входами регистра коммутации, регистра команд, арифметического блока и блока местной памяти, о тл и ч а ю шийся тем, что, с целью сокращения оборудования, он содержит блок формирования остатка, причем первый вход блока формирования остатка соединен с выходом регистра коммутации, второй вход— с выходом регистра команд, а управляющий вход — с выходом блока микропрограммного управления, а выход— со вторыми входами блока микропрограммного управления и арифметического блока.

2. Процессор,,по п. 1, о т л ич а ю шийся тем, что блок формирования остатка содержит регистр остатка, дешифратор, двухразрядный сумматор, группы элементов И, элемэнты И и ИЛИ, причем входы двух младших разрядов регистра остатка соединены с выходами первого и второго элемента ИЛИ соответственно, первые входы которых соединены с выходами элементов И первой и второй групп собтветственно, а вторые входы — с выходами элементов И третьей и четвертой групп соответственно, первые входы элементов И первой и второй групп и вход установки нуля старшего разряда регистра остатка соединен с соответствующим выходом блока микропрограммного управления, вторые входы элементов И первый и второй групп соединены с выходами соответствующих разрядов регистра коммутации, первые входы элементов И третьей и четвертой групп соединены с первым входом элемента И и с соответствующим выходом блока микропрограммного управления, а вторые входы — с первым и вторым выходами двухразрядного сумматора соответственно, выход переноса которого соединен со вторым входом элемента И, выход которого соединен со входом установки единицы старшего разряда регистра остатка, первый и второй входы двухразрядного сумматора соединены с единичными выходами двух младших разрядов регистра остатка соответ20 ственно, а. третий вход — с выходом регистра кОманд все выходы регистра остатка соединены с соответствующими входами дешифратора, выходы которого соединены со вторыми входами

25 блока микропрограммного управления и ариФметического блока.

Источники информации, принятые во внимание при экспертизе

Дроздов E. А. и др. Электронные вычислительные машины единой системы.1976, с. 259 — 261, рис. 7.7.

2. Хассон С. Микропрограммное управление. Мир, 1974, с . 162 и. 8.6, рис. 8.1 8.6 (прототип) 7445S7

Составитель Г. Пономарева

Редактор A. Долинич Техред Ж. Кастелевич КорректорИ. Муска

Подписное

Закаэ 3795/14 Тираж 751

ЦНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП. Патент, г. Ужгород, ул. Проектная, 4

I