Цифровой функциональный преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ (61) Дополнительное к авт. свид-ву (22) Заявлено 21.0777 (21) 2509607/18-24 5 М „г с присоединением заявки ¹

G 06 Г 15/34

Государственный комитет

СССР оо делам изобретений и открытий (23) Приоритет -—

Опубликовано 300680. Бюллетень № 24

Дата опубликования описания 300680 (5З) УДК 681. 327 (088.8) (72) Автор изобретени я

A. Л. Рейхенберг (71) Заявитель (54) ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

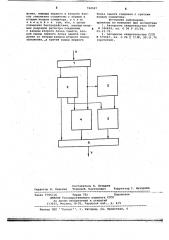

Устройство содержит регистр 1, блоки 2 и 3 памяти, блоки 4 и 5 умножения, сумматор б.

Блоки 2 и 3 памяти могут быть выполнены в виде одностороннего запоминающего устройства. Блоки 4 и 5 умножения могут быть выполнены в зависимости от требуемого быстродействия либо по последовательной схеме, либо в виде одностороннего запоминающего устройства. Сумматор б может быть вйполнен в виде параллельной схемы.

ЗО

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной реализа- ции вычисления функций в специализированных вычислительных машинах и системах для управления и регулирования в реальном масштабе времени.

Известен функциональный преобразователь, содержащий генератор импульсов, счетчики, дешифратор, блок памяти, блок умножения, схему совпадения и схему считывания (1).

Недостатком его является большой объем памяти и большое время для воспроизведения функции. 15

Наиболее близким техническим решением к предлагаемому является цифровой функциональный преобразователь, содержащий регистр, выходы старших разрядов которого соединены с входа- 20 ми первого блока памяти, первый выход первого блока памяти соединен с первым входом первого блока умножения, второй вход которого соединен с выходами младших разрядов регистра, выход второго блока памяти соединен с первым входом второго блока умножения, выходы первого и второго блоков умножения соединены с первым и вторым входом сумматора (2).

Устройство содержит, кроме .того, третий блок умножения.

Недостатком его является низкое быс тродейств ие.

Цель изобретения — повышение быстродейств ия.

Цель достигается тем, что выходы младших разрядов регистра соединены с входом второго блока памяти, второй выход первого блока памяти соединен со вторым входом второго блока умножения, а третий выход первого блока памяти соединен с третьим входом сумматора.

На чертеже представлена блок-схема устройства.

744 5gy 4

l старшими разрядаМ регистра 1.В блоке 3 памяти хранятся значения ь х,записанные по адресу а х,представленному младгаими разрядами регистра 1.В первом цикле вычисления по адресу х+дх, записанному в регистре l,èý блоков

2 и 3 памяти считываются соответствующие значения и пор аются на вход сумматора б и входы блоков 4 и 5 ум" ножения. Во втором цикле вычисления в блоке 4 производится умножение эначеьия 1/(1+х ) на значение г.х, в блоке 5 — умножение значения о х/ (1+х } на величину л х 2. Полученное произведение с выхода блока 4 суммируется с значением a ctg х в

15 сумматоре б. Полученное произведение с выхода блока 5 вычитается иэ суммы двух вышеуказанных значений в сумматоре б (вычитание может быть выполнено сложением дополнительного

QQ кода, подаваемого с.выхода блока 5).

Результат с выхода сумматора б ян— ляется значением обратного тригонометрического тангенса.

С труктура ЦФП одинакова для про25 цессов воспроизведения обратного и прямого тригонометрического тангенса. Различием являются содержания (запомненные данные). в блоках 2 и 3 памяти и операция сложение (вычитание) по нторому входу сумматора б.

Точность воспроизведения Функций прямого и обратного тригонометрического тангенса определяется длиной разрядной сетки регистра 1.

Время воспроизведения указанных

Функций зависит от времени выполь- нения операции умножения н блоках

4 и 5. При реализации этих блоков

4 и S умножения в виде одностороннего эапоминакшего устройства, время

4Q выполнения второго цикла равно времЕни обращения к памяти, т.е. равно одному такту. Общее время вычисления в этом случае определяется тремя таКтами. Для любого случая

45 общее время вычисления Т = Т + 2, где Тул„- время в тактах операции умножения.

Таким образом, по сравнению с известным предлагаемый преобразователь обладает большим быстродействием и более широкими функциональными возможностями.

Фсрмула изобретения

Воспроизведение Функций tg г. или

Оье1уХ в данном ЦФП осуществляется следугсшим образом.

В регистр 1 записывается код аргумента х. Старшие разряды аргумен та х являются адресом для обращения к блоку 2 памяти, н котором по каждому адресу записано одновременно тр значения „ считываемые одновременно.

Мггадшие разряды аргумента х являются адресом для обращения к блоку 3 памя ти и одновременно значением одного

-из cîìíîæèòeëåé для блока 4 умножения, вторым сомножителем для которог является значение с первого выхода блока 2 памяти. Значение с выхода блока 3 памяти является одним из сомножителей для блока 5 умножения, вторым сомножителем для которого является значение с второго выхода блока 2 памяти. Полученные произведения с выходов блоков 4 и 5 умножения и значение с выхода блока 2 памяти суммируются в сумматоре б, с вы хода которого снимается значение воспроизводимой Функции. Воспроизнедение функции производится в три цикла. В первом цикле производится запись аргумента и считывание чисел из блоков 2 и 3 памяти. Бо втором цикле производится умножение в блоках 4 и 5 умножения одновременно.

В третьем цикле производится сложение в сумматоре б.

При вычислении тригонометрического тангенса Ъу (х+лх) в блоке па- мяти 2 хранятся три значения (по первому выходу блока 2. (/сон х, по второму выходу 1(гх/eos х, по трет ему выходу tg х),записанные по одному адресу х, представленному старшими разрядами регистра 1. В блоке

3 памяти хранятся значения ь.х, записанные по адресу 6,х„ представленному младшими разрядами регистра 1.

B первом цикле вычисления по. адресу х + j х, записанному в регистре 1, иэ блоков 2 и 3 памяти считываются соответствующие значения и передаются на входы блоков 4 и 5 умножения и сугматора б. Во втором цикле вычисления н блоке 4,производит-ся умножение значения 1/cos х на значение ах, в блоке 5 — умножени значения Ъу х/сонг х на значение Ьх

Полученные произведения с выходов блоков 4 и 5 и значение tg х с третьего выхода блока памяти 2 суммируются в сумматоре б н третьем цикле ны- 55 числения. Результат с выхода сумматора б является значением тригонометрического тангенса.

При вычислении обратного тригонометрического тангенса avctg (х-г-ах) н щ блоке 2 памяти хранятся три значения (по первому выходу блока 2 1/ (1+Х ), по второму выходу х/ (I + х ) ., по третьему выходу aretg х ), записанные по одному адресу х, представленному 65

Цифровой функциональный преобразователь, содержащий регистр, выходы старших разрядов которого соединены с входами первого блока памяти, первый выход которого соединен с первым входом первого блока умножения, второй вход которого соединен с выходами младших разрядов регистра, выход второго блока памяти соединен с первым входом второго блока умно744597

Составитель Е. Пупырев

Редактор И. Нанкина Техред Ж. Кастелевич Корректор Г. Назарова

Заказ 3795/14 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 жения, выходы первого и второго блоков умножения соединены с первым и вторым входом сумматора, о т л ич а ю шийся тем, что, с целью повьпаения быстродействия, выходы младших разрядов регистра соединены 5 с входом второго блока памяти, второй выход первого блока памяти соединен со вторым входом второго блока умножения, а третий выход первого блока памяти соединен с третьим входом сумматора".

Источники информации, принятые во внимание при экспертизе

1. Авторское снидетельство СССР

Р 344444, кл. G 06 F 15/20, 03.12.70.

2. Авторское свидетельство СССР

Р 575647, кл. С 06 F 7/38, 30.11.76 (прототип).