Стохастический интегратор

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОЛ ЙСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТИЛЬСТВУ

< в744607 (61) Дополнительное к авт. свид-ву (22) Заявлено Q9Ql,78 (21) 2567888/18-24 с присоединением заявки N2 (23) Приоритет

Опубликовано 300680. бюллетень М 24

Дата опубликования описания 300680 (51)М. Кл.2

G 06 F 15/36

Государственный комитет

СССР по делам изобретений и открыти и (53) УДК 681.3 (088.8) В.Е. Иельник и A.Þ. Авилова (72) Авторы изобретения

Таганрогский радиотехнический институт им. В.Д. Калмыкова (71) Заявитель (54) СТОХАСТИЧЕСКИЙ ИНТЕГРАТОР

Изобретение относится к вычиолительной технике и может быть использовано при построении стохастических вычислительных устройств.

Известны стохастические интегра,торы, содержащие последовательно mразрядный накопитель подинтегральной функции, входы которого подключены ко входам интегратора и блок стохастического кодирования; состоит из

m-разрядной схемы сравнения чисел в параллельных кодах и генератора случайных чисел, представляющего собой

m датчиков равновероятных случайных двоичных последовательностей (1) и 15 (2) .

Недостатком этих йнтеграторов являются большие аппаратурные затраты, необходимые для построения параллель-20 ной схемы сравнения и многоразрядного генератора случайных чисел.

Наиболее близок к предлагаемоМу стохастический интегратор, содержащий реверсивный счетчик,суммирующий25 счетчик, одноразрядный датчик случайных чисел, группу элементов И и элемент ИЛИ, выход которого является вы- ходом интегратора, входами интегратора являются входы реверсивного счетчи Q0 ка, выходы элементов И подключены ко входам элемента .ИЛИ, выход однораз- . рядного датчика случайных чисел соединен со входом суммирующего счетчика, выходы которого подключены к импульсным входам соответствующих элементов И, выход переполнения реверсивного счетчика через инвертор и выходной вентиль подключен к выходу интегратора (3) .

Однако такой интегратор имеет существенный недостаток - интеграл, текущее значение Y которого находится в реверсивном счетчике, преобразуется в выходную стохастическую последсвательность Z с масштабом Р(х), т.е.

Р() = Р (х) 3

Р(г) — вероятность появления единицы в выходной последовательности

Р(Х)=0,о - вероятность появления единицы в последов ательности Х.

Умножение на масштаб Р(х) =0,5 при интегрировании приводит к увеличению веса последовательности Z что в бсльшинстве применений весьма нежелательно, так как приводит к снижению точности интегрирования.

744607

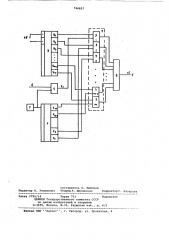

Вход l приращений интеграла а у (положительных и отрицательных) подключен ко входу младшего m-го разряда реверсивного счетчика 2. Выходы числовых разрядон реверсивного счетчика 2 подключены к потенциальным входам m зпементов И 3; (i=1,m), причем выход 1-го разряда (отсчет ведется со старшего разряда) подключен ко входу i-го элемента 3; .

Импульсные входы элементов И подключены к выходу элемента 4 запрета и к выходам счетчика 5. .Причем вход элемента 3 подключен к выходу элемента 4 запрета, а вход каждого элемента 3; (1=: 2, m) подключен к выходу (m-i+1) -ого разряда счетчика

5. Прямой вход элемента 4 запрета подключен к шине б синхронизирующих импульсов СИ. Выход датчика 7 случайной двоичной последовательности х подключен к запрещающему входу элемента 4 и к счетному входу счетчика 5. Выходы всех элементов 3; (1=1,m) подключены ко входам элемента ИЛИ 8, выход которого подключен к выходу 9 интегратора. устройство работает следующим образом.

l, 40

Цель изобретения — повьпление точ ности и упрок.ение интегратора.

Постанленная цель достигается тем, что в с-roxac;-ический интегратор содержащий ренерсинный счетчик,- суммирующий счетчик, одноразрядный датчик случайных чисел, группу элемен 5 тов И и элемент ИЛИ, выход которого является выходом интегратора,. входами инте гратора являются н ходы реверсивного "четчика, выходы элементов

И подключены «о входам элемента ИЛИ, выход одноразрядного датчика случайных чисел соединен со входом суммирующего счетчика, выходы которого подключены к импульсным входам соответствующих элементов И, соединенных 15 своими потенциальными входами с выходами (m — 1) младших разрядон реверсивного счетчика, дополнительно введен элемент запрета, выход которого подключен к импульсному входу ъ0 элемента И, соединенного своим потенциальным н ходом с в ыходом старшего разряда реверсивного счетчика, запрещающий вход элемента запрета соединен с выходом одноразрядного датчика случайных чисел, а прямой вход элемента запрета является в ходом с инхрониз ацни инте гр атора;

На чертеже предстанле на блок-схема интегратора.

Стохастический интегратор содержит входы 1 интегратора, ренерсивный счетчик 2, группу элементов И 3, элемент 4 запрета, суммирующий счетчик

5, вход б синхронизации интегратора; одноразрядный датчик 7 случайных чисел 35 элемент ИЛИ 8, выход 9 интегратора.

После н ключе ния питания датчик

7 формирует случайную последовательность х с вероятностью появления двоичных символов 0 и 1 н каждом такте P(x)=(x)=0,5, Последовательность х поступает на запрещающий вход элемента 4 и на счетный вход счетчика 5. Нуль последовательности х разрешает прохождение импульса синхронизации СИ с шины б на выход элемента 4 — формируется единичный символ последовательности х Поскольку в счетчике 5 при х--0 не переключается ни один разряд, то остальные последовательности х, х,..., х,„, формируемые на выходах счетчика 5, имеют нулевые значения.

Таким образом, единичные значения последовательности с вероятностью

P(х„)=P(х)= 1=Р(х)=0,5=2 поступают на вход элемента 3 .

Единица послеДовательности х запрещает прохождение синхроимпульса на выход элемента 4 — формируется нулевой символ последовательности х„.

При этом единица, поступающая на счетный вход счетчика 5 вызывает в последнем переключении в единичное состояние лишь одного из разрядов, например, (m †. i + 1)-ого (i=1,m-l).

Переключение (m †i)-ого разряда из нуля н единицу воспринимается импульсным входом элемента 3; как единица последовательности х„ . Таким образом,; последовательности х,, х,..., х на импульсных входах элементов И образуют последовательности несовместимых событий, т.е. в данном такте единица появляется только лишь в одной из последовательностей. Вероятность появлений единицы в последовательностях х, x,... х с учетом

P(x) =2," равной соответственно

Р(Х, ) = Р(х). 2 4 2 2

Р (Х j=P(x) 2 =2

Р(Х )-P(yg.Р С""-л)„1

Перед началом процесса интегрирования н реверсивный счетчик 2 заносится начальное значение интеграла уо (в частном случае равное нулю) .

В пРоцессе интегрирования на вход

1 реверсивного счетчика 2 поступают стохастические последовательности положительных или отрицательных приращений интеграла+аУ . Поступающие приращения интеграла фиксируются реверсивным счетчиком 2, преобразующим интегральные стохастические последовательности+дУ в дноичный код текущего значения интеграла у,которое в процессе интегрирования преобразуется в стохастическую последовательность приращений а Z с помощью датчика 7, элемента 4, счетчика 5, элементов И

3 и элемента 8. Выходная последовательность приращений д Z представляе

744607

10 с бой интеграл от в хбдной последов ательности A Y .

Преобразование интеграла Y в стохастическую последовательность приращений осуществляется следующим образом.

Последовательности х,, x,,...., х „, с вероятностями Р(х )=-2 ", Р(х )=2, - ГТ л 2

Р (х,„) =2 опрашивают соответственно разряды Y Y ..., Y ñ÷åò÷èка 2. На выходах элементов И

3„, 3,..., 3 формируются стохастические последовательности

Z„= Y„x„, Е, — Y х,..., Z = Y х с вероятностями

P(Z„)= У 2 р(2. )= У 2 р(=ч -

Указанное формирование последовательности Z; (i=1,m) заключается в пропускании на выход элемента 3; символов последовательности х; в тактах, в которых Y; = 1. В тактах, когда Y; = О, символы последовательности х; на выход элемента 3; не пропускаются, т.е. в последовательности Z; в эти такты формируются нулиНоскольку последовательности

x x,..., х являются несовместными, то несовместными являются последовательности Z, Z 2 и, следовательно, на элементе ИЛИ 8 осуществляется сложение указанных по следовательностей с полным суммированием вероятностей. () =л l =- ( т. е. выходная последовательность имеет математическое ожидание (вероятность) появления единицы в каждом такте, в точности равное текущему значению интеграла без дополнительных масштабных множителей.

В предлагаемом стохастическом инте граторе математическое ожидание (вероятность) появления единицы в выходной стохастичес кой последовательности равно текущему значению интеграла. Это означает равенство весов входной и выходной стохастическ и х последов ательностей, что при реализации сложных математических зависимостей позволяет исключить блоки выравнивания весов стохастических последовательностей и приводит к уменьшению аппаратурных затрат при решении сложных математических зависимостей, систем уравнений и т.п. Дополнительное уменьшение

55 оборудования в предлагаемом интеграторе происходит от -замены дж .Tà— точно сложного счетного тригге; а суммирующего счетчика более прсстым элементом запрета. Кроме того, oòcóò=.òâèå эффекта увеличения веса импульса выходной последовательности (отсутствие эффекта прореживания ) в предлагаемом интеrpаторе обеспечивает снижение дисперсии этой последовательности в два раза, а погрешности случайного отклонения стохастического представления — в /2 раз по сравнению с дисперсией и погрешностью известного интегратора.

Формула изобретения

Стохастический интегратор, содержащий реверсивный счетчик, суммирующий счетчик, одноразрядный датчик случайных чисел, группу элементов И и элемент ИЛИ,выход которого является выходом интегратора, входами интегратора являются входы реверсивного счетчика, выходы элементов И подключены Ко входам элемента ИЛИ, выход одноразрядного датчика случайных чисел соединен со входом суммирующего счетчика, выходы которого подключены к импульсным входам соответствующих элементов И, соединенных своими потенциальными входами с выходами (m — 1) младших разрядов реверсивного счетчика, о тл и ч а ю шийся тем, что, с целью повышения точности и упрощения интегратора, он дополнительно сОдержит элемент запрета, выход которого подключен к импульсному входу элемента И, соединенного своим потенциальным входом с выходом старшего разряда реверсивного счетчика, запрещающий вход элемен-. та запрета соединен с выходом одноразрядного датчика случайных чисел, а прямой вход элемента запрета является входом синхронизации интегратора.

Источники информации, принятые во внимание при экспертизе

1. Яковлев В.В.„ Федоров P Ô.

Стохастические вычислительные машины. Л., 1974 с. 148 — 150.

2. Авторское свидетельство СССР

Р 491139, кл. G 06 Т 1/02, 1975.

3. Авторское свидетельство CCCP

М 344458, кл. G 06 F 15/36, 1972 (прототип).

744607 мЕ

Составитель О. Майоров

Редактор В. Романенко Техред A. Щепанская

Корректор Г. Назарова

Заказ 3795/14 Тираж 751

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4