Время-импульсное устройство для умножения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ С ИТВЛЬСТВУ

Союз Соватскнх

Соцналнстнческнк

Рес убпнк

< |т744625 (61) Дополнительное к авт. санд-вам (22) Заявлено 061277 (21) 2552663/28-24 (51)М. Кл. с присоединением заявки Hо (23) Приоритет—

G 06 G 7/161

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 300680. Бюллетень ¹ 24

Дата опубликования описания 30.06.80 (53) УДК 681,335 (088.8) (72) Авторы изобретения (71) Заявитель (54) ВРЕМЯ-ИМПУЛЬСНОЕ УСТРОПСТВО

ДЛЯ УМНОЖЕНИЯ.вход которого соединен через первый ключ с первым входом устройства и через второй ключ с выходом блока запоминания, третий ключ, управляющие входы блока запоминания первого, второго и третьего ключей связаны с выходом хронизатора, первый вход которого соединен со вторым входом устройства, содержит дополнительный блок запоминания н пороговый блок, причем выход порогового блока соединен cD вторым входом хронизатора, а выход интегратора — с основным блоком запоминания и через последовательно соединенные дополнительный блок запоминания и третий ключ .со входом интегратора, управляющий вход дополнительного блока запоминания подключен к выходу хронизатора.

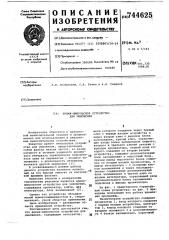

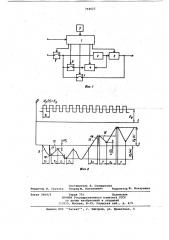

На фиг. 1 представлена структурная схема устройства; на фиг. 2 приведены поясняющие его работу времен-. ные диаграммы.

25 Множительное устройство содержит хронизатор 1, вход которого соединен с первым входом устройства, интегратор 2, выход которого соединен со входами основного 3 и дополнительного. го 4 блоков запоминания, пороговый

Изобретение относится к аналоговой вычислительной технике и предназ- начено для использования в аналоговых вычислительных устройствах.

Известно время- импульсное устройство для умножения, представляющее собой фильтр низких частот, ко входу которого в течение заданного временного интервала периодически подключается одна из переменгых — входное напряжение; а длительность интервала является другой перменной (1).

В установившемся режиме работы данного устройства величина пульсаций на его выходе зависит от постоянной времени фильтра.

Наиболее близким к изобретению техническим решением является времяимпульсное устройство для умножения, содержащее хронизатор, ключи, два интегратора, блок запоминания (2) .

Однако это устройство обладает малой помехозащищенностью и, следовательно, узкой областью применения.

Цель изобретения — расширение области применения устройства.

Поставленная цель достигается тем, что время-импульсное устройство для умножения, содержащее интегратор, I

А. Е. Волынский, С.A. Рачин и A.À. Смирнов

744625 блок 5, вход которого связан с источником помехи, а выход подключен к дополнительному входу хрониэатора

1. Вход интегратора 2 связан через первый ключ б,со вторым входом устройства, а через второй 7 и третий 8 ключи — с выходами блоков 3 и 4 соответственно.

Умножение переменных tg u Е осуществляется в два такта. В начале первого такта, состоящего из m циклов, временные метки с периодом следования, равным периоду помехи U (t) формируется на выходе порогового блока 5,и полученное значение периода

Тоэапомиаается хронизатором.

Далее в течение интервала, длительность которого Т -KT К-1,2,... задается хрониэатором, вход интегратора 2 подключается ко второму входу . устройства через замкнутый ключ 6 и на вход данного блока поступает ис- 20 каженный аддитивной помехой сигнал

Е„, вызывая соответствующее изменение напряжения на его выходе (на диаграмме эта часть кривой обозначена

9) . По окончании данного интервала первый ключ 6 размыкается и на вход синхронизации дополнительйого блока 4 запоминания подается команда на запоминание выходного напряжения интегратора 2.

30 г т

, Т (Е + U„(t) )dt=- E„ так как Т,(= КТ,, На диаграмме соответствующие этому интервалу у астки кривых для ин- 35 тегратора 2 и блока 4 запоминания обозначены 10 и 11. В течение оставшейся час и перво го цикла, длительность которой также равна Т4, вход нтегратора 2 через 40 замкнутйй ключ 8 подключается к выходу блока 4 запоминания (на диаграмме — 12) . По окончании данного интервала третий ключ 8 размыкается, значение напряжения на выходе интегратора 2 равно ошибке, накопленной уст- 45 ройством в течение. первого цикла

h,U = - E .— 11- — 1 и является поТ„Г Т1ч

v e1 .с1 правкой к ре э ультатам интегрировани я в последующих m-1 циклах первого так- 50 та, Так как фактическая постоянная времени интегрирования .с = Т, то напряжение на выходе блока 4 запоминания к концу первого такта

„ - =- „1 - l — 1 1-.-, Т4

В начале второго такта, состоящего из и циклов, вход интегратора 2 через замкнутый третий ключ 8 подключается к выходу блока 4 запоминания 40 и выходное йапряжение последнего в течение интервала t„, интегрируется интегратором 2 с носледующим.запоминанием в блоке 3 запоминания (на диаграмме 13 и 14) в течение остав- 6 шейся части первого цикла данного такта, длительность которой Т выбрана равной нбминальной постоянной времени интегрирования и задается хроннэатором. Вход блока 2 через замкнутый второй ключ 7 подлкючен к выходу блока 3 (на диаграмме изменение выходного напряжения блока 2 в течение этого интервала обозначено 15).

По окончании данного цикла второй ключ 7 размыкается и значение выходного напряжения U = Е.t.l- (1- ) I t1 )

Аналогично предыдущему можно показать, что к концу второго такта напряжение йа выходе блока 3 запоминания

О1 фЕ„((<- ) ((1--) ) "=E т.е. является произведением двух переменных.

Но в отличие от прототипа, результат умножения перменных. „ и Е не искажается аддитивной относительно Еу периодической помехой, т.е. по сравнению с прототипом предлагаемое устройство обладает лучшей помехозащищенностью.

Таким образом, введение новых элементов — порогового блока и блока запоминания выгодно отличает предлагаемое устройство от прототипа, так как при этом увеличивается помехозащищенность, а, следовательно, расширяется область прменения устройства.

Формула изобретения

Время-импульсное устройство для умножения, содержащее интегратор, вход которого соединен через первый ключ с первым входом устройства и через второй ключ с выходом блока запоминания, третий ключ, управляющие входы блока запоминания первого, второго и третьего ключей соединены с выходом хронизатора, первый вход которого соединен со вторым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения, оно содержит дополнительный блок запоминания и пороговый блок, причем выход порогового блока соеди.нен со вторым входом хронизатора, а выход интегратора соединен с основным блоком запоминания и через последовательно соединенные дополнительный блок запоминания и третий ключ со входом интегратора, управляющий вход дополнительного блока запоминания соединен с выходом хронизатора.

Источники информации, принятые во внимание при экспертизе

1. Кори Г., Кори Т. Электронные моделирующие устройства. h1., Мир

1955, с. 247.

2, Авторское свидетельство СССР ,ю заявке Р 2449770/18-24, кл. а 06 G 7/161, 1977 (прототип).

744625

Тирам 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и отнрытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3664/5

Филиал ППП Патент, r. Увгород, ул. Проектная, 4

Составитель Л. Снимщикова

Редактор И. Грузова Техред Ж. Кастелевйч Корректор Ю. Макаренко