Аналоговое делительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ВТЕЛЬСТВУ

Союз Советских

Социалистических

Республик о11744626 (61) Дополнительное к авт. свид-ву (22) Заявлено 060278 (21) 2577959/18-24 (53)М. Кл.2

G 06 G 7/16 с присоединением заявки №

Государственный комитет

СССР

Ilo яеяам изобретений н открытий (23) Приоритет—

Опубликовано 3006.80 Бюллетень ¹ 24 (S3) УДК 681. 335 (088. 8) Дата опубликования описания 300680(72) Авторы изобретения

A.È. Фесенко и Е.И. Глинкин

P1) Заявитель

Тамбовский институт химического машиностроения (54) АНАЛОГОВОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области, электрических вычислительных устройств и может быть использовано в аналоговых вычислительных машинах.

Однако из известных устройств для деления содержит блок сравнения, регистр памяти, блок управления (l j .

Это устройство обладает сравнительно низким быстродействием.

Из известных устройств аналогичного назначения наиболее близким к предложенному является аналоговое дели.тельное устройство, содержащее.соединенные последовательно основной гене ратор экспоненциального напряжения, иэ блок сравнения, триггер, вход основного генератора экспоненциального напряжения подключен к источнику напря1 жения-делителя, второй вход блока сравнения присоединен к источнику на- 0 пряжения-делимого, дополнительный ге нератор экспоненциального напряжения, ко входу которого подключен источник опорного напряжения, ключевой элемент регистр памяти (2).

Это устройство характеризуется низкиМ быстродейетвием вследствие получения результатов деления с частотой, определяемой внешним запуском.у) Целью изобретения является повышение быстродействия.

Для достижения ук аз анной цели в предлагаемое делительное устройство введены дифференциатор импульсов, первый и второй блоки задержки, входы которых соединены с выходом дифференциатора импульсов и управляющим входом ключевого элемента, выход первого блока задержки подключен к входам запуска основного и дополнительного генераторов экспоненциального напряжения и второму входу триггера, выход которого соединен со входом дифференциатора импульсов, выход второго блока задержки присоединен к входам установки в исходное состоя- ние основного и дополнительного генераторов экспоненциального напряжения.

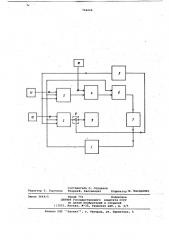

На чертеже показана функциональная схема предложенного устройства.

Оно содержит первый блок задержки 1, основной и дополнительный генераторы экспоненциального напряжения 2 и 3, блок сравнения 4, второй блок задержки 5, триггер 6, дифференциатор импульсов 7, ключевой элемент

8, регистр памяти 9, источник напря744626 агония-делимого 10, источник напряжения-делителя ll и источник опорного напряжения 12.

Устройство работает следующим обРазОме

Импульсом с выхода первого блока задержки 1 запускаются основной и дополнительный генераторы экспоненциального напряжения 2 и 3, и переключайтся в исходное состояние триггер 6.

Сигнал источника напряжения-делимого 10 подается на блок сравнения 4, сигнал источника напряжения-делителя

11 подается на основной генератор экспоненциального напряжения 2, сигнал источника опорного напряжения 12 поступает на дополнительный генератор экспоненциального напряжения 3.

В момент равенства выходного напряжения основного генератора экспонен циального напряжения 2 и сигнала источника напряжения-делимого 10 блок сравнения 4 формирует импульс, переключающий триггер 6.

Длительность импульса на выходе триггера б пропорциональна логарифму отношения сигналов источника напряжения-делимого 10 и источника напряжения-делителя 11. Одновременно выходное напряжение дополнительного генератора экспоненциального напряжения 3 через ключевой элемент 8 поступает в регистр памяти 9. Ключевой элемент 8 управляется выходным сигналом дифференциатора импульсов 7.

В свою очередь выходной сигнал дифференциатора импульсов 7 формируется в момент переключения триггера б (в момент срабатывания блока сравнения 4).

При срабатывании ключевого элемента 8 в регистр памяти 9 поступает выходное напряжение дополнительного генератора экспоненциального напряжения 3, пропорциональное произведению величины напряжения источника опорного напряжения 12 на отношение величин напряжений источника напряжения-делимого 10 и источника напряжения-делителя 11.

Выходной сигнал дифференциатора импульсов 7 через первый и второй блоки задержки 1 и 5 поступает на входы запуска основного и дополнительного генераторов экспоненциального напряжения 2 и 3. Время задержки первого блока задержки 1 выбирается больше времени задержки второго блока задержки 5. Выходной сигнал второго блока задержки 5 устанавливает s исходное состояние основной и дополнительный генераторы экспоненциального напряжения 2 и 3.

В последующий момент времени выходной сигйал первого блока задержки 1 вновь запускает основной и дополнительный генераторы экспоненциального напряжения 2 и 3 и пере- . ключает в исходное состояние триггер 6. 1аким образом,. описанный цикл работы устройства повторяется. Информация в регистре памяти 9 изменяется только после срабатывания ключевого элемента 8.

Укаэанные выше конструктивные от1 личия позволили повысить быстродействие -устройства, так как частота получения информации на выходе (в регистре памяти 9) определяется только значениями напряжений делимого и делителя.

Формула изобретения

Аналоговое делительное устройство, содержащее соединенные последовательно основной генератор экспоненциального напряжения, блок сравнения, триггер, вход основного генератора экспоненциального напряжения подключен к источнику напряжения-делителя, ко входу блока сравнения присоединен источник напряжения-делимого, дополнительный генератор экспоненциального напряжения, ко входу которого подключен источник опорного напряжения, ключевой элемент, регистр памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены дифференциатор импульсов, первый и второй блоки задержки, входы которых соединены соответственно с выходом дифференциатора импульсов и управляющим входом ключевого элемента, выход первого блока задержки подключен к входам запуска основного и дополнительного генераторов экспоненциального напряжения и первому входу триггера, выход которого соединен со входом дифференциатора импульсов, выход второго блока задержки присоединен к входам установки в исходное состояние основного и дополнительного генераторов экспоненциального напряжения.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 608170, кл. G 06 G 7/16, 1977.

2. Авторское свидетельство СССР

9 547780,. кл. G 06 G 7/16, 1975 (прототип).

744626

Составитель О. Отраднов

Редактор Т. Горячева ТехредЖ. Кастелевич

Корректор Ю. Макаренко

Заказ 3664/5

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб. д. 4/5

Филиал ППП Патент, г. ужгород, ул. Проектная, 4