Устройство для решения систем логических уравнений

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ИТВЛЬСТВУ

Союз Советских

Социалистических

Республик р>744644

1 (61) Дополнительное к авт. свид-ву (22) Заявлено 050178 (21) 2567969/18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 300680. Бюллетень №24

Дата опубликования описания 3006.80 (5 )ф . Кл.2

G 06 G 7/48

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.335 (088.8) (72} Авторы изобретения

Б.А.Борконский, A.Ô.Êàòêîâ и В.П.Романцон

Институт электродинамики AH Украинской CCP (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ

ЛОГИЧЕСКИХ УРАВНЕНИИ

ЗО

Изобретение относится к вычислительной технике и. предназначено для использования в нычислительных системах различного назначения, в частности при исследовании работы конечных антоматов при заданных огра- ничениях.

Известны устройства для моделирования логических функций, используемые при построении логических автома- >О тов. Эти устройства состоят из логических элементов, соединенных между— собой в соответствии с моделируемой функцией, и применяются для нахождения значений логической функции 15 при заданных значениях логических переменных,т.е. при решении прямых задач (1).

Недостаток известного устройства состоит в невозможности решения обрат-2О ных и смешанных задач.

Наиболее близким по технической сущности к предлагаемому является устройство для решения систем логических уравнений, содержащее регист- 25 ры, блоки задания логических функций, сумматоры по модулю два (2), Недостаток известного устройстна заключается в невозможности решения обратных и смешанных задач.

Цель изобретения — расширение класса решаемых задач эа счет возможМости решения обратных и смешанных задач.

Поставленная цель достигается тем, что в уСтройство для решения . систем логических уравнений, содержащее и каналов, каждый из которых содержит блок задания логических функций, выход которого соединен с первым входом сумматора по модулю два,-второй вход которого подключен к шине истинного значения логической переменной, третий вход сумматора по модулю два соединен с шиной истинного" зйачения лбгической функции, в каждый канал дополнительно введены первый, второй, третий и четвертый элементы НЕ, первый, второй, третий и четвертый делители напряжения, первый, второй, третий и четвертый переключатели, причем в каждом канале выход блока задания логических функций соединен со входом первого элемента НЕ, выход которого подключен ко входу первого переключателя, выход которого через второй элемент НЕ соединен со входом второго переключателя, выход которого соединен со вторым входом сумматора

744644

1 ника 6. Заданные значения логических функций и переменных с помощью эле- ментов НЕ 3 и переключателей 4 rIpeобразуются в истинные значения и подаются на входы сумматоров 1 по модулю два и блоков 2 задания логических функций соответственно. В результате введенной информации на входах сумматоров 1 по модулю два возникает противоречивая комбинация кодов.

Схема выходит иэ устойчивого состояния и, находится в переходном режиме

1 пока сумматоры 1 по модулю два не отработают на своих выходах такие значения, которые удовлетворяют системе (а) .

5 Предлагаемое устройство, благодаря наличию новых элементов и связей между ними, позволяет решать прямую, обратную и смешанные зацачи.

Формула изобретения

3 по модулю двау выход которого через третий элемент НЕ подключен ко входу третьего переключателя, выход которого соединен со входом четвертого элемента РЕ, выход которого подключен xg.входу четвертого переключатеЛя, выходы переключателей всех каналов соединены с шинами инверсного значения логических функций!

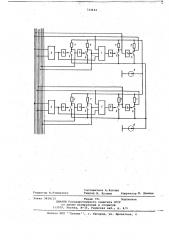

На чертеже схематически представлено предлагаемое устройство.

Устройство содержит. трехвходовые сумматоры 1 по модулю два, блоки 2 задания логических функций, элементы

НЕ 3, переключатели 4, источники 5 и 6 напряжения делители 7 напряжения.

Все пары шин истинных и инверсных 1 значений логических переменных и функций устройства служат входными или выходными беэ какой-либо перестройки.

Устройство работает следующим образом. 20

В исходном состбянии устройство находится в равновесии. На тех шинах истинных и инверсных значений логических функций и переменных, которые не соединены с помощью переключателя 4 с источником б напряжения, формируются от источника 5 напряжения, через делители 7 напряжения, равные, например, логической едини° t це . На тех же шинах, которые соединены с источником б напряжения, 30 напряжение равно величине источника б напряжения, соответствующее логи-. ческому нулю . Если устройство находится в равновесии, то на входах сумматоров 1 по модулю два комбинация З5 кодов непротиворечива, т.е. Удовлетворяет системе уравнений ( (х,, х,, ° . °, хп)+y<+

fg (х,, х,.... xn)+yg+ х = хд

Ф ° ° ° ° ° ° Ф ° ° ° Э ° ° ° ° ° ° ° ° ° ° °

Ы„(х, хл, . ° .. ха)+уц+ xn = х» (а).

1 где х, х,...., х — значения логи2 и ческих переменных; у„, у,...., у„ — значения логических функций;

Й (х«х2 ã °, x ) ° °

Й (х х, i х ) - лОГические функции, моделируемые блоками

2 моделйрованйя логических функций. 50

На соответствующих парах шин, которые при решении конкретной задачи являются входными, задают значения известных переменных и функций в ви де истинных значений и их отрицаний, 55 прйчем значения задаваемых логических единиц подтверждаются устройством в конце переходного процесса, так как они формируются на всех шинах с помощью источйика 5 напряжения и делителей 7 найряжения, а значения логических нулей задают от источника 6 напряжения с величиной напряжения, равной напряжению источУстройство для решения систем логических уравнений, содержащее и каналов, каждый из которых содержит блок задания логических функций, выход которого соединен с первым входом сумматора по модулю два, второй вход которого подключен к шине истинного значения логической переменной, третий вход сумматора по модулю два соединен с шиной истинного значения логической функции, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет возможности решения обратных и смешанных задач, в каждый канал дополнительно введены первый, второй, третий и четвертый элементы НЕ, первый, второй, третий и четвертый делители напряжения, первый, второй, третий и четвертый переключатели, причем в каждом канале выход блока задания логических функций соединен со входом первого элемента НЕ, выход которого подключен ко входу первого переключателя, выход которого через второй элемент НЕ соединен с входом второго переключателя, выход которого соединен со вторым входом сумматора по модулю два, выход которого через третий элемент НЕ подключен ко входу третьего переключателя, выход которого соединен со входом четвертого элемента НЕ, выход которого подключен ко входу четвертого переключателя, выходы переключателей всех каналов соедйнены с шинами инверсного значения логических функций.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии Р 48-4105, кл . G 06 F 15/00, опублик. 1973.

2. Авторское свидетельство СССР

9486331, кл. G 06 G 7/48, опублик.

1975.

744644

Составитель A.Колчин техред N. Кузьма Корректор И. Демчик

Редактор В.Романенко

Заказ 3818/15 Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Иосква, Ж-35, Раушская наб. д. 4/5

Филиал ППП Патент, r. Ужгород, ул . Проектная, 4