Вычислитель статических моментов

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалнстическив

Рес ублин

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИ ЕТЕЛЬСТВУ

<и>744646 (б1) Дополнительное к авт. свид-ву (22) Заявлено 161277 (21) 2556264/18 24 (51)М. Кл.2 с присоединением заявки М

G 06 G 7/52

Государствеииый комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 30.06.80. Бюллетень Hо 24 (53) УДК 681. 3 (08 8. 8) Дата опубликования описания 30.06.80 (72) Авторы изобретения

A.Ã. Струнин, В.И. Губарь и В.С. Мирошниченко

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (71) Заявитель (54) ВЫЧИСЛИТЕЛЬ СТАТИСТИЧЕСКИХ МОМЕНТОВ

Изобретение относится к области вычислительной техники и может быть использовано для оценки числовых характеристик совокупности стационарных и нестационарных случайных процессов с высокой точностью.

Известен вычислитель статистических моментов (1), который содержит блок модуляции, широтно-импульсный модулятор, элемент И, счетчики, дешифратор, блок элементов памяти, частотно-импульсный модулятор, блок ключей, генератор прямоугольных импульсов, одновибратор, элементы НЕ, переключатель.

К недостаткам вычислителя следует отнести его аппаратурную сложность.

Наиболее близким к изобретению по технической сущности является вычислитель статистических моментов (2), содержащий автоматический регулятор масштаба, первый выход которого подключен к управляющему входу масштабного усилителя, информационным вхо- 25 дом соединенного с выходом сумматора, входы которого являются входами вычислителя, второй выход автоматического регулятора масштаба через блок запрета подключен к управляющему вхо- З0 ду усредняющего усилителя, информационный вход которого соединен с выходом антилогарифмического усилителя, вход автоматического регулятора масштаба подключен ко второму выходу второй,из к последовательно соединенных дифференцирующих цепочек. Основным-источником погрешности такого вычислителя является аналоговый нелинейный блок — антилогарифмический усилитель, адцитивная погрешность которого полностью входит в результат вычисления моментов высоких порядков.

Цель настоящего изобретения — повышение точности вычисления многомерных статистических.моментов.

Поставленная цель достигается тем, что s вычислитель статистических моментов введены запоминающий элемент, два переключателя, блок логарифмирования, квадратор и блок деления. При этом выход масштабного усилителя подключен к одному входу переключателя, другой вход которого соединен с выходом блока логарифмирования, вход которого объединен со входом квадратора и подключен к выходу запоминающего элемента. Вход запоминающего элемента соединен с одним выходом

744646 второго переключателя, вход которогс

* пбдклйчен к выходу усредняющего усилителя; другой выход переключателя соединен d первым входом блока деления, второй вход которого подключен к выходу квадратора. Выход блока деления соединен со входом первой иэ

К последовательно соединенных диф ференцирующих цепочек, а выход пер- вого переключателя подключен ко входу антилогарифмического усилителя.

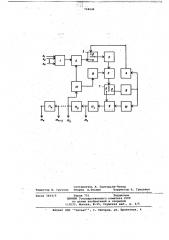

На чертеже представлена блок- схема вычислителя статистических моментов.

Вычислитель статистических моментов содержит сумматор 1, масштабный усилитель 2, первый переключатель 3, блок 4 логарифмирования, усредняющий усилитель 5, антилогарифмический усилитель б, второй переключатель 7, запоминающий элемент 8, блок 9 деления, квадратор 10, последовательно соединенные дифференцирующие цепочки

11 -11к, автоматический регулятор

12 масштаба, блок 13 запрета. Выходы дифференцирующих цепочек являются вы ходами устройства.

Вычислитель статистических моменI тов работает в два такта. В йервый такт переключатели 3 и 7 находятся в положении а, а на входы сумматора 1 поступают сигналы х,х,...,х„,, сумма которых у, проходя через масштабный усилитель 2, антилогарифмический усилитель 5 принимает значение многомерной производящей функции моментов

Я (у, t) = ехр(у(1+О) (1+ ) ), Эта величина фиксируется на выходе запоминающего элемента 8 и поступает через блок логарифмирования на вход б переключателя 3 и через квадратор

l0 на один выход блока 9 деления.

Во втором такте переключатели 3 и 7 переводятся в положение б. В результате сигнал с выхода блока 4 поступает через антилогарифмический усилитель 6, усредняющий усилитель. 5 на второй вход блока 9 деления, на выхОде которого образуется величина

s""(v,t ) =exnjv(2(<+d)(<+q)-(+ a) + Я =

-е юг -(+61- Ю(1 +2 +ф )=е р у(ЬЬ» ) (Д (М/ ) 1.=. (» б ) с помощью последовательно включенных дифференцирующих цепочек 11„-11, .

Для расширения динамического диапазона в устройстве есть автоматический регулятор 12 масштаба, поддерживающий величину на входе айтилогарифмического усилителя б в Малом диапазоне, а для ускорения процесса измерения использован блок 13 запрета, предназначенная для исключения переходного процесса. Выходы дифференцирующих цепочек являются выходами устройства.

Предлагаемый вычислитель статистических момейтов в отличие от известного имеет резко сниженную погрешность измерения d " моментов вык соких порядков, что позволит применить простые нелинейные преобразователи, обладающие большой погрешностью при построении измерителей статистических моментов, и в то же время получить результат измерения с высокой точностью и устранит тем самым необходимость разработки высокоточных аналоговых нелинейных преобразователей для измерителей многомерных моментов высоких порядков, обладающих высокими метрологическими характеристиками, 5 !

О

Формула изобретения кл, G 06 F 15/36, 1977 (прототип).

Вычислитель статистических моментов, содержащий автоматический регулятор масштаба, первый выход которого подключен к управляющему входу масштабного усилителя, информационный вход которого соединен с выходом сумматора, входы которого являются входами вычислителя, второй выход ав томатического регулятора масштаба через блок запрета подключен к управляющему входу усредняющего усилителя, информационный вход которого соединен с выходом антилогарифмического усилителя, вход автоматического регулятора масштаба подключен к выходу второй иэ к последовательно соединенных дифференцирующих цепочек, отличающийся тем, что, с целью повышения точности, в него введены запоминающий элемент, два переключателя, блок логарифмирова40,ния, квадратор и блок деления, при. этом выход масштабного усилителя подключен к одному входу переключателя, другой вход которого соединен с вы- . ходом блока логарифмирования, вход

4 которого объединен со входом квадратора и подключен к выходу запоминающего элемента, вход запоминающего элемента соединен с одним выходом второго переключателя, вход которого подключен к выходу усредняющего усилителя, другой выход переключателя соединен с первым входом блока деления, второй вход которого подключен к выходу квадратора, выход блока деления соединен со входом первой из к последовательно соединенных дифференцирующих цепочек, а выход первого переключателя подключен ко входу антилогарифмического усилителя.

Источники информации, щ принятые во внимание при экспертизе

1, Авторское свидетельство СССР

Р 475625, кл. 6 06 Р 15/36, 1973.

2. Авторское свидетельство СССР по заявке Р 2448540/18-24, 744646 тк 1 -2 g

Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Заказ 3664/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель Л. Григорьян-Чтенц

Редактор И. Грузова Техред Л.Теслюк Корректор А ° Гриценко с