Матричное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз С нет:кмк

Социалистм чеснку

Республик 11,744 724 (61) Дополнительное к авт. свид-ву— (22) Заявлено 14.09.77 (21) 2526181/18-24 с присоединением заявки №вЂ” (23) Приоритет—

{51) М. Кл.

Сг 11 С 11/40

Гооударстеениый комитет (53) УДК 681.32?..66 (088.8) Опубликовано 30 06.80. Бюллетень № 24

Дата опубликования описания 05.07.80 до делам изобретений н открытий

А. С. Березин, Е. М. Онищенко, В. И. Кимарский, Ю. И. Кузовлев и А. С. Федонин (72) Авторы изобретения (71) Заявитель (54) МАТРИЧНОЕ ЗАПОМИНАЮЩЕЕ YCTPOFfCTBO. Изобретение относится к полупроводниковым запоминающим устройствам.

Известна .матрица элементов памяти, выполненная на основе инжекционного элемента памяти.

Известный элемент памяти содержит бистабильную ячейку, образованную двумя п-р-п транзисторами и двухколлекторным р-и-р транзистором. Для записи-считывания информации служат дополнительные (вторые) коллекторы и-р-и транзисторов, подключенные к разрядным шинам 111. 1о

Недостатком матрицы, выполненной на основе описанного элемента памяти, является необходимость введения изоляции между отдельными строками матрицы, что связано с недопустимостью электрической связи между ними и что значительно усложняет г5 технологию изготовления больших интегральных схем памяти, содержащей эту матрицу.

Известна также матрица инжекционных элементов памяти, которая может бъггь из- . готовлена без изоляции отдельных строк или щ рядов. (2).

Однако базовый элемент памяти данной матрицы содержит большое число дополнительных логических инжекционных вентилей

2 для выборки элемента памяти в матрице и для управления им при запгки и считывании информации. Это существенно увеличивает плошадь элементов. памяти и матрицы в целом и снижает ее быстродействие при считывании и записи.

Наиболее близким техническим ренгением . являетея. полупроводниковое интегральное запоминающее устройство, содержащее элементы памяти, адресные шины и разрядные . шины записи и считывания. Каждый элемент памяти содержит бистабильную ячейку, образованную первым и вторым и р-п транзисторами с перехрестно связанными базами и коллекторами и двухколлекторным третьим транзистором р-п-р типа. Первый транзистор и-р-и типа имеет дополнительный коллектор для считывания информации.

Эмиттер третьего р- и-р транзистора подключен к словарной шине, а коллекторы —. к базам первого и второго транзисторов соответственно. Для записи информации служат четвертый и пятый транзнсгоры р-п-р типа, эмиттеры которых подклк1чены к разрядным шинам, а коллекторы к базам не рного и второго транзисторов. 11ятый 1 - н- р транзисторр имеет дополнительный кол,ц K10(>, со744724

3 единенный со вторым коллектором первого п-р-п транзистора. К этой же точке подключен коллектор шестого п-р-п транзистора, база которого подключена к словарной шине.

Точка объедйпения коллекторов подсоединена к базе выходного седьмого и-р-п транзистора считывания, коллектор tcogoporo подключен к разрядной шине считывания. Базы всех р-п-р транзисторов и эмиттеры всех и-р-и транзисторов соединены с общей точкой. В режиме хранения все р-и-р транзисторы элемента памяти открыты и бистабильная ячейка находится в одном иэ двух устойчивых состояний..Выборка строки матрицы производится снижением потенциала адресной шины и выключением третьего тран- . зистора. При записи, одновременно с сиг-., налом выборки, выключается один из р-п-р транзисторов записи, а считывание осуществ- ляется при подаче сигнала выборки. При этом закрывается шестой п-р-п транзистор и снимается запрещающий сигнал с базы содержит бистабильную ячейку, образован26 ную, например, п-р-и транзисторами 3 и 4; и р-п-р транзистором 5. Цепи записи элемента 2 памяти образованы, например, р-п-р транзисторами 6 и 7.

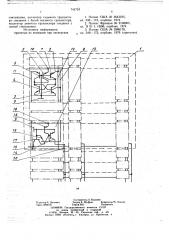

База и коллектор транзистора 4 соединены соответственно с одним из коллекто-. ров и базой транзистора 3, второй коллектор транзистора 3 соединей с информационной шиной 8. Первый и второй коллекторы р-п-р транзистора 5 соединены соответственно с коллекторами п-р-и транзисторов 3 и 4 и з!! р-и-р транзисторов 7 и 6. Базы р-и-р транзисторов 5, 6, 7 и эмиттеры п-р-п транзисторов 3 и 4 соединенй вместе и подключены к шине 9 нулевого потенциала. Эмиттер р-п-р транзистора 5 подключен к адресной шине 10, а эмиттеры р-п-р транзисторов

6 и 7 подключены соответственно к разряд- ным шинам 1 и 12. Элементы 2 памяти каждого столбца одной группы 1 подключены к усилителю. 13 считывания, состоящему, например, иэ и-р-п транзисторов 14 и 15 и р-и-р транзисторов 16 и 17, причем

: эмиттеры и-р- п транзисторов 14 и 15 и п-базы р-и-р транзисторов 16 и 17 соединены вместе и подключены к шине 9, эмиттер между элементами 2 памяти, подключенныл мй к шине 10. Коллекторные токи транзистора 5 в первом приближении равны, повыходного транзистора, что приводит к его включению и снижению потенциала разрядной шины считывания.до уровня логического «О», в случае„если элемент памяти хранит его, т. е. если открыт второй п-р-п транзистор.

Недостатками матрицы подобных элементов памяти являются введение для считывания информации двух инверторов на п-р-и транзисторах,,что вызывает заметное возрастание мощности. потребления, невысокое быстродействие при считывании информации, которое объясняется тем, что относительно большая паразитная емкость шины считывания перезаряжается с помощью инвертора на выходном п-р-п транзисторе, базовый ток которого невелик (часть тока хранения).

Цель изобретения — повышение ее бйстродействия при считывании информации и уменьшение рассеиваемой мощности.

Указанная цель достигается тем, что в матричное запоминающее устройство, содержащее группы ячеек памяти, каждая иэ которых выполнена на пяти транзисторах, первый и второй иэ которых соединены rIo триггерной схеме, коллектор третьего и первый коллектор четвертого транзисторов соединены с коллектором первого т!райзистора, второй коллектор четвертого и коллектор пятого транзисторов соединены с коллектором второго транзистора, эмиттеры первого и второго транзисторов соединены с шиной нулевого потенциала и базами четвертого и. пятого транзисторов, эмнттер третьего транэистора соединен с первой разрядной шиной; эмиттер четвертого транзистора подключен к адресной шине, эмиттер пятого транзистора подсоединен ко второй разрядной шине, усилители считывания, каждый из которых выполнен на четырех транзисторах, базы шестого и седьмого из которых подключены к шине нулевого потенциала и эмиттеру восьмого транзистора. эмиттер девятого транзистора соединен с базой шестого транзистора, информационную шину, шину питания, шину разрешения считывания и шину считывания, в нем вторые коллекторы первых транзисторов каждой группы ячеек памяти подключены к информационной шине, к коллектору восьмого, базе девятого и коллектору шестого транзисторов, эмиттер шестого транзистора соединен с шиной питания, эмиттер седьмого транзистора соединен с шиной разрешения считывания, коллектор седьмого транзистора соединен с базой восьмого транзистора, коллектор девятого транзистара соединен с шиной считывания.

На чертеже представлена электрическая схема устройства, Матричное запоминающее устройство разбито на группы ячеек памяти 1, по четыре строки в каждой. группе. Элемент 2 памяти р-п-р транзистора !6 подключен к шине 18 питания, эмиттер р-п-р транзистора 17 подключен к шине 19 разрешения считывания, коллекторы транзисторов 15, 16 и база транзистора 4 соединены вместе и подключены к шине 8, а коллектор транзистора 14 подключен к шине 20 считывания.. Устройство работает следущим образом .

В режиме хранения в адресную шину 10 поступает ток от источника питания (на чертеже не показан), который распределяется этому элемент 2 памяти может находиться в любом состоянии «О» или «1», если коэф744724

5 б фициенты усиления тока транзисторов 3 и" 4 в полувыбрацных элементах 2 памяти, вос(,В(,, /)»»,) превышают единицу. станавливается благодаря запоминанию на

В усилителях 13 считывания (транзис- паразитных емкостях. торы 14, 15, 16, 17) оба р-п-р транзистора 16 и 17 открйты, поэтому и-р-и трап- Достоинствами предлагаемой матрицы явзистор )6 открыт и насыц(ен, а транзистор лиютсЯ, во-пеРвых, меньшал площадь, за14 закрыт. Это приводит к тому, что на ши- нимаемаЯ на кРисталле, посколькУ в ней нах 20 считывания поддерживаются уровни два инвертора (транзисторы) обслУживают логической «i » с помощью внеш(|их схем четыре элемента памЯти; во-втоРых, Умень(на .черт. не показаны). шение потребления мощности в элементах

Выборка строк» в матрице произ.одится памЯти ДополнительнаЯ эко ОМИЯ мощности снижением потенциала шины 10 до уровня to в матРице в Режиме хРанения достигаетсЯ логического «0». благодаря выключенному состоянию транВ. режиме хранения потенциалы разряд- зисторов записи; сокрап(ение вРемени переных шин 11 и 12 записи равны логического заРЯдки паразитной емкости шины считы«()», поэтому транзисторы записи 6 и 7 ваннЯ, так как сама эта емкость ойазывазакрыты, что позволяет умены ить потреб- етсЯ ме (ьц(е в четыРе Раза, а входной ток ление мощности в элементах памяти 2 в ре- инвертора (транз(»стор), осуп1ествляюшего жиме хранения; перезарядку этой емкости, может быть больдля записи. информации, одновременно ше, чем в известном устРойстве. Это обесс импульсом В.,борки в соответствующую пе вает повыше ие быстРодейств Я матриразрядную шину записи, например, в шину цы при считывании. Все элементы матрицы устройства, подается импульс тока, что z выполняются на кристалле без изоляции, приводит к переключению бистабиль((ой ячей- посколькУ базы всех Р-п-Р тРанзистоРов и ки выбранного элемента памяти 2. Это при- эмиттеРы и-Р-и тРанзистоРов подключены к водит к тому, что на шинах считывания 20 поддерживаются уровни логической «1» с помощью внешних схем (на чертеже не показаны). 3s Формула изобретения

Выборка строки в матрице производится снижением потенциала шины 10 до уровня . МатРичное запоминающее Устроиство, сологического «0». держащее группы ячеек памяти, каждая из

В режиме хранения потенциалы на раз- котоРых выполнена на пЯти транзисторах, рядных шинах 11 и 12 равны логической пеРвЫй и втоРой из котоРых соединены по

«Р», поэтому транзисторы 6 и? записи за- триггерно|» схеме, коллектоР тРетьего и перкрыты, что позволяет уменьшить потребле- вый коллектоР четвеРтого тРанзистоРов соение мо(цности в элементах памяти 2 в ре- динены с коллектоРом пеРвого тРанзистоРа, „„„, х н „ия .. втоРой коллектоР четвеРтого и коЛлектор

Для записи информа ии одновременно пнтого тРанзистоРов соединены с коллектос импульсом выборки в соответствующую ç3 Ром втоРого тРанзистоРа, эь»иттеры пеРвого разрядную шину записи, например в шину 11 и втоРого тРанзистоРов соединены с шиной матрицы, подается импульс тока, что Hype улевого потенциала и базами четвеРтого водит к пере лючению бистабильной ячей- и пЯтого тРанзистоРов, эмиттер третьего ки выбранного элемента 2 памяти тРанзистоРа соединен с пеРвой РазРЯдной для считывания информации необходимо шиной, эмиттеР четвеРтого транзистора подв .трех невыбранных строках соответствую- . ключен к адРесной шине, эмиттеР цЯтого щей группы l мат ицы снизить нап яже- тРанзистоРа подсоединен ко втоРой РазРЯдние на шиках 1 и" и этом в вы нн ю ной шине, Усилители считываниЯ, каждый шин 10 ток х анения по-прежнем пост - из котоРых выполнен на четыРех тРанзистопает. Одновременно потенциал шины 1Р раз- Рак, базы шестого и седьмого из котоРых реШения считывания данной группы l сни 4. подключены к шине нулевого потенциала жается до овня логического «(что н и- и эмиттеру восьмого тРанзистоРа; эмиттер жается до уровня логического « О», что нриводит к выключению транзисторов 1? и 15, девЯто о транз"стора соеди"ен с базои шесчто, в свою очередь, снимает «блокировку» того тРанзистоРа, инфоРмационнУю шинУ; инвертора на транзисторах 14 и 16. Состоя- шинУ питаниЯ, шинУ РазРешениЯ считывание транзистора 14 оп еделяе я п н - ниЯ и шинУ считываниЯ, Отличаюи(еРСЯ тем, определяется потенциалом на шине 8 который в свою о е-едь 3о что, с.целью повьп ен"Я бь с Р действиЯ Устопределяется состоянием транзистора 3. уменьшения рассеиваемой мощности, в нем

Следовательно, в зависимости от того, вторые коллекторы первых транзисторов каж. какую информацию хранит элемент 2 памяти дой группы ячеек памяти подключены к инвыбранной строки («!» или «О»), потенциал формационной шине, к коллектору восьмошины 8 соответствует - логическим «1» 33 го, базе девятого и коллектору шестого транили «О». зисторов, эмиттер шестого транзистора сое.После снятия сигналов выборки (или «ан- тивыборки») информация, хранимая ранее динен с шиной питания, эмиттер седьмого транзистора соединен с шиной Разрешения

744724

/2 8 /Я

5 ю 7 2

Составитель А. Воронин

Редактор А. Полиннч Техред К. Шуфрнч Корректор М. Ленчик

Заказ 3824/18 Тирам 682 Подписное.I lEiMHHH Государственного комитета СССР по делам изобретений и открытий

1 3035, Москва, Ж вЂ” 35, Раушсиая наб., д. 415

Филиал ППП «Патент>«г: Ужгород, ул. Проектная, 4 считывании, коллектор седьмого транзистора соединен с базой восьмого транзистора, коллектор девятого транзистора соединен с шиной считывания.

Источники информации, принятые во внимание прн экспертизе

1. Патент СШЛ № 3643235, кл. 340 — 173, опублнк. 1974.

2. Патент Франции № 2138905, кл. Н 01 L !9/ОО, опублик, 1974

3. Патент США № 3986178, кл. 340 — 173, опублнк, 1976 (прототип),