Устройство управления для блоков памяти с разрешением неоднозначности

Иллюстрации

Показать всеРеферат

О П И С А И И Е 744727

ИЗОБРЕТЕНИЯ

Сокзз Советских

Социалистических, Ресттубпик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 02.10.75 (21) 2177516/18-24, с присоединением заявки ¹вЂ” (51) М.К.

G 11 С 15/00

Гесударстееиньй комитет

СССР (23) Приоритет—

Опубликовано 30.06.80. Бюллетень №24 (53) УДК681.326. .7 (088.8) до делам изобретений и открытий

Дата опубликования описания 05.07.80. (72) Автор изобретения

Ю. А. Хаскин (71) Заявитель (54) УСТРОИСТВО УПРАВЛЕНИЯ ДЛЯ БЛОКОВ ПАМЯТИ

С РАЗРЕШЕНИЕМ НЕОДНОЗНАЧНОСТИ.

Изобретение относится к цифровой вычислительной технике и предназначено для использования в буферных или ассоциативных запоминающих устройствах.

Известны схемы управления с разрешением неолнозначности, используемые в ассоциативных и буферных запоминающих устройствах, содержащие триггеры, связанные параллельно ко входу тактовыми сигналами и параллельно-последовательно либо параллельно ко входу цепочками айализа состояния элементов памяти tlj и 12).

Однако такие устройства обладают аппаратурной избыточностью и низким быстродейст вне м.

Наиболее близким по техническому решению к предложенному является устройство, состоящее из триггеров, каЖдый из которых соединен с двумя соответствующими элементами И, причем единичный выход триггера соединен с одним из входов первого элемента И, тактовые входы всех триггеров объединены, входы установки триггеров в единичное состояние являются информационными вхолами устройства, нулевой выход каждого триггера полключен к одному из входов второго элемента И, ко вторым вхо2

1 дам первого и второго элемента И, кроме элементов И, связанных с первым триггером, подключен выход второго элемента И, связанного с соседним триггером, вторые входы элементов И, связанных с первым триггером, объединены и являются трактнруемыми входами, выходы первых элементов И являются выходами устройства 13).

Однако такое устройство облалает низким быстродействием, так как в нем после выработки каждого управляющего сигнала то необходимо произволить повторную запись данных в триггеры.

Цель изобретения — повышение. быстродействия устройства.

Указанная пель достигается тем, что в устройство управления лля блоков памяти с разрешением неоднозначности, содержащее триггеры и элементы И, единичный выход каждого триггера соединен с одним из входов соответствующего элемента И, тактовые вхолы триггеров объединены, а щ входы установки триггеров в единичное састоянке являются информационными входами устройства, дополнительно введены сумматоры по модулю два, причем выход каждого элемента И соединен с соответствую744727

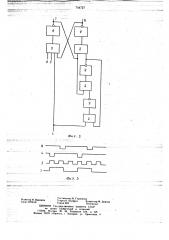

Код на выходах элементов 2 И

Номер тактового !Код, запнсанны!! импульса в триггер I

Код на выходах сумматоров 3

0 !

3

01 1 I t l l

000! 111

00000!

0000001

0000000

010101 1

000!01!

00000 I

000000!

01 00000

00000! 0

000000!

0000000 !цими 1гходами смежных-сучматоров по модулю два и другим входом последую!цего элемента И, выходы сумматоров по модулю два соединены со входами управления соответствующих триггеров, нулевые выходы которых являются выходами устройства.

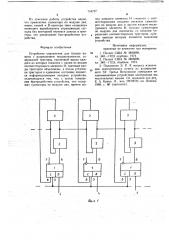

На фиг. 1 показана функциональная схема устройства; на фиг. 2 -- один из вариантов построения В-триггера типа «защелка»; на фиг. 3 — диаграммы, поясняющие работу D-триггера.

Устройство состоит из D-триггеров 1 типа «защелка», элементов 2 И, сумматора 3 по модулю два, входа 4 установки триггеров в единичное состояние, тактовых входов 5 триггеров, входов 6 управления, нулевых выходов 7 триггеров, единичных выходов 8 триггеров.

Устройство работает следущим образом.

Входной информацией для него являются данные о расположении ячеек памяти запоминающего устройства, к которым необходи мо обратиться. Да нные поступают на входы 4 триггеров 1 устройства в виде параллельного кода, логический нуль которого означает наличие, а логическая единица -- отсутствие полезной информации. В начальный момеHT все триггеры 1 установлены в нулевое состояние. На выходах элементов 2 И потенциал соответствует логической единице, потенциалы на входах сумматоров 3 по модулю 2 также соответствуют логической единице. вследствие этогб на выходах сумматоров 3 по модулю 2 потенциал соответствует логическому нулю и триггеры заперты по входу 6 для прохождения тактовых сигналов. При поступлении кода входной информации он записывается в триггеры 1 и устанавливается на их выходах 8. Так как выход каждого элемента 2 И соединен с левым входом соседнего элемента 2 И, то первый (считая слева) потенциал, соответствующий логическому нулю на выходе 8 триггера 1, установит потенциал логического нуля на выходе связанного с ним элемента 2 И и всех элементов 2 И, расположенных справа.

Таким образом, код входной информации, записанный в триггеры 1 и состоящий из произвольно расположенных логических еди4 ниц и нулей, на выходах элементов 2 И преобразуется в код, содержащий одну последовательность логических единиц н одну последовательность логических нулей, причем начало последовательности нулей однозначно соответствует первому слева логическому нулю в коде входной информации.

При этом на выходах Всех, за исключением одного, сумматоров 3 по.модулю 2 устанавливаются потенциалы логического нуля. На входах сумматора 3 ио модулю 2, связан10 ного с триггером 1, который является первым слева из числа триггеров, установленных в единичное состояние, потенциалы неодинаковы и поэтому на выходе данного сумматора 3 по модулю 2 устанавливается потенциал логической единицы.

Поэтому к моменту поступления очередного тактового импульса только один триггер 1, а именно первый слева из числа триггеров 1, установленных в единичное состояние, открыт по входу 6. Тактовый импульс

20 в этот триггер в инверсном виде появляется на выходе 7 в качестве сигнала управления, выдаваемого в запоминающее устройство. По заднему фронту тактового импульса происходит возврат триггера 1 в исходное состояние. К моменту появления следующего тактового импульса открытым по входу 6 окажется уже второй слева триггер 1 из числа тех, в которые первоначально была записана логическая единица. Очередной тактовый импульс пройдет через этот зе триггер 1, по заднему фронту его триггер I закроется по входу 6 и откроется следующий, и так далее до тех пор, пока все триггеры 1, в которые первоначально была записана логическая единица, не вернутся в исходное состояние.

3$

Таким образом, по каждому логическому нулю, содерЖащемуся в коде входной информации и являющемуся признаком необходимости выработки управляющего сигнала, поочередно слева направо устройством

40 вырабатывается по одному управляющему сигналу.

Порядок изменения кодов в триггерах 1, .на выходах элементов 2 И и сумматоров 3 по модулю 2 показан на примере одного из кодов входной информации в таблице.

744727

Из описания работы устройства видно, что применение сумматора по модулю два, новых связей и D-триггера типа «защелка» позволяет вырабатывать управляющие сигналы без повторной переписи данных в триггеры, что увеличивает быстродействие устройства.

Формула изобретения

Устройство управления для блоков памяти с разрешением неоднозначности, содержащее триггеры, единичный выход каждого из которых соединен с одним из входов соответствующего элемента И, тактовые входы триггеров объединены, а входы установки триггеров в единичное состояние являются информационными входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит сумматоры по модулю два, причем выход каждого элемента И соединен с соответствующими входами смежных сумматоров по модулю два и другим входом последующего элемента И, выходы сумматоров по модулю два соединены со входами управления соответствующих триггеров, нулевые выходы которых являются выходами устройства.

Источнйки информаций, принятые во внимание при экспертизе

1Е 1. Патент США № 3806889, кл. 340 — !72,5 опублик. 1974.

2. Патент США № 3806890, кл. 340 — 172,5, опублик. 1974.

3. Пилипосян Э.Р. К вопросу извлечеМ иия многозначного ответа из ассоциативного ЗУ. Третье Всесоюзное совещание по запоминающим устройствам электронных вычислительных машин. Сб. докладов под ред.

Е. А. Брика. Л., изд. НТОРЭС им. Попова, 1968, с. 6„0 (прототип).

1 з

744727. Составитель В. Гордонова

Рыак ор И. Нанкнна Техред К. Шуфрич Корректор М. Ленчик

Заказ 3824/l8 Тираж 662 Подписное

UHHHflH Государственного комитета СССР по делам изобретен нй .и открытий

113035, Москва. )K - 35. Раушская иа6., д. 4/5

Филиал ППП ° Èàòåíòý, г. Ужгород. ул. Проектная. 4