Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 744728

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 15.06.77 (21) 2496942/18-24 (51) М. Кл. с присоединением заявки №вЂ”

G 11 С 15/00

Государстевекык комитет (23) Приоритет—

Опубликовано 30.06.80. Бюллетень № 24 (53) УДК 681.327..6 (088.8) ло делам изобретений и открытий

Дата опубликования описания 05.07.80 (72) Авторы изобретения

Е. И. Ильяшенко и В. Ф. Рудаков (71) Заявитель

Всесоюзный институт научной н технической информации (54) ACCOUHATHBHOE ЗАПОМИНА1О1ИЕЕ УСТРОЯСТВО

Изобретение относится к области запоминающих устройств.

Известны ассоциативные запоминающие устройства (1 j и (3) .

Известны ассоциативные запоминающие устройства (АЗУ); содержащие матрицу многоразрядных запоминающих элементов, формирователи опросного тока, регистры и детекторы (1(.

В этих устройствах запоминающие элементы помимо собственно функции запоминания должны выполнять функцию «Неравнозначность» (или «Равнозначность») над хранимой и опросной информацией. Это значительно усложняет запоминающйй элемент, и следовательно, все устройство и приводит к большим аппаратурным затратам, прн которых использование таких АЗУ; особенно большого объема, становится экономически невыгодным.

Из известных устройств наиболее близким техническим решением к данному изобретению, является ассоциативное запоминающее устройство, содержащее регйстрй, выходы которых соединены с соответствующими входами элементов ИЛИ, выходы одних из которых подключены ко входам де,г

2 шифратора, запоминающие элементы, выходы которых соединень1 со входами соответствующих детекторов (2) .

Недостатком этого устройства является большое количество выходных шнн дешифратора (при большой емкости устройства), а также значительные аппаратурные затраты и сложность самого дешифратора с большим количеством выходных шин, что также снижает быстродействие устройства и препятствует построению АЗУ большого объема. я Цель изобретения — - увеличение информационной емкости И упрощение устройства.

Поставленная цель достигается тем, что устройство содержит дополнительные дешифраторы и элементы И»о числу запоминающих элементов, входы которых подключены т соответственно к выходам дешифраторов, выходы элементов И подключены ко входам соответствующих запоминающих элементов, входы дополнительных дешифраторов подключены к выходам других элементов ИЛИ.

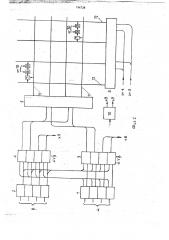

На фиг. 1 изображена блок-схема предложенного АЗУ, например емкостью 16 4-разрядйых двоичных чисел, для n = 1, где и— число дополнительных дешйфраторов; на фиг. 2 а показано выполнение запоминающе744728

3 го элемента для постояйного запоминающего устройства (АЗУ); на фиг. 2 б — то же,, для полуностоянного запоминающего устройства (ДПЗУ); на фиг. 2 в — - то же, для оперативного запоминающего устройства (ОЗУ); на фиг. 2 г — один из возможных вариантов за поминающего элемента для ОЗУ., Устройство содержит (фиг. 1) регистр 1, иСпользуемый в качестве опросного, регистр 2, являющийся маскирующим, группы элементов 3 и 4 ИЛИ, двшифратор 5, до полнительный дешифратор 6, элементы 7 И, запоминающие элементы 8, детекторы. 9, блок !О управления, горизонтальные 11 и вертикальные 12 координатные шины.

Нулевые выходы регистров 1-и 2 соединены с одними входами элементов 3 и 4 ИЛИ,.

fS другие входы элементов 3 и 4 ИЛИ соединены соответственно с нулевыми И едййичными выходами регистров 1 и 2. Выходы элементов 3 ИЛИ соединены соответственно с нулевыми входами дешифраторов 5 и 6, 29 а выходы элементов 4 ИЛИ подключены соответственно к единичным входам дешифраторов 5 и 6. Входы элементов И подключены соответственно к координатным шинам 11 и 12, соединенным с соответствующими выходами дешифраторов 5 и 6, выходы элементов 7 И подключены ко входам соответствующих запо)пинающих элементов 8.

B предлагаемом устройстве факт записи любого 4-разрядного двоичного кода ото- 35 ждествляется с установкой, например, в единичное состояние соответствующего запоминающего элемента 5.

В зависимости от требований к частоте и продолжительности времени .записи запоминающий элемент 5 может быть вЬ|полнен различными способами.

Если в устройстве допустима однократная запись (ПЗУ), то запоминающий элемент 5 может быть выполнен в виде усилительного элемента, либо просто перемычки

46 соединяющей выход элемента 7 И со входом соответствующего детектора 9 (в последнем случае факт отсутствия записи может бытьпредставлен "отсутствием соответствующего элемента 7 И и детектора 9) .

Если в устройстве допустимы сравнитель- 4> но редкая и медленная перезапись информации (ПЗУ), то запоминающий элемент 8 может быть выполнен в виде ключа !3, два выхода которого, соответствующие счит ыванию и записи, соединены со входами собственного элемента 14 памяти (фиг. 2 б).

SO

Если в устройстве требуется оперативная перезапись информации (ОЗУ), то в этом случае ключ 13 может иметь три выхода соответственно для записи, считывания и избирательного стирания информации Я (фиг. 2 в). либо ключ 13 может иметь два выхода (один -- для записи, другой — для считывания и избирательного стирания информации), а элемент памяти выполнен состоящим из триггера 15 и элемента 16 задержки (фиг. 2 r). В последнем случае стирающий импульс, поступающий на триггер, должен иметь длительность, превышающую время задержки в элементе 16 задержки.—

Ключ 13 (фиг. 26, в) управляется от блока

10Ä который может также быть использован. и для стирания всей информации в АЗУ.

Рассмотрим работу устройства в предположении, что его запоминающие элементы выполнены по схеме, изображенной на фиг. 2

Устройство может работать в четырех режимах: записи информации, общего стирания информации, избирательного стирания информации и поиска информации.

При этом предполагается, что все триггеры установлены первоначально в нулевое состояние.

Режим записи информации. В этом режиме в регистр 1 йбступает код числа, которое необходимо записать, а в регистр 2— код 1111 (т. е. содержащий все единицы).

В соответствии с этим кодом возбуждают один из выходов дешифратора 5 и один из .выходов дешифратора 6. На выходе элемента И, оба входа которого подключены к возбужденным выходам дешифраторов 5 и 6, появляется импульс, который через ключ 13, управляемый блоком 10, поступает на вход

l7 триггера 15 и устанавливает его в единичное состояние.

Режим общего стирания информации. В этом режиме на входы 18 всех триггеров 15 из блока IO поступает импульс, устанавливающий триггеры 15 в нулевое состояние.

Режим избирательного стирания информации. Этот режим отличается от режима записи тем, что с выхода ключа 13 импульс поступает на вход 19 выбранного триггера 15 и устанавливает его в нулевое состояние, При этом длительность импульса, поступающего на триггер 10 от ключа 8, должна быть больше времени задержки элемента 16.

Режим поиска информации. Целью поиска является выяснение факта записи в устройстве любого числа или некоторого подмножества чисел из множества, состоящего из чисел О, 1, 2, ... 14, 15 (0000, 0001.....1110, l1ll в двоичном коде), В соответствии с этимрассмотрим 2 случая поиска.

Первый случай. В этом случае требуется выяснить, записано ли в АЗУ, какое-либо конкретное число из множества чисел О, I,..., 14, 15.

На регистр 1 поступает двоичный код этого числа, который используется в качестве поискового образа, а на регистр 2 — код !

111 (т. е. состоящий из всех единиц).

Как и в режиме записи, на выходе единственного элемента 7 И, соответствующего коду поискового образа, появляется импульс, который через ключ 13 поступает на вход 19 соответствующего триггера 15. Если триггер 15 находится в единичном сгктоянии, 744728 что соответствует записи кода искомого числа в АЗУ, то он переключается в нулевое состояние. Импульс, появляющийся на вы ходе 20 триггера 15, используется для переключения соответствуюп1его детектора 9 в единичное состояние (перед началом поиска все детекторы 9 устанавливаются в нулевое состояние) и возврата в единичное состояние триггера 15 (через элемент 11 задержки}.

Если триггер 15 находится в нулевом состоянии, что соответствует отсутствию записи кода искомого числа в АЗУ, то îí 1о не изменяет своего состояния, поэтому не изменяет своего состояния и детектор 9, связанный с этим триггером 15 (ни один из детекторов 9 не изменяет своего состояния).

Второй случай. В этом случае требуется выяснить, записаны ли в АЗУ какие-либо

13 числа, часть разрядов которых совпадает с кодом числа, представляющего поисковый образ и входящего в множество чисел

0,1„..14,15.

Пусть конкретно требуется выяснить, записаны ли в АЗУ числа, совпадающие с кодом поискового образа во всех разрядах, кроме, например, младшего (младший разряд считается замаскированным).

На регистр 1 поступает код поискового образа, а на регистр 2 — код 1110 (т. е. состоящий из единиц во всех разрядах, кроме замаскированного). В этом случае возбужда ется один выход дешифратора 5 и два выхода дешифратора 6. На выходе двух элементов 7 И, оба входа которых связаны с координатными шинами 11 и 12, соединенными с возбужденными выходами дешифраторов 5 и 6, появляются импульсы (в общем случае при маскировании m разрядов кода поискового образа, где О gm <4 появляется импульс на выходе элементов 7 И И устройства (фиг. 1). Далее работа устройства подобна работе в режиме поиска (первый случай) с тем лишь отличием, что возможно переключение двух триггеров 15 и соответственно установление в единичное состояние стольких же детекторов 9. Обнару-, жение детекторов, установленных в единичное состояние, выполняется известными способами f3). . В предлагаемом устройстве значительно сокращены аппаратурные затраты на дешифрирование (при одной и той же емкости АЗУ), а также существенно уменьшено количество дешифраторных шин. Для предложенного А3У, хранящего 16-разрядные числа и соответственно емкостью 2 чисел, количество дешифраторных шин уменьшается по сравнению с известным (прн п = 1) в 256 раз.

Уменьшение количества шин имеет важное значение при выполнении предложенного устройства на интегральных схемах.

Формула изобретения

Ассоциативное запоминающее устройство, содержащее регистры, выходы которых соединены соответственно со входами элементов ИЛИ, выходы одних иэ кото) ых подключены ко входам дешифратора, запоминающие элементы, выходы которых соединены со входами соответствующих детекторов, отличающееся тем, что, с целью увеличения информационной емкости и упрощения устройства, оно содержит дополнительные де-, шифраторы и элементы И по числу запоминающих элементов, причем входы элементов И подключены соответственно к выходам дешифраторов, выходы -- ко входам соответствующих запоминающих элементов, входы дополнительных дешифраторов подключены к выходам других элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1, Крайзмер Л. П. и др. Ассоциативные запоминающие устройства. Л., «Энергия», 1957, с. 32 — 37.

2. Авторское свидетельство СССР llo заявке № 2430439/24, кл. (i 1 С 15/00, 16.12.76.

3. Ильяшенко F.. И., Рудаков В. Ф. Ассоциативные запоминаюнсие устройства на маГнитных элементах. М., «Энергия», 1975, с. 45 — 51 (п рототи и ) .

744721

Составитель И. Гордонова

Рехактор И, Нянкнна Техред К. Шуфрнч Корректор M. Демчнк

:3 а к з з 3 A 24/ I II Тираж 662 1lодпнсное

1111ИИ11И Государственного комитета СССР по делам нэобретеннй и открытий

I I 3035, Москва. Ж -35. Рау нес к а я наб., д. 4/5 I>нлнал !11111 ellатентз. г. Ужгород, Ул. 1lроектная. 4