Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii 74473)l

Союз Советскнн

Соцнапнстнческмк

Респубннк (6!) Дополнительное к авт. свид-ву— (22) Заявлено 28.03.78 (2! ) 2597202/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М.К .

Ci I I С !7/00

Государственный комитет

СССР

Опубликовано 30.06.80. Бюллетень № 24 (53) УДК 681.327. .6 (088.8) llo делам изобретений н открытий

Дата опубликования описания 05.07.80 (72) Авторы изобретения

П. И. Платонов, В. И. Скорубский и H. И. Конон (7I) Заявитель (54) ПОСТОЯННОЕ ЗЛПОМИНА!ОЩЕЕ УСТРОЙСТВО!

Изобретение относится к вычислительной технике и может быть использовано для построения устройств хранения дискретной информации..

Известны постоянные запоминающие устройства для хранения дискретной информации,содержащие дешифратор адреса, выходы которого подключены ко входу накопителя, а выходы накопителя к выходным усилителям (1 j ..

Такие запоминающие устройства имеют малую информационную емкость и болЬшой объем накопителя из-за огромного числа запоминающих элементов в накопителе.

Известны также постоянные запоминающие устройства, которые кроме дешифратора адреса и накопителя имеют шифратор, входы которого подключены к накопителю, а выходы шифратора являются выходами устройства (21.

Но и эти постоянные запоминающие устройства имеют болыцое количество оборудования и малую информационную емкость.

Наиболее близким техническим решением. к предлагаемому является запоминающее устройство, содержащее дешифратор адреса, выходы которого через первую группу

2 элементов ИЛИ соединены с соответствующими входами накопителя, второй группы элементов ИЛИ, входы которых подключены к выходам накопителя, а выходы через усилители считывания — к соответствующим входам сумматора.

В сумматоре постоянного запоминающего устройства происходит формирование требуемых кодов чисел путем сложения нескольких кодов, выбранных из различных частей накопителя (3(.

Недостатком этого устройства является то, что оно имеет болыпое количество ohорудования, в особешпгсти запоминающих элементов в накопителе и цевысокое быстродействие из-за нали цгя в устройстве сумматора. Так, например, время сложения ((,„) двух чисел в наиболее быстродействующем асинхронном сумматоре зависит от разрядности сумматора (разрядность сумматора определяется разрядностью суммируемых чисел) и раино

feJL= (Е+ 10Кап - u где — времтт срабатывания схемы обраЕ зования счммы;

744731

Разрндиость

Емкость намитн в чнслак (словак} й

Предлагаемое

92

IN

I 88

3}6 б!2

)024

2048

4096

32

64

l28

256

t время распространения переноса в одном разряде; п †число разрядов сумматора.

Время срабатывания известного (4р,а.„,в) запоминающего устройства равно ! срлб.и в.= !Ам+ 2(нлм + ус,+ t a где tgg, !ц „, („„(щ,6 и (е„соответственно время срабатывания дешифратора адреса, элемента. ИЛИ, усилителя считывания, время выборки кода числа из накопителя и время сложения двух чисел на сумматоре.

Цель изобретения. — повышение надежности и быстродействия устройства.

ПосТавленная цель достигается тем, что в постоянное запоминающее устройство, содержащее дешифратор, выходы которого сое"динены со входами" накопителя и. элементов

ИЛИ первой группы, вторую группу эле-ментов ИЛИ, введены элементы И н регистр

"числа, входы которого через элементы ИЛИ второй rpyrim соединены с выходами соответствующих элементов И, первые входы соответствующих элементов И подключены

}; вйходам накопителя, а вторые — к выходам элементов ИЛИ первой группы.

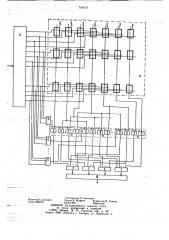

На чертеже представлена блок-схема постоянного запоминающего устройства для хранения 4-х разрядных чисел.

Устройство содержит дешифратор 1 адре са, первую группу элементов 2 ИЛИ, запо: минающие элементы 3 накопителя 4, (двухвходовые) элементы 5 И группы б двухвходовых элементов 5 И, вторую группу элементов 7 ИЛИ и регистр 8 числа.

Выходы дешифратора адреса подклю: — чены ко входам соответствующих элементов 2 ИЛИ первой.,группы и к соответствующим . запоминающим элементам 3 накопйтеля 4. Выходы матричного накопителя 4 . соединены с первыми входами двухвходовых элементов 5 И каждой группы б элементов 5 И.

Вторые входы элементов 5 И каждой группы б соединены между собой и подклю- чЕны К выходу соответствующЕго элемента

2 ИЛИ. Выходы элементов 5 И одноименных разрядов ка;lloA группы 6 элементов

5 И объединены с помощью элементов

7 ИЛИ, выходы котбрых пойключемы .ко входу регистра 8 числа. Выход регистра 8 числа является выходом запоминающего устройства.

Устройство работает следукнцим образом

После расшифровки кода адреса дешифратором I адреса на одном из его выходов появляется сигнал, который поступает на один вход соответствующего элемента

2 ИЛИ и на вход матричного накопителя 4, обеспечивая считывание требуемого кода числа из запоминающих элементов 3 накопителя 4.

Разряды считанного кода числа поступают на первые входы соответствующих элементов 5 И группы 6, на вторые входы — сигнал с выхода элемента 2 ИЛИ, разрешая выдачу числа из накопителя через элементы

7 ИЛИ на вход регистра 8 числа, С регист ра 8 числа требуемый код числа выдается из запоминающего устройства.

В предлагаемом устройстве количество оборудования сокращается за счет уменьшения числа запоминающих элементов в матричном накопителе.

Уменьшение количества m запоминающих элементов в устройстве достигается за счет того, что информация в памяти хранится в сжатом виде. Например, шесть следующих 4-х разрядных чисел 14, !2, 9, 2, 5, IO могут быть представлены в виде сжатой последовательности. Следовательно, для хранения этих чисел необходимо 9 запоминающих элементов, а при известном способе потребовалось бы m = N .n = 9 .4 = Зб.

Где N — количество хранимых чисел в памяти; п — количество разрядов в числе, 50 m — количество запоминающих элементов.

В предлагаемом устройстве все числа

N делятся наогруппы по - - чисел в кажИ дой группе. Каждая группа чисел хранится в сжатом виде в одной строке запоминающих элементов 3 матричного накопи35 теля 4, Количество запоминающих элементов в предлагаемом устройстве при хранении и-разрядных чисел определяется соотношением

m = в(-о + и — !), а при известном спо И собе m = N.tt; где в — количество r póïï, на которые делятся все хранимые числа

s памяти (или число строк запоминающих элементов 3 в матричном накопителе 4)., Сравнительная характеристика предлагаемого и известного устройств по количеет45 ву запоминающих элементов m в зависимости от объема памяти приведена в таблице.

Количество заномннающнк элементов

Известное

Количество элементов 2 ИЛИ н число групп 6 элементов 5 определяется количеством-групп в, на которые делятся все хранимые числа N (или то же самое количеством строк в матричном накопителе), а количество элементов И 5 в каждой группе 6 и число элементов 7 ИЛЙ равно и.

Время срабатывания предлагаемого (Цр„6„>) устройствй определяется соотношением

tcpa6.пр = 4ш+ te 6 + (и +t„„<+ tpe„

Если предположить, что любое, запом1п аю- шее устройство имеет регистр числа и что ти = 1или, то предлагаемое устройство по сравнению с известным позволяет повысить быстродействие на величину t«+ t c.

Применение групп двухвходовых элементов И выгодно отличает предлагаемое запоминающее устройство от известного, так как позволяет уменьшить количество оборудования, в особенности запоминающих элементов в накопителе, а также увеличить быстродействие за счет того, что формирование кодов чисел, в отличие от известного,осуществляется без применения сумматора..

744731

Формула изобретения

Постоянное запоминающее устройство, содержащее дешифратор, выходы которого соединены со входами накопителя и элементов ИЛИ первой группы, вторую группу элементов ИЛИ, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, оно содержит элементы И и регистр числа, входы которого через элементы ИЛИ второй группы соединены

te с выходами соответствующих элементов И, первые входы соответствующих элементов И подключены к выходам накопителя, а вторые — к выходам элементов ИЛИ первой группы.

Источники информации, принятые во внимание при экспертизе

1. Брик Е. A. Постоянные запоминающие . устройства. «Энергия», 1969, с. 25.

2. Авторское свидетельство СССР

2å № 3123!О, кл. 6 11 С 17/00, 1971

3; Авторское свидетельство СССР № 490184, кл. G 1! С 17/00, 19?5 (прототип).

74473!

Редактор A. Доламич

Заказ 3824!18

Составитель Л. Амусьева

Техред К. Шуфрнч Корректор М. Демчнк

Тираж 662 Подписнде

ЦНИИПИ Государственного комитета СССР но делам изобретений и отхрытнй

l 13035, Москва, Ж -ЗБ, Рауиккаи изб., д. 45

Филиал ППП хПатент>, r. Ужгород, ул. Проектная. 4