Устройство для контроля памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социепистмческик

Респубпик ни 744737 (61) Дополнительное к авт. свид-ву— (22) Заявлено 20.03.78 (21) 2592267/1 8-24 (51) М. Кл.к с присоединением заявки №вЂ”

G 11 С 29/00

Ге«удерственнмй кюмнтЕт

СССР (23) Приоритет—

Опубликовано 30 06.80. Бюллетень ¹ 24 (53) УДК 681.327 . (088.8) «о делам «зебретеннй н открмтнй

Дата опубликования описания 05.07.80 (72) Авторы изобретения

Н. И. Варяес, Б. Е. Гласко и А. К. Култыгин (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАМЯТИ

Изобретение относится к области запоминающих устройств.

Известны устройства для контроля памяти, содержащие накопитель. подключенный через блок воспроизведения к регистру числа выполненному на триггерах со счетным входом, блок контроля достоверности информации, соединенный с блоком управления и с регистром числа (Ц.

Это устройство позволяет исправлять одиночные ошибки, но недостатком его является то, что нет локализации места ошибки.

Наиболее близким техническим решением к данному изобретению является устройство для контроля памяти, содержащее информационный регистр, регистр контрольных разрядов, шифраторы записи и считывания, схему сравнения, дешифратор и блок управления, причем выход информационного регистра соединен со входами шифраторов записи и считывания и одним из выходов устройства, вход которого подключен к первым входам информационного регистра и регистра контрольных разрядов, выход которого подключен к первому входу схемы сравнения. второй вход которой соединен ==-=- — = с""вИходом" йифратора считывания, первый выход — со входом дешифратора, выход которого соединен со вторыми входами информационного регистра и регистра контрольных разрядов, выход шифратора записи соединен с другим выходом устройства, второй выход схемы сравнения подключен ко входу блока управления, первый выход которого соединен с управляющими входамн регистра контрольных разрядов и информационного регистра 12 .

В этом устройстве осуществляется исправление одиночных ошибок.

Недостатком этого устройства является то, что нет локализации неисправности в цепях "коррекцйи ошибок и в накопителе, что снижает надежность устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что устройство содержит генератор кодов ошибки, дополнительную схему сравнения и ло.гический блок, входы которого соединены

20 соответственно с выходами схем сравнения, " и вторым выходом"блока управления, первый вход дополнительной схемы сравнения под- . ключен к выходу регистра контрольных разрядов, второй вход — к другому входу

744737 .

jet з дешифратора и выходу генератора кодов ошибки. вход которого соединен с третьим выходом блока управления, выход ц ифратора записи соединен с третьим входом регистра контрольных разрядов.

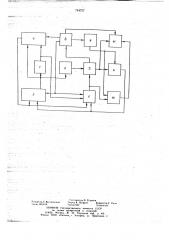

На чертеже представлена блок-схема устройства для контроля памяти.

Устройство содержит шифраторы 1 записи и 2 считывания, схему 3 сравнения, дешифратор 4, информационный регистр 5, регистр 6 контрольных разрядов. Входы и, выходы устройства соединены с выходами и входами. контролируемого накопителя 7.

Устройство также содержит блок 8 управления, генератор 9 кодов ошибки, допдлнительную схему 10 сравнения, логический блок 11, служащий для анализа неисправности цепей коррекции.

Выход регистра 5 соединен со входами шифраторов 1 и 2 и одним из выходов устройства, вход которого подключен к первым входам регистров 5 и 6. Выход регистра 6 подключен к первому входу схемы

3 сравнения, второй вход которой соединен. с выходом шифратора 2, первый выход— с одним из входов дешифратора 4, выход которого соединен со вторыми входами регистров 5 и 6, второй выход схемы 3 сравнения подключен ко вхбду блока 8 управления, первый выход которого соединен с управляющими входами регистров 5 и 6.

Входы логического блока 11 соедйнень! соответственно с выходами схем 3 и. 10 сравнения. Первый вход схемы 10 сравнения подключен к выходу регистра 6, второй вход — к другому входу дешифратора 4 и выходу генератора 9, вход. которого соединен с третьйм выходом блока 8 управления. Выход шифратора 1 соединен с третьим входом регистра 6.

Устройство работает в двух режимах: рабочем и проверочном.

В рабочем режиме информация поступает на информационный регистр 5, а затем на шифратор 1 записи, который вырабатывает контрольные разряды в соответствии с кодом Хэмминга. Затем ийформационный код и контрольные разряды записываются в накопитель 7. При считывании информация нз накопителя 7 поступает на информационный регистр 5 и регистр 6 контрольных разрядов, а затем из информационного регистра 5 — на шифратор 2 считывания, который вновь формирует контроль-. ные разряды. Схема 3 сравнения сравни; вает код с регистра б контрольных .разрядов с кодом. сформированным шифратором

2 считывания, в случае ошибки в цепи кор- рекции ошибки, которая включает в себя информационный регистр 5, регистр 6 контрольных разрядов, шифратор 1 записи, шифратор 2 считывания, схему 3 сравнения, дешифратор 4, схема 3 сравнения вырабатывает код номера ошибки, который поступает на вход дешифратора 4, а сигнал о наличии ои ибки, который поступает на блок

8 управления, с выхода дешифратора 4 номер неисправного разряда корректирует соответствующий разряд в информационном регистре 5 или в регистре.б контрольных разрядов.

В рабочем режиме блок 8 управления запрещает работу генератора 9 кодов, запись информации с шифратора 1 записи в регистр б контрольных разрядов и осуществление останова блоком 1! цепей коррекции.

Ю В проверочном режиме при наличии в .блоке 8 управления информации об ошибках в рабочем режиме осуществляется локализация неиСправности накопителя 7. При этом определяется местоположение ошибки: либо ошибка в накопйтеле 7, либо в цепи коррекции, с точностью до неисправного блока цепи коррекции и номера разряда, в котором произошла ошибка.

В проверочном режиме блок 8 управления формирует сигналы, запрещающие образе щение к .накопителю 7, разрешает работу генератора 9 кодов ошибки и одновременно открывает регистр 6 контрольных разрядов для записи туда информации с шифратора l записи. Код ошибки с генератора 9 кодов ошибки подается на входы дешифратора 4 и дополнительной схемы 10 сравнения, В первом такте дешифрируемый код ошибки записывается в информационный регистр 5 и в регистр 6 контрольных разрядов, предварительно обнулен ные, уу Шифратор 1 записи и шифратор 2 считывания формируют контрольный код числа, записанного в информационный регистр

5, во втором такте контрольный код с выхода шифратора 1 записи записывается в

3S регистр б контрольных разрядов, код которого сравнивается схемой 3 сравнения с кодом, сформированным шифратором 2 считывания, и сравнивается дополнительной схемой 10 сравнения с кодом генератора 9. Результаты сравнения анализируются блоком 11.

Локализация неисправностей цепи коррекции осуществляется с точностью до двух блоков цепи коррекции при наличии только одной неисправности в одном из этих блоков.

Возможны варианты неисправности блоков коррекции.

Неисправен шифратор записи I. Код, сформированный в шифраторе 1 записи, записанный в регистр 6 контрольных разрядов, е подается на входы схем 3, 10 сравнения, и на выходе обеих схем появляются сиг-":-"" """ "налы ошибок.

Неисправен шифратор 2 считывания. Код; сформированный этим шифратором, подает- ся только на вход схемы 3 сравнения, на выходе этой схемы появляется сигнал ошибки.

Неисправен информационный регистр 5.

Так как шифраторы 1 записи и 2 считывания формируют контрольные коды ошибоч744737

5 ного информационного числа, и они сравниваются схемой сравнения 3, то на выходе этой схемы сигнала ошибки иет, а дойолнительная схема 10 сравнения сравни. вает код, сформированный шифратором 1 записи из ошибочного числа, с кодом генератора 9 кодов ошибки, на выходе дополнительной схемы 1О сравнения появляется сиг,- .нал ошибки.

Неисправен регистр контрольных разрядов 6. Код с этого регистра подается на входы схем 3, 10. сравнения, сигналы ошибок появляются на выходах обеих схем.

Неисправна схема сравнения 3. Сигнал ошибки на выходе этой схемы.

Неисправна дополнительная схема сравнения 10. Сигнал ошибки на выходе этой схемы. 15

Неисправен дешифратор 4. Это соответствует записи ошибочного кода в информационный регистр 5. Сигнал ошибки появляется только на выходе дополнительной схемы 10 сравнения.

Блок анализа фиксирует три случая, ко3Е торые приводят к останову устройства.

В первом случае фиксируется сигнал ошибки на выходе схемы 3 сравнения, что определяет неисправность или в самой схеме, или в шифраторе 2 считывания. 25

Во втором случае фиксируется сигнал ошибки на выходе дополнительной схемы

10 сравнения, что определяет неисправность или в дешифраторе 4, или в информационном регистре 5, или в дополнительной схеме 10 сравнения.

В третьем случае. фиксируется сигнал иа выходах схем 3 и 10 сравнения, что определяет неисправность или в шифраторе 1 записи, или в регистре 6 контрольных раз.рядов. 55

В случае отсутствия неисправности в цепи коррекции, что соответствует отсутствию сигнала ошибок на выходах схем 3 и 10 сравнения, и наличия зафиксированных ошибок в первом режиме судят о неисправности 4в на ко пи тел я.

Предлагаемое устройство для контроля памяти не только исправляет одиночные ошибки, но и локализует неисправности с

6 точностью до определенного блока цепи коррекции, что повышает его точность.

Формула изобретения

Устройство для контроля памяти, содержащее информационный регистр, регистр контрольных разрядов, шифраторы записи и .считывания, схему сравнения, дешифратор и блок управления, причем выход информационного регистра соединен со входами шифраторов записи и считывания и одним из выходов устройства, вход которого подключен к первым входам информационного регистра и регистра контрольных разрядов, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом шифратора считывания, первый выход — с одним из входов дешифратора, выход которого соединен со вторыми входами информационного регистра и регистра контрольных разрядов, выход шифратора записи соединен с другим выходом устройства, второй выход схемы сравнения подключен ко входу блока управления, первый выход которого соединен с управляюшими входами регистра контрольных разрядов и информационного регистра, отличающееся тем, что; с целью повышения надежности устройства, оно содержит генератор кодов ошибки, дополнительную схему сравнения и .логический блок, входы кото--рого соединены соответственно с выходами схем сравнения и вторым выходом блока управления, первый вход дополнительной схемы сравнения подключен к выходу регистра контрольных разрядов, второй вход — к другому входу дешнфратора и выходу генератора кодов ошибки, вход которого соединен с третьим выходом блока управления, выход шифратора записи соединен с третьим входом регистра контрольных разрядов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 333605, кл. G Il С 29/00, 1970.

2. Актуальные вопросы технической кибернетики. М., «Наука», 1972, с. 235 — 240 (прототип),.

744737

Составнтель В. Рудаков

Редактор Л. Веселовская Техред К. 11!уфрнч Корректор Е 11аяп

:1з к аз 3К24/1 8 Тираж 662 Подпнсное

И1! И И11И Государственного ком мтета СССР по делан нзобретений н открнтнй! 1З(135, Москва, Ж 35, Раушскан наб., д. 4/5

Фмлиал I II II I <Патент>, г. Ужгород, ул. Проектная, 4