Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

О П И C А Н И Е,744740

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (6l) Дополнительное к авт. свид-ву— (22) Заявлено 10.04.78 (2l) 2602531/18-24 (51) М. Кл.

G 1l С 29/00 с присоединением заявки ¹вЂ”

Гвсударстввннв1й квинтет

СССР

Ito делам навбретеннй н втхрытнй (23) Приоритет—

Опубликовано 30.06.80. Бюллетень ¹ 24

Дата опубликования описания 05.07.80 (53) УДК 68 l.327 (088.8) (72) Авторы изобретения

А. А. Елисеев, Д. Б. Жаворонков и В. М, Ленкова (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С КОРРЕКЦИЕЙ ОШИБОК

И зобретение относится к запоминающим уст ойствам. звестно устройство, содержащее блок памяти, блок контроля, блок управления, операционный блок н генератор четности fl).

Недостатком устройства являются боль-. шие аппаратурные затраты; . Наиболее близким техническим решением к предлагаемому является запоминающее устройство с коррекцией ошибок, содержащее матричный накопитель, соединенный с регистром адреса и информационным регистром, выход которого подключен к первому входу блока контроля, логический блок, первый и второй входы которого подключены соответственно к выходам регистра адреса и информационного регистра, а выход соединен со входом генератора четности и информационным входом регистра адреса, формирователь запросов управления, вход которого подключен к выходу блока контроля и входу устройства, а выход соединен со входом блока управления, выход которого подключен к управляющим входам регистра адреса, информационного регистра и логического блока {2).

Недостатком этого устройства является наличие сложных узлов управления реконфигурацией накопителя, а также необходимость иметь набор резервных модулей на. копителя, подключаемых взамен отказавших.

Кроме этого в этом устройстве после отказа какого-либо модуля накопителя полностью теряется блок информации, расположенный в этом модуле, поэтому требуется специальная разработка математического обеспечения, позволяющая организовать . контрольную точку (т. е. запомнить, например, на внешнем носителе всю существенную информацию о программе, выполняемой устройством) н выполнить перезапуск программы с контрольной точки после . обнаружения отказа.

Цель изобретения — упрогцение устройства.

Поставленная цель достигается тем, что устройство содержит селектор, блок поразрядного сравнения, регистр четности столбцов, элемент НЕ и дополнительный инфор. мационный регистр, входы которого подкл очены соответственно к выходам операционного блока, информационного регистра и генератора четности, а выход соединен с on.

744?40 иим иэ входов матричного накопителя и первым входом блока поразрядного сравнения, второй вход которого подключен к выходу селектора, входы селектора соединены соответственно с выходами информационного регистра и регистра четности столбцов, входы которого подключены к выходу блока поразрядного сравнения и входу устройства, который через элемент НЕ соединен со вторым входом блока контроля, выход регистра четности столбцов подключен к третьему входу логического блока, управляющие входы дополнительного информационного регистра, блока поразрядного сравнения и селектора .соединены с выходом блока управлейия.

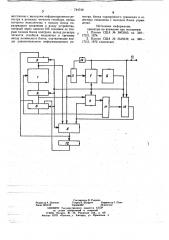

На чертеже изображена функциональная схема устройства.

Устройство содержит матричный накопитель 1, информационный регистр 2, блок

3 контроля, селектор 4, дополнительный информационный регистр 5, логический блок 6, формирователь 7 запросов управления, блок

8 управления, регистр 9 адреса, регистр 10 четности столбцов, блок 11 поразрядного сравнения. генератор 12 четности. Устройство имеет вход 13, подключенный ко входу элемента 14 НЕ. Выход регистра 2 подключен к первому входу блока 3. Первый и второй входы блока 6 подключены соответственно к выходам регистров 9 и 2. Входы регистра 5 подключенйсоответственно к выходам блока 6, регистра 2 и генератора 12, а выход соединен с одним из входов накопителя 1 и первым входом блока 11, второй вход которого:подключен к выходу селектора 4. Входы селектора 4 соединены соответственно с выходами регистров 2 и 10, Входы регистра 10 подключены к выходу блока 11 и входу устройства 13. Выход элемента 14 HE соединен со вторым входом блока 3. Выход регистра 10 подключен к третьему входу блока 6. Управляющие входы регистра 5, блока 11 и селектора 4 соединены с выходом блока 8.

Устройство работает следующим образом.

Накопитель хранит N-разрядные слова памяти, в которых размещаются команды программы и данные. Каждое слово памяти имеетаодин контрольный разряд, образованный суммированием по модулю 2 (и.последующим инвертированием результата) информационных разрядов слова, т. е. физическая длина слова памяти равна N + разрядов. Группе i-ых разрядов (для i =

= 1, 2...N, N + 1) всех слов памяти приписан один контрольный разряд — разряд четности i-ого столбца (если расположить слова и а м я ги в виде последовательности строк, где одно слово составляет строку, то i-ый разряд всех слов представляет собой i-ый столбец). Все (N + 1)-ые разряды четности столбцов сгруппированы в (N + 1)разрядный регистр 10. Каждый i-ый разряд регистра !О образуется суммированием по модулю 2 (с инвертированием результата) всех разрядов i-ro столбца.

При запуске устройства на входе 13 выл рабатывается сигнал сброса, приводящий устройство в исходное состояние, По этому сигналу все разряды регистра !О принуди-. тельно устанавливаются в единичное состояние и формирователь 7 выдает в блок 8 управления запрос на процедуру приведе.ния устройства в исходное состояние. При выполнении этой процедуры содержимое накопителя 1 обнуляется и для каждого слова памяти формируется единичный контрольный разряд слова. Обнуление содержимого накопителя 1 происходит в следующей последовательности: I) в блоке 6 подготавли- вается адрес очередного обнуляемого слова путем модификации адреса предыдущего слова, находящегося в регистре 9 адреса; 2) про модифицированный адрес засылается в ре © гистр 9 и в регистр 2, из накопителя 1 считывается очередное обнуляемое слово,,так как в прочитанном слове может оказаться ошибка, работа блока 3 контроля на время приведения в исходное состояние. забло-. кирована через элемент 14 НЕ сигналом сброса на входе 13; 3) в регистр 5 с выхода блока 6 заносится нулевая информация в контрольный разряд регистра 5 заносит- . . ся содержимое генератора 1 2 четности;

4) сформированное в регистре 5 нулевое

>@ слово с единичным контрольным разрядом записывается в накопитель I 5) шаги 1 — 4 продолжаются до завершения обнуления всего накопителя I, Б исходном состоянии все слова памяти обнулены, контрольные разЗЯ ряды всех слов равны единице, в регистре

10 все разряды равны единице.

При записи в накопитель 1 произвольной информации по какому-либо адресу выполняются следующие действия, В регистр адреса 9 помещается адрес ячейки памяти, в которой выполняется запись н первоначальное содержимое записываемого слова считывается в регистр 2, В регистр 5 с выхода блока 6 заносится новая записываемая информация. Селектор 4 по сигналу из блока 8 управления передает на один из входов блока 11. содержимое регистра 2. На другой вход блока 11 поступает содержимое регистра записи 5. Если в какой-либо паре -ых разрядов регистра 2 (старые данные) н регистра 5 (новые даиные) обнаружено несравнение, на выходе

i-го разряда блока ! вырабатывается сигнал переключения i-го разряда регистра IО.

Каждый разряд регистра 10 выполнен на триггере со счетным входом, изменяющем свое состояние по сигналу переключения данного разряда, который вырабатывается на .соответствующем выходе блока 11. Таким образом, модификация контрольного разряда столбца выполняется только в том случае, когда в соответствующий разряд ячей744740

5 ки памяти записывается единица, а предыдущее состояние этого разряда было нулевым, или при записи нуля, если в разряде перед записью была единица. Регистр 10 сохраняет текущее состояние контрольных разрядов столбцов, изменяя состояние при любой модификации данных в накопителе 1.

Если в процессе обработки данных после считывания очередного слова данных из накопителя 1 в регистр 2 блок 3 обнаруживает ошибку, в формирователь 7 выдается сигнал о наличии ошибки. Формирователь 7 возбуждает запрос, по которому блок управления 8 вырабатывает последовательность сигналов по обработке возникшей ошибки. Эта последовательность включает сохранение содержимого регистра адреса 9 (адрес ячейки, в которой обнаружена ошибка) в блоке 6 и считывание всех ячеек накопителя с параллельной модификацией содержимого регистра 10. Для обеспечения этой модификации в регистре 5 при выполнении чтения из накопителя 1 формируется нулевая информация, поэтому на выход блока 11 выдается содержимое регистра 2. Каждый разряд регистра 10 при выполнении этой последовательности подсчитйвает контрольную сумму разрядов соответ ствуюц1его столбца. После очередной модификации регистра 10 информация, прочитанная в регистр 2, пересылается в регистр 5 и записывается в накопитель 1 по прежнему адресу. После считывания всех- слов накопителя Iврегистре,,10 будет сформирована контрольная сумма всех столбцов накопителя 1.

Для определения типа возникшей ошибки содержимое регистра 10 передается на анализ в блок 6. При отсутствии ошибок или при наличии четного числа ошибок в одном и том же разряде нескольких слов все разряды регистра 10 равйы единицам.

Так как подсчет четности столбцов выполняется только при обнаружении ошибки, такое сачтояние регистра 10 говорит о наличии ошибки в одинаковом разряде четного . числа слов. Одиночная ошибка приведет к

:. тому, что контрольная сумма столбца, которому принадлежит разряд-с ошйбкой, ока- . жется нулевой.

50

Форл ула изобретения

Запоминающее устройство с коррекцией ошибок. содержащее матричный накопитель, соединенный с регистром адреса и информационным регистром, выход которого подключен - к первому входу блока контроля, логический блок, первый и второй входы которого подключены соответственна к выходам регистра адреса и информационного регистра, а выход соединен со входом генеpampa четности и информационным входаМ регистра адреса, формирователь запросов управления, входы которого подключены к выходу блока контроля и входу устройства, а выход соединен со входом блока управления, выход которого подключен к управляющим входа м регистра адреса; информационного регистра и логического блока, отличающееся тем, что, с целью упрощения .: устройства, оно содержит селектор, блок поразрядного сравнения, регистр четности столбцов, элемент НЕ и дополнительный ин-:. формационный регистр, входы которого под- ключены соответственно к вйходам логического блока, информационнога регистра и ге55 нератора четности, а выход соединен с одним из входов матричного накопителя и пер,вым входом блока поразрядного сравнения, Все разряды регистра 10, за исключе-. нием одного, в этом случае являются единичными. Для исправления одиночной ошибки результирующее содержимое регистра 10 инвертируется. Инвертирование обеспечивается выдачей единиц во всех разрядах на вы- ход блока 11. Генерация единиц на выходе этого блока задается специальным управляю-. щим сигналом, который вырабатйвается блоком 8 управления, После инвертирования в регистре 10 установлен в единицу только один. разряд, соответствующий сбойному разряду в слове памяти. Адрес ошибочного слова пересылается из блока 6 в регистр адреса 9, ошибочное слово вновь считываб ется из накопителя 1 в регистр 2 и передается в регистр 5. Блок Ь управления выдает в селектор 4 управляющий сигнал, переключающий селектор 4 на выдачу. на выход содержимого регистра 10. На один из входов блока 11 передается содержимое регистра 5,(исправляемое слово), на .другой его вход — нулевое слово с единицей в том разряде, в котором произошла ошибка..В результате на выходе блока 11 формируется исправленное слово памяти, так как ошибочный разряд инвертируется. Регистр 10 сбрасывается по сигналу сброса из блока 8 управления и затем в него за.. носится скорректированное слово. После этого скорректированное слово пересылается через блок 6 в регистр 5 и записывается по прежнему адресу в накопитель .

Основным технико-экономическим. преимуществом изобретения является то, что при любой длине слова памяти избыточность накопителя составляет один двоичный разряд на слово, т. е. относительная избыточность накопителя

К = < —. 100% = 303% (длясловадли32+ 1 ной 32 разряда);

К =,, 100% = 1,54% (длясловадлиной 64 разряда) .

По сравнению с известным относительная избыточность накопителя в предлагаемом устройстве уменьшается примерно на

12,8% для слова памяти длиной 32 разряда и на 8,4% для слова памяти длиной 64 разряда. второй вход которого подключен к выходу селектора, входы селектора соединены соат

744740

Состааытель В. Рудаков

Редактор А. Долнннч Техред К. Шуфрнч Корректор F. Пяпн

Заказ 3824/l в Тара@,662 Подписное

UHHHllB Государственного комитета СССР по делам изобретений н открытый

1 l 3035, Москва, Ж -- З5, Рву шская наб., д. 45

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 ветственно с выходами информационного регистра и регистра четности столбцов, входы которого подключены к выходу блока поразрядного сравнения и входу устройства, который через элемент HE соединен со вторым входом блока контроля, выход регистра четности столбцов подключен к третьему входу логического блока, упрзвляющие входы дополнительного информационного ре8 гистра, блока поразрядного сравнения и селектора соединены с выходом блока управ ° лени я.

Источники информации, принятые во внимание при экспертизе !. Патент США № 3803560, кл. 340—

172.5, 1974.

2. Патент США № Зб48239, кл. 340—

172.5, !972 (прототип).