Многоканальный преобразователь аналог-код

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii 744969 (6I) Дополнительное к авт. саид-ву (22) заявлено 21.1 1.77 (21 ) 2544343/1 8-21 (5l)M. Кл.

Н 03 К 13/17 с присоединением заявки ¹

Гасударственный комитет (23) Приоритет— но делам нэобретеннй н открытий

ОпУбликовано 30.06.80. Бюллетень № 24

Дата опубликования описания 03.07.80 (53) УДК681.326 (088.8) (72) Авторы изобретения

T. А. Алиев и А. Н. Колесников

Институт кибернетики АН Азербайджанской CCP (71) Заявитель (54) N НОГОКА НАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ-KOD

Изобретение относится к измерительной технике и может использоваться для иэмесения многомерных сигналов, представленных в аналоговой форме.

Известны аналоговые преобразователи развертьвающего типа, в которых осущест5 вляется последовательное кодирование начальных напряжений по принципу счета циклической разверткой эталонного ступенчатого напряжения (1)

Общий недостаток всех этих устройств заключается в том, что их возможности ограничены только преобразованием в циф ровой код входных сигналов, представлен15 ных в аналоговой форме, Наиболее близким к предлагаемому устройству является аналого-цифровой преобразователь, содержащий генератор импульсов, преобразователь код-напряжение, дво- „ ичный счетчик, схемы сравнения, коммутатор каналов, вентиль f2)

Цель изобретения — расширение функцт ональньм воэможностей преобразователя, что предусматривает одновременно с преобразованием входных аналоговых переменных Х (J 1,2Ä.., K,...n) в цифровой код измерение искомой нензмеряемой величины У согласно заданному уравнению рет ре ссии

Al

У= а Е Ь, .Х;, Дi(rl

1» по цифровым значениям косвенных измеряемых величин Х; .

Цель достит ается тем, что в преобразователь аналот код, содержащий и блоков сравнения, первые входы которьм соединены с соответствующими и шинами входного сигнала, вторые входы соединены с Bblxo» дом преобразователя кода в напряжение, в выходы подключены соответственно к пер»вым входам тт первых элементов И, вторые входы которых соединены с соответствующими q выходами коммутатора каналов, а выходит т первых элементов И соединены с соответствующими Q BxoaBMH первого элемента ИЛИ, выход которого подключен к первым входам) вторых элементов И, 3 744 выходы которых соединены с соответствующими k входами выходного регистра„а вторые входы подключены к соответствующим k первым выходам счетчика, вторые выходы которого соединены с соответствующими g входами преобразователя кода в напряжение, блок управления, выходы с первого по третий которого соединены соответственно с управляющим входом счетчика, установочными входами счетчика и выходного регистра и управляющим входом коммутатора, дополнительно введены ITI третьих элементов И, гп групп переключателей, второй элемент ИЛИ, сумматор и триггер, нулевой вход которого соединен с выходом первого элемента ИЛИ, единичный вход подключен к четвертому выходу блока управления, а единичный выход триггера соединен с первыми входами rn третьих элементов И, вторые входы которых соединены с соответствующими выходами

Коммутатора каналов, третьи входы подключены к первому выходу блока управления, а выходы через соответствук цие гП группы переклкчателей соединены с соответствующими m входами второго элемента ИЛИ, выходы которого соединены с соответствующими входами сумматора, уп равляющий вход которого соединен с пятым выходом блока управления. зо

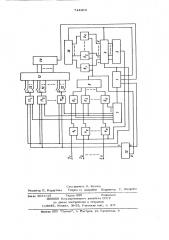

На чертеже приведена структурная электрическая схема предлагаемого преобразов ателя, Преобразователь содержит бпок 1 управления, счетчик 2, преобразователь 3 кода в напряжение, и блоков 4 сравнения, шин 5 входных сигналов первых эпементов И 6, коммутатор 7 каналов, первый элемент ИЛИ 8, вторых элементов И 9, разрядный выходной регистр 10, гг тре4О тьих элементов И 11, т групп переключателей 12, второй элемент ИЛИ 13, сумматор 14, триггер 15.

Преобразователь работает следующим образом.

Перед началом измерения блок 1 управления приводит в нулевое состояние счетчик 2 и выходной регистр 10, в единичное состояние триггер 15, в сумматор

14 заносится постоянная величина а, урав-, 50 нения регрессии, на п1 переключателях 12 устанавлив аются соответствующие значения величины коэффициентов b уравнения регре ссии.

При преобразовании входного сигнала

-го канала счетные импульсы от блока 1 управления последовательно поступают на вход счетчика 2 и одновременно кажлый

969 4 из них, проходя через элемент И 11, перелает через элемент ИЛИ 13 значение -го коэффициента Ь; управления регрессии, набранное на I -й группе переключателей 12, на вход сумматора 14. Таким образом, в зависимости от того, сколько счетных импульсов пройдет через элемент И 11, столько же раз соответствующий коэффициент b; спожится сам с собой в сумматоре 14, Прохождение упомянутых счетных импульсов в -й элемент И 11 прекрмцается в момент равенства линейно- ступенчатого напряжения, которое выр,"батывается на выходе преобразователя 3 кода в напряж ние, с входным сигналом I -го канала, Сравнение этих напряжений происходит в соответствующем -м блоке 4 сравнения.

В результате этого равенства на выходе блока 4 сравнения I -го канала вырабатывается импульс, который, проходя через -й алемент И 6, открытый i -м выходом коммутатора 7 каналов, и оступ ает н а нулевой вход триггера 15 и устанавливает его в нулевое состояние. Этим самым триггер 15 запирает алементы И 11. Кроме описанного выше упомянутый импульс с выхода элемента ИЛИ 8 поступает на входы алементов И 9 и передает содержимое счетчика 2, которое соответствует в этот момент времени значению измеряемого анапогового сигнала i --го канала, на выходной регистр 10. В результате завершения преобразования сигнала I -го канала в выходном регистре 10 находится цифровое значение измеряемого анапогового сигнала I -го канала, а к содержимому сумматора 14 прибавляется произведение цифрового значения преобразованного аналогового сигнала I ãñ канапэ и соответствукшего коэффициента b; уравнения ре| рессии. Перед следующим { +1}-м циклом измерения блок l управления производит гашение содержимого счетчика 2 и выходного регистра 10, а также устанавливает в единичное состояние триггер 15. Преобразование всех других входных каналов в цифровой код происходит аналогично описанному выше. Из мерение же неизмеря мого параметра завершается тогда, когда все косвенные параметры,, связанные с и характериз,лошие его изменения, будучи преобразованы, произведут через соответствующие элементы И 11 передачу соответствующих им коэффициентов уравнения регрессии, набранных заранее на соответствующих переключателях 12, через элемент ИЛИ 13 в накапливакший сумматор 14. В каждом шаге дискретизации вход!

5 7449 ных переменньм величин Х; преобразователь последовательно производит умножение цифровых значений лишь тех косвенных измеряемых величин Х;, которые связаны с искомой величиной у и характери5 зуют ее изменения, на постоянньэ коэффициенты уравнения регрессии b и накапливает получаемые последовательные прсизведен.IH B накаппивакщем сумматоре 14.

При этом полученная сумма представляет собой цифровое значение измеряемого параметра У . формула изобретения

Многоканальный преобразователь аналогкод, содержащий и блоков сравнения, первые входы которых соединены с соот ветствуюшими д шинами входного сигнала, вторые входы соединены с выходом преобразователя кода в напряжение, а выходы подключены соответственно к первым входам и первых элементов И, вторые входы которых соединены с соответствующими выходами коммутатора каналов, а выходы д первых элементов И соединены с соответствующими rl входами первого эпемента ИЛИ, выход которого подключен к первым входам k, вторых элементов И, вы-3р ходы которых соединены с соответствующими k входами выходного регистра, а вторые входы подключены к соответствующим первым выходам счетчика, вторые выходы которого соединены с соответ35 ствуюшими 4 вхопами преобразователя кода в напряжение, блок управления, вых 69 6 ды с первого по третий которого соединены соответственно с управлякшим входом счетчика, установочными входами счетчика и выходного регистра и управляющим входом коммутатора, о т л и ч а ю ш и йс я тем, что, с целью расширения функциональных возможностей, в него дополнительно введены т третих элементов И, т групп переключателей, второй элемент

ИЛИ, сумматор и триггер, нулевой вход которого соединен с выходом первого элемента ИЛИ, единичный вход подкпняен к четвертому выходу блока управления, а единичный выход триггера соединен с первыми входами rn третьих элементов И, вто.рые входы которых соединены с соответст вующими выходами коммутатора каналов, третьи BxoBbI подключены к первому выходу блока управления, а выходы через соответствукщие группы переключателей соединены с соответствующими m входами второго элемента ИЛИ, выходы которого соединены с соответствующими входами сумматора, управляющий ахоп которого соединен с пятым выходом блока управления.

И сто чник и инФО рМ ации, принятые во внимание при экспертизе

1. Смолов В. Б., Чернявский E. А. и др. Универсальные электронные преобр зователи информации. Л., М ашиностроение, 1971, с. 45-46, рис. 1.17.

2. Дроздов E. A.,Пятибратов А, П.

Автоматическое преобразование и кодирование информации. М., Советское радио, 1 96 4, с. 289 (прототип) .

74496 9

Составитель Н. Козлов

Редактор Е, Караулова Texpeä О, Андрейко Корректор Г. назарова

Заказ 3682/15 Тираж 995 Подписное

ОНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., a. 4/5

Филиал ППП "Патент", r. Ужгород, ул, Проектная, 4